# Fault-Tolerant Computer System Design ECE 60872/CS 59000

Topic 9: Validation

#### Saurabh Bagchi

ECE/CS Purdue University

ECE/CS 1 PURDUE

## Outline

- Introduction

- Validation methods

- Design phase

- Fault simulation

- Prototype phase

- HW or SW implemented fault injection

ECE/CS 2 PURDUE

### **Challenges**

- Assessing the system dependability for

- different technologies

- different computers

- different network topologies

- different communication protocols

- Validating the networked system characteristics

- dependability: (i) user level, (ii) system level, and (iii) network level

- availability validation: (i) detection and (ii) recovery

ECE/CS 3 PURDUE

## Experimental Analysis Different Design Phases

#### **Early Design Phase**

#### Approach and Goals:

- CAD environments used to evaluate design via simulation

- Simulated fault injection experiments

- Evaluate effectiveness of fault-tolerant mechanisms

- Provide timely feedback to system designers

#### Information produced

fault models, error latency, error detection coverage, recovery time distribution

#### Limitation:

Simulations need accurate inputs and validation of results

#### **Prototype Phase**

#### Approach and Goals:

- System run under controlled workload conditions

- Controlled fault injections used to evaluate system in presents of faults

#### Information produced

error latency, propagation detection distributions, availability

#### Limitation:

Injected faults should create/induce failure scenarios representative of actual system operation

#### **Operational Phase**

#### Approach and Goal:

- Measurement-based approach to study naturally occurring errors

- Study systems in the field, under real workloads

- Analyze collected error and performance data

- Provide information on actual failure characteristics

#### Information produced

actual failure characteristics, failure rates, time to failure distribution

#### Limitation:

Reported errors are representative of the systems studied

## **Evaluation - Experimental Methods**

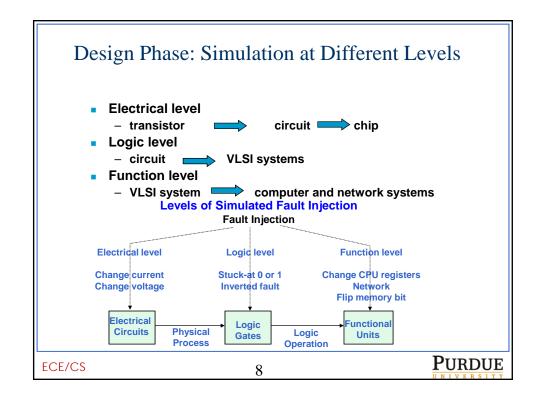

- Design phase

- Fault simulation (simulated fault injection)

- Electrical, logic, or functional level

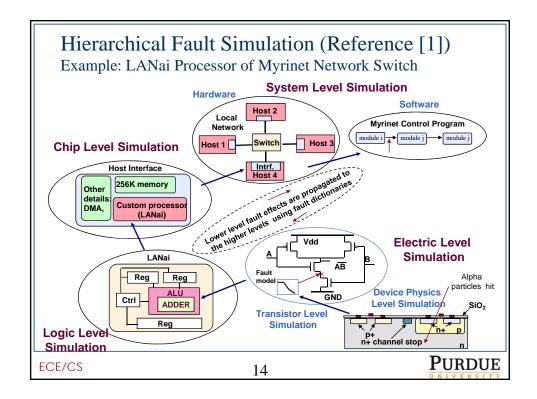

- Hierarchical simulation

- Issues: simulation time, level of simulation, fault conditions, accurate fault models

- Prototype phase

- Fault injection in prototype systems

- Hardware fault injection

- Software fault injection

- Radiation-based fault injection

- Issues: Fault models, joint HW /SW fault injection, injection into networked applications

- Operational phase

- Study of naturally occurring faults in real environments

- Essential for believable analysis of today's complex systems

- What can we say about future systems based on measurements from current systems

- Issues: HW/SW instrumentation, analysis tools

ECE/CS

## Key Issues in Fault Injection

- Effective fault injection mechanisms using hardware, software, and hybrid technology to accurately assess and validate networked systems

- Practical evaluation methods to accurately quantify fault effect and recovery mechanisms in complex environments

- Evaluation of error detection, diagnosis, and recovery techniques

- Quantification of confidence in the fault-injection based validation

- Usable fault tolerance benchmark for assessing systems and networks

6

Common evaluation/validation framework

### Metrics of Fault Injection

- Fault activation refers to the activation or access of injected faults.

- For example, fault injected into a register is activated when that register is read before the register is overwritten.

- Fault activation level refers to the ratio of the number of activated faults  $(F_a)$  to the total number of injected faults  $(F_i)$ . Therefore, fault activation level =  $F_a/F_i$

- Metrics for a fault tolerant technique

- Accuracy/Recall = (Number of activated faults that were dealt with)/(Total number of activated faults)

- Precision = (Number of cases out of the denominator that were actual activated faults)/(Number of cases that were dealt with by the fault-tolerant technique)

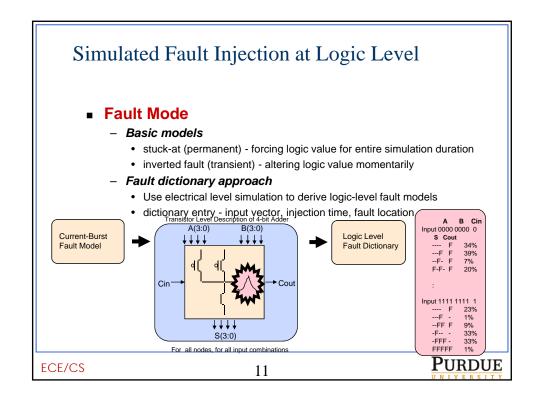

## Questions to Ask In Simulated Fault Injection

- In simulation-based fault injection, the whole system behavior is modeled and faults are injected to the simulated model of the systems

- This technique is often applied in the design phases to allow test and validation of error handling techniques before a physical prototype is available

- Fault models

- Fault conditions, fault types, number of faults, fault times, fault locations

- Workload

- Real applications, benchmarks, synthetic programs

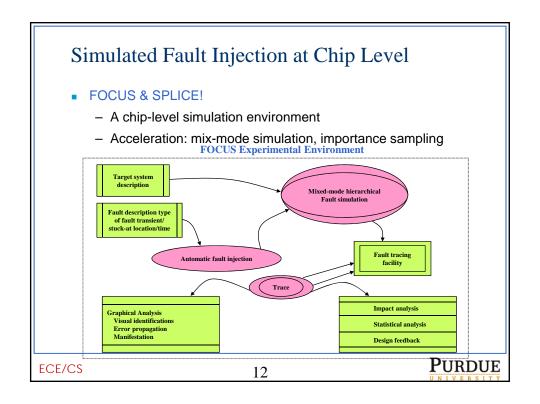

- Simulation time explosion

- Mix-mode simulation, importance sampling, concurrent simulation, accelerated fault simulation, hierarchical simulation

ECE/CS 9 PURDUE

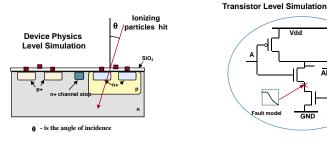

## Simulated Fault Injection at Electrical Level

Why is it needed?

ECE/CS

- Study the impact of physical causes

- Simple stuck-at models do not represent many real types of faults

10 PURDUE

### Simulated Fault Injection at Function Level

- Diversity of Components

- Object-oriented approach

- Fault Models

- Various types depending on the type of components

- Examples

- Single bit-flip for a memory or register fault

- · Message corruption for communication channel fault

- · Service interrupt for a node fault

- More detailed fault models derived from lower-level simulation

- Impact of Software

- Impact of faults is application dependent

- Software effect can be studied at this level

ECE/CS 13 PURDUE

## Prototype Phase: Software Implemented Fault Injection

- Advantages: flexibility, low cost

- Disadvantages: perturbation to workload, low time resolution

#### Targets for software fault injection

- Software faults and errors

- modify the text/data segment of the program

- Memory faults

- flip memory bits

- CPU faults

- modify CPU registers, cache, buffers

- Bus faults

- use traps before and after an instruction to change the code or data used by the instruction and then restore them after the instruction is executed

- Network faults

- modify or delete transmitted messages

- introduce faults in network controllers, drivers, buffers

ECE/CS 15

**PURDUE**

#### Characteristics of SWIFI

Table 1: Characteristics of Software Fault Injection Techniques

| L | Softw        | ware Fault Injection Hierarchy       |                            | Main Property                                                                                                 | Fault Type             | Advantage                                                                                                 | Disadvantage                                                                                                |

|---|--------------|--------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

|   | Compile-Time | Software<br>Mutation                 | Source<br>Code<br>Mutation | A modified version of<br>high-level source code is<br>loaded to emulate<br>common practical fault<br>patterns | Mutation               | More close to emulate<br>real software<br>mistakes/bugs;<br>Suitable to emulate<br>permanent faults.      | Case specific. Require<br>manual intervention;<br>Hard to emulate transient<br>faults;<br>Need to recompile |

|   | Compi        |                                      | Bytecode<br>Mutation       | For JAVA; C#;<br>In bytecode level                                                                            | Bit flips,<br>Mutation | No source code needs to<br>be modified.                                                                   | Additional tools are<br>needed to transform the<br>bytecode                                                 |

|   |              | Time Trigger                         |                            | Software/hardware<br>Interrupt; Random                                                                        | Bit flips,<br>mutation | Random; Can be<br>combined with other type<br>of injections                                               | Hard to re-create the<br>faulted scenario<br>(Low reproducibility)                                          |

|   | Runtime      | Mutation                             | Interface<br>(Parameter)   | API; syscall; Parameter in; Function return value                                                             | Mutation               | Good Portability; Can be<br>implemented to be<br>automatically run.                                       | Limited area of operating systems are tested.                                                               |

|   |              |                                      | Code;<br>bytecode          | Emulation including performance faults                                                                        | Mutation               | Match faults in reality;<br>Inject to virtual machine's<br>object attribute values,<br>methods parameters | Case specific; Hard to be run automatically                                                                 |

|   |              | User-Space<br>Ptrace<br>(Breakpoint) | TRAP instruction           | Activation; Monitor,<br>Code, Register, Crash<br>latency                                                      | Bit flips              | Multiple breakpoints;<br>Automatic experiments;<br>Emulate transient/<br>permanent faults                 | Cannot monitor data<br>access; Target process<br>needs to agree to be<br>traced.                            |

|   |              |                                      | Debug<br>register          | Activation; Monitor,<br>Code, Data, Stack,<br>Register; Crash latency                                         | Bit flips              | Inject to code/data/stack<br>parts; Automatic<br>experiments; Emulate<br>transient/ permanent<br>faults   | Not all kernels support<br>debug register access in<br>Ptrace.                                              |

## Characteristics of SWIFI (Continued)

|            |                              | Kernel                                          | Activation; Monitor;<br>Code, Data, Stack,<br>Register; Crash latency                               | Bit flips              | Use Debugging and<br>Performance features;<br>Automation; Emulate<br>transient/permanent<br>faults                                 | Need to have knowledge<br>of kernel                                                                                 |

|------------|------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Runtime    | Kernel-Space<br>(Breakpoint) | User<br>Virtual<br>Address                      | Virtual address injection;<br>Activation; Monitor;<br>Code, Data, Stack,<br>Register; Crash latency | Bit flips              | No need to use Ptrace;<br>Minimum inference to<br>applications; Automatic<br>experiments; Emulate<br>transient/permanent<br>faults | Need to use additional<br>code to differentiate<br>overlapped virtual address<br>space for different<br>processes   |

| Rui        | FPGA                         | Configurat<br>ion bit file<br>Code<br>Mutations | Dynamic Reconfigurable FPGA;                                                                        | Bit flips              | Runtime directly injects<br>to FPGA; Evaluate<br>hardware prototypes                                                               | Hard to monitor behavior<br>after injections; Need to<br>have knowledge of<br>FPGA; Need to re-<br>compute checksum |

|            | Security Threat              |                                                 | Penetration Testing                                                                                 | Mutation,<br>Bit flips | Fast and cheap, effective                                                                                                          | Front impact testing, inefficient                                                                                   |

| Simulation | Simulation-relat             | ted                                             | Processor level;<br>Combinational logic;<br>Flip-flops                                              | Bit flips              | Easy to monitor system<br>behavior in presence of<br>faults;                                                                       | Results are based on the design of simulator,                                                                       |

ECE/CS 17

## Difficulties in using SWIFI Tools

- Often fault injection is needed to answer the following questions

- Comparative studies is my app more reliable on Android or iOS?

- Dependability benchmarking rank the various flavors of Linux by their reliability

- System-level evaluation of large systems comprising heterogeneous components

- Special-purpose embedded systems which have resource constraints

- To answer these questions, the SWIFI tool needs to be ported to different platforms

- Porting effort is high

**PURDUE**

#### NFTAPE (Reference [3])

# NFTAPE is a tool for conducting automated fault/error injection-based dependability characterization

- Tool, which enables a user: (1) to specify a fault/error injection plan, (2) to carry on injection experiments, and (3) to collect the experimental results for analysis.

- Facilitates <u>automated</u> execution of fault/error injection experiments.

- Targets assessment of a broad set of dependability metrics, e.g., availability, reliability, coverage, mean time to failure.

- Operates in a distributed environment.

- Imposes minimal disturbance of target systems

ECE/CS 19

## PURDUE

#### NFTAPE Approach to Fault/Error Injection

- Lightweight Fault/Error Injectors (LWFIs)

- Small (in terms of a code size) entities responsible for injecting faults/errors

- Rely on other processes for services such as fault triggering, data logging, etc.

- Example LWFIs: driver-based, target-specific

- API for implementing and invoking Triggers, LWFIs, and support programs

20

- Less work to create components necessary for conducting fault/error injection experiments

- Components conform to standard interface

- Components can be reconfigured using the standard interface (e.g., swap triggers)

- Reusability

- LWFIs and triggers collected in a library

- Same configuration, startup, and logging process for different fault/error injection campaigns

- One learning curve

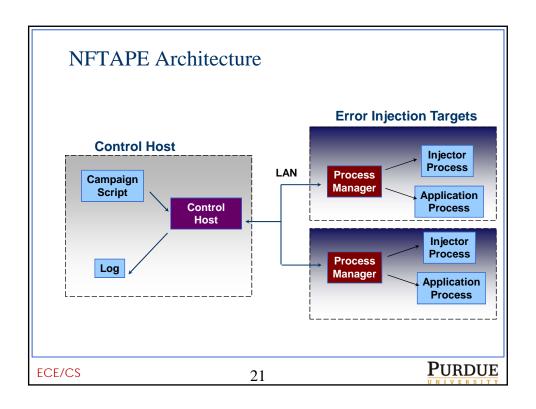

## Control Host & Process Manager

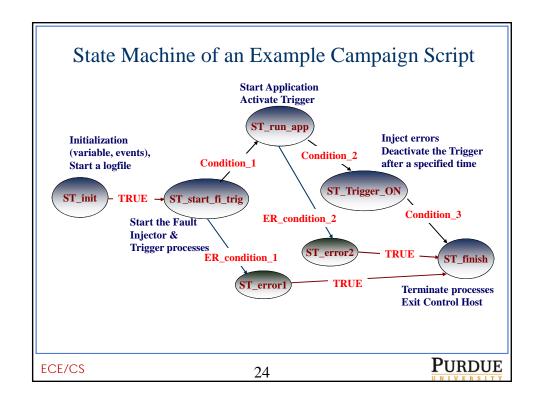

- Control Host

- Processes a Campaign Script, a file that specifies a state machine or control flow followed by the control host during the fault injection campaign

- Simple yet general way to customize a fault injection experiment

- Experiments controlled by the Common Control Mechanism

- Implemented in Java to ensure portability

- Process Manager

- Daemon on each target node to manage processes on the target node(s) including process execution and termination

- processes include: injectors, workloads, applications, monitors

- all processes are treated the same as an abstract process object rather than a process of some specific type

- Facilitates communication between the Control Host and Target Nodes.

## Fault Injectors - examples

- Driver-based injector uses dedicated device driver to inject memory, registers, OS functions, I/O devices (e.g., Linux, Solaris)

- Ptrace-based injector (e.g., Linux, Lynx) controlled injection to the target process memory and registers;

- Proc file based injector (e.g., Solaris) controlled injection to the memory image of a process

- Network injector employs dedicated software for controlling network hardware to inject faults into network cards/controllers; can intercept and corrupt messages

- Use of performance monitors (built into the CPU) to trigger fault injection

- Injection of delay faults/errors controlled, temporary suspending of interrupts

ECE/CS 23 PURDUE

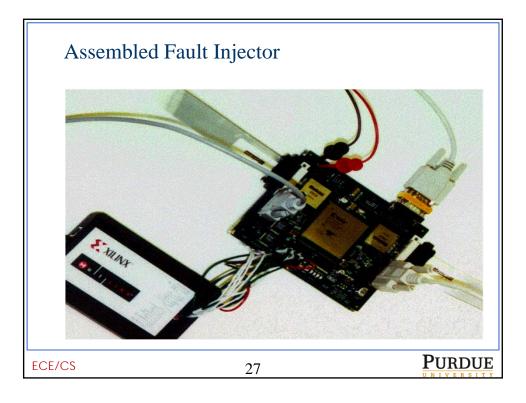

## Hardware Fault Injector for Inducing Network Faults

- A versatile device for supporting injection of random and specific faults in a network environment.

- Design based on FPGA as the core structural component, which allows the device to be programmed to:

- accept configuration commands generated either internally (i.e., by the device itself) or by an external system

- provide other services e.g., data monitoring, statistics gathering, or prototyping new designs

- Design enables precise synchronization of fault injection hardware with target systems – Myrinet network and Fiber Channel - while running at-speed of the network

- Fault injector inserted in the data path (i.e., in the network) to decode the data patterns, modify the data if necessary (i.e., inject faults), and then retransmit the data (i.e., send the corrupted/modified data to the network).

ECE/CS 25

PURDUE

**PURDUE**

## Capabilities of HW Fault Injection Techniques Summary

| Injection method                                                                                                               | Synchroni<br>zation with<br>the system<br>activity | Injection at the system speed                                                                         | Targeting faults to specific locations | Guarantees of fault activation | Example tools and references                                       |

|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------|--------------------------------------------------------------------|

| Pin-level at the signal level; not signal partitioning                                                                         | Speculative                                        | Yes                                                                                                   | Yes                                    | Low speed                      | Messaline [Arl89],<br>Hybrid (signal-<br>level & SWIFI)<br>[Kan95] |

| Pin-level by signal<br>interception; Signal<br>partition by inserting<br>the injection logic<br>into the path of the<br>signal | Full                                               | Yes<br>(if the delay induced<br>by the inserted logic<br>does not exceed that<br>allow by the system) | Yes                                    | Yes                            | Messaline [Arl89],<br>Rifle[Mad94]                                 |

| Heavy Ion Radiation                                                                                                            | Speculative                                        | Yes                                                                                                   | No                                     | No                             | [Kar94]                                                            |

| Power supply disturbances                                                                                                      | Speculative                                        | Yes                                                                                                   | No                                     | No                             | [Mir95]                                                            |

| Electromagnetic interferences                                                                                                  | Speculative                                        | Yes                                                                                                   | No                                     | No                             | [Kar97]                                                            |

| Laser (LFI)                                                                                                                    | Speculative                                        | Yes                                                                                                   | Yes                                    | No                             | [Sam97]                                                            |

| Built-in logic                                                                                                                 | Full                                               | No                                                                                                    | Yes                                    | Yes                            | FIMBUL [Fol98]]                                                    |

ECE/CS 26

13

#### Conclusion

- Fault injection is a means to effectively test and stress fault tolerance mechanisms before they are deployed in the field on an actual system

- Fault injection can be done through hardware or software

- Software-implemented fault injection (SWIFI) is the dominant mode of system verification, especially for complex software systems

- It is common to compare multiple systems (or versions of the same system) using dependability attributes collected from a fault injection campaign

ECE/CS 28 PURDUE

#### References

- 1. Stott, D. T., Ries, G., Hsueh, M. C., & Iyer, R. K. (1998). Dependability analysis of a high-speed network using software-implemented fault injection and simulated fault injection. Computers, IEEE Transactions on, 47(1), 108-119.

- 2. Z. Kalbarczyk, R. K. Iyer, G.L. Ries, J.U. Patel, M.S. Lee, and Y. Xiao "Hierarchical Simulation Approach to Accurate Fault Modeling for System Dependability Evaluation", IEEE Transactions on Software Engineering, vol. 25, no.5, September/October 1999, pp.619-632.

- 3. Stott, D.T.; Floering, B.; Burke, D.; Kalbarczpk, Z.; Iyer, R.K., "NFTAPE: a framework for assessing dependability in distributed systems with lightweight fault injectors," Computer Performance and Dependability Symposium, 2000. IPDS 2000. Proceedings. IEEE International, vol., no., pp.91-100, 2000

ECE/CS 29 PURDUE