# 10. Configuring Cyclone III Devices

CIII51010-2.1

## Introduction

Cyclone® III devices use SRAM cells to store configuration data. Because SRAM memory is volatile, configuration data must be downloaded to Cyclone III devices each time the device powers up.

Depending on device densities or package options, Cyclone III devices can be configured using one of five configuration schemes:

- Active serial (AS)

- Active parallel (AP)

- Passive serial (PS)

- Fast passive parallel (FPP)

- Joint Test Action Group (JTAG)

AS and AP schemes use an external flash memory, such as a serial configuration device or a supported flash memory, respectively. PS, FPP, and JTAG schemes use either an external controller (for example, a MAX® II device or microprocessor), or a download cable. When used in a multi-device configuration scheme for PS and FPP, the external controller for the slave Cyclone III device is a master Cyclone III device set in the AS and AP modes, respectively (for more information, refer to the "Configuration Features").

In some applications, it may be necessary for a device to wake up very quickly to begin operation. Cyclone III devices offer the Fast-On feature for fast power-on reset (POR) time to support fast wake-up time applications such as those used in the automotive market. Cyclone III devices support a new configuration scheme, such as the AP scheme, which uses commodity parallel flash as configuration memory without the need for an external host. This lowers system costs and offers fast configuration time. Additionally, Cyclone III devices can receive a compressed configuration bitstream and decompress the data in real-time, reducing storage requirements and configuration time. Furthermore, Cyclone III devices support remote system upgrade in active configuration modes. Remote system upgrades help deliver feature enhancements and bug fixes without costly recalls, reduce time-to-market, and extend product life.

This chapter explains Cyclone III device configuration features and describes how to configure Cyclone III devices using supported configuration schemes. This chapter also includes configuration pin descriptions and Cyclone III device configuration file formats. In this chapter, the generic term "device" includes all Cyclone III devices.

This chapter contains the following sections:

- "Configuration Features"

- "Configuration Requirements"

- "Active Serial Configuration (Serial Configuration Devices)"

- "Active Parallel Configuration (Supported Flash Memories)"

- "Passive Serial Configuration"

- "Fast Passive Parallel Configuration"

- "JTAG Configuration"

- "Cyclone III JTAG Instructions"

- "Device Configuration Pins"

## **Configuration Devices**

Altera® serial configuration devices (EPCS128, EPCS64, EPCS16, and EPCS4) are used in the AS configuration scheme for Cyclone III devices. Serial configuration devices offer a low-cost, low-pin count configuration solution.

For information about serial configuration devices, refer to the *Serial Configuration Devices* (*EPCS1*, *EPCS4*, *EPCS16*, *EPCS64*, and *EPCS128*) Data Sheet chapter in volume 2 of the *Configuration Handbook*.

In the AP configuration scheme, the commodity parallel flash is used as configuration memory (for information about the supported families for the commodity parallel flash, refer to Table 10–10).

## **Configuration Schemes**

A configuration scheme with different configuration voltage standards is selected by driving the Cyclone III device's MSEL pins either high or low as shown in Table 10–1. The MSEL pins are powered by the  $V_{\text{CCINT}}$  power supply of the bank in which they reside. The MSEL [3 . . 0] pins have 9-k $\Omega$  internal pull-down resistors that are always active.

To avoid problems in detecting an incorrect configuration scheme, hardwire the MSEL pins to  $V_{\text{CCA}}$  or GND without pull-up or pull-down resistors. Do not drive the MSEL pins with a microprocessor or another device.

**Table 10–1.** Cyclone III Configuration Schemes (*Note 13*) (Part 1 of 2)

| Configuration Scheme                                   | MSEL3 (10) | MSEL2 | MSEL1 | MSELO | Configuration<br>Voltage<br>Standard <i>(9)</i> |

|--------------------------------------------------------|------------|-------|-------|-------|-------------------------------------------------|

| Passive Serial Standard (PS Standard POR) (6)          | 0          | 0     | 0     | 0     | 3.3/3.0/2.5 V<br>(11)                           |

| Active Serial Standard (AS Standard POR) (1), (5), (6) | 0          | 0     | 1     | 0     | 3.3 V (11)                                      |

| Active Serial Standard (AS Standard POR) (1), (5), (6) | 0          | 0     | 1     | 1     | 3.0/2.5 V (11)                                  |

| Active Serial Fast (AS Fast POR) (1), (5), (6), (12)   | 0          | 1     | 0     | 0     | 3.0/2.5 V (11)                                  |

| Active Parallel ×16 Fast (AP Fast POR) (1), (2), (3)   | 0          | 1     | 0     | 1     | 3.3 V (11)                                      |

| Active Parallel ×16 Fast (AP Fast POR) (1), (2), (3)   | 0          | 1     | 1     | 0     | 1.8 V                                           |

| Active Parallel ×16 (AP Standard POR) (1), (2), (3)    | 0          | 1     | 1     | 1     | 3.3 V (11)                                      |

| Active Parallel ×16 (AP Standard POR) (1), (2), (3)    | 1          | 0     | 0     | 0     | 1.8 V                                           |

| Active Parallel ×16 (AP Standard POR) (1), (2), (3)    | 1          | 0     | 1     | 1     | 3.0/2.5 V <i>(11)</i>                           |

**Table 10–1.** Cyclone III Configuration Schemes (Note 13) (Part 2 of 2)

| Configuration Scheme                           | MSEL3 (10) | MSEL2 | MSEL1 | MSELO | Configuration<br>Voltage<br>Standard <i>(9)</i> |

|------------------------------------------------|------------|-------|-------|-------|-------------------------------------------------|

| Passive Serial Fast (PS Fast POR) (6)          | 1          | 1     | 0     | 0     | 3.3/3.0/2.5 V<br>(11)                           |

| Active Serial Fast (AS Fast POR) (1), (5), (6) | 1          | 1     | 0     | 1     | 3.3 V (11)                                      |

| Fast Passive Parallel Fast (FPP Fast POR) (4)  | 1          | 1     | 1     | 0     | 3.3/3.0/2.5 V<br>(11)                           |

| Fast Passive Parallel Fast (FPP Fast POR) (4)  | 1          | 1     | 1     | 1     | 1.8/1.5 V                                       |

| JTAG-based configuration (8)                   | (7)        | (7)   | (7)   | (7)   | _                                               |

#### Notes to Table 10-1:

- (1) These schemes support the remote system upgrade feature. Remote update mode is supported when using the remote system upgrade feature. You can enable or disable remote update mode with an option setting in the Quartus® II software. For more information about the remote system upgrade feature, refer to the Remote System Upgrade with Cyclone III Devices chapter in volume 1 of the Cyclone III Device Handbook.

- (2) Some of the smaller Cyclone III devices or package options do not support the AP configuration scheme (for more information, refer to Table 10–2).

- (3) In the AP configuration scheme, the commodity parallel flash is used as configuration memory (for information about the supported families for the commodity parallel flash, refer to Table 10–10).

- (4) Some of the smaller Cyclone III devices or package options do not support the FPP configuration scheme (for more information, refer to Table 10–2).

- (5) EPCS16, EPCS64, and EPCS128 support up to 40 MHz DCLK and are supported in Cyclone III devices. Existing batches of EPCS4 manufactured on 0.15 μ process geometry support up to 40 MHz DCLK and are supported in Cyclone III devices. However, batches of EPCS4 manufactured on 0.18 μ process geometry do not support AS configuration in Cyclone III devices. For information about product traceability and transition date to differentiate between supported and non-supported EPCS4 serial configuration devices, refer to PCN 0514 Manufacturing Changes on EPCS Family. For more information about serial configuration devices, refer to the Serial Configuration Devices (EPCS1, EPCS4, EPCS16, EPCS64, and EPCS128) Data Sheet chapter in volume 2 of the Configuration Handbook

- (6) These schemes support data decompression.

- (7) Do not leave the MSEL pins floating. Connect them to V<sub>CCA</sub> or GND. These pins support the non-JTAG configuration scheme used in production. If you only use JTAG configuration connect the MSEL pins to GND.

- (8) JTAG-based configuration takes precedence over other configuration schemes, which means MSEL pin settings are ignored.

- (9) Configuration voltage standard is applied to the  $V_{\text{CCIO}}$  supply of the bank in which the configuration pins reside.

- (10) Some of the smaller Cyclone III devices or package options do not support the AP configuration scheme and do not have the MSEL [3] pin (for more information about the supported configuration schemes across device densities and package options, refer to Table 10–2).

- (11) You must follow specific requirements when interfacing Cyclone III devices with 2.5-, 3.0-, and 3.3-V configuration voltage standards (for information about the requirements, refer to "Configuration and JTAG Pin I/O Requirements").

- (12) AS Fast POR with 2.5-, and 3.0-V configuration voltage standard is not available for devices that do not have the MSEL [3] pin (for devices that support AS Fast POR, refer Table 10–2).

- (13) Connect the MSEL pins to  $V_{\text{CCA}}$  or GND depending on the MSEL pin settings.

In Cyclone III devices, supported configuration schemes differ for different device densities and package options.

Table 10–2 shows the supported configuration schemes across device densities and package options.

**Table 10–2.** Cyclone III Devices Supported Configuration Schemes Across Device Densities and Package Options (Note 1)

|         |                     | Package Options (4)         |                             |                             |                                 |                                 |                                         |                                    |                                 |

|---------|---------------------|-----------------------------|-----------------------------|-----------------------------|---------------------------------|---------------------------------|-----------------------------------------|------------------------------------|---------------------------------|

| Device  | E144                | M164                        | Q240                        | F256                        | F324                            | F484                            | F780                                    | U256                               | U484                            |

| EP3C5   | AS, PS,<br>JTAG (2) | AS, PS,<br>FPP, JTAG<br>(2) | _                           | AS, PS,<br>FPP, JTAG<br>(2) | _                               | _                               | _                                       | AS, PS,<br>FPP, JTAG<br>(2)        | _                               |

| EP3C10  | AS, PS,<br>JTAG (2) | AS, PS,<br>FPP, JTAG<br>(2) | _                           | AS, PS,<br>FPP, JTAG<br>(2) | _                               | _                               | _                                       | AS, PS,<br>FPP, JTAG<br>(2)        | _                               |

| EP3C16  | AS, PS,<br>JTAG (2) | AS, PS,<br>FPP, JTAG<br>(2) | AS, PS,<br>FPP, JTAG<br>(2) | AS, PS,<br>FPP, JTAG<br>(2) | _                               | AS, PS,<br>FPP, AP,<br>JTAG (3) | _                                       | AS, PS,<br>FPP, JTAG<br><i>(2)</i> | AS, PS,<br>FPP, AP,<br>JTAG (3) |

| EP3C25  | AS, PS,<br>JTAG (2) | _                           | AS, PS,<br>FPP, JTAG<br>(2) | AS, PS,<br>FPP, JTAG<br>(2) | AS, PS,<br>FPP, AP,<br>JTAG (3) | _                               | _                                       | AS, PS,<br>FPP, JTAG<br>(2)        | _                               |

| EP3C40  | _                   | _                           | AS, PS,<br>FPP, JTAG<br>(2) | _                           | AS, PS,<br>FPP, AP,<br>JTAG (3) | AS, PS,<br>FPP, AP,<br>JTAG (3) | AS, PS,<br>FPP, AP,<br>JTAG (3),<br>(5) | _                                  | AS, PS,<br>FPP, AP,<br>JTAG (3) |

| EP3C55  | _                   | _                           | _                           | _                           | _                               | AS, PS,<br>FPP, AP,<br>JTAG (3) | AS, PS,<br>FPP, AP,<br>JTAG (3)         | _                                  | AS, PS,<br>FPP, AP,<br>JTAG (3) |

| EP3C80  | _                   | _                           | _                           | _                           | _                               | AS, PS,<br>FPP, AP,<br>JTAG (3) | AS, PS,<br>FPP, AP,<br>JTAG (3)         | _                                  | AS, PS,<br>FPP, AP,<br>JTAG (3) |

| EP3C120 | _                   | _                           | _                           | _                           | _                               | AS, PS,<br>FPP, AP,<br>JTAG (3) | AS, PS,<br>FPP, AP,<br>JTAG (3)         | _                                  | _                               |

#### Notes to Table 10-2:

- (1) AS is active serial, PS is passive serial, FPP is fast passive parallel, and AP is active parallel.

- (2) These packages do not support AP configuration scheme and AS Fast POR with 2.5-, and 3.0-V configuration voltage standard. These packages do not have the MSEL [3] pin.

- (3) These packages support all the configuration schemes shown in Table 10–10.

- (4) For more information about vertical package migration and package options for Cyclone III devices, refer to the Cyclone III Device Family Overview chapter and the Package Information for Cyclone III Devices chapter in volume 1 of the Cyclone III Device Handbook.

- (5) The EP3C40 package option F780 only partially supports vertical package migration to other F780 package options.

For more information about vertical package migration and package options for Cyclone III devices, refer to the *Cyclone III Device Family Overview* chapter and the *Package Information for Cyclone III Devices* chapter in volume 1 the *Cyclone III Device Handbook*.

Cyclone III devices offer decompression and remote system upgrade features. Cyclone III devices can receive a compressed configuration bitstream and decompress this data in real-time, thus reducing storage requirements and configuration time. Data decompression is supported in AS and PS configuration schemes. You can make real-time system upgrades from remote locations of your Cyclone III designs with the remote system upgrade mode feature. Remote update is supported in AS and AP configuration schemes.

## **Configuration File Format**

Table 10–3 shows the approximate uncompressed configuration file sizes for Cyclone III devices. To calculate the amount of storage space required for multiple device configurations, add the file size of each device together.

| Table 10-3. | Cyclone III Uncompressed Raw | Binary File Sizes | (Note 1) |

|-------------|------------------------------|-------------------|----------|

|             |                              |                   |          |

| Device  | Data Size (Mbits) |

|---------|-------------------|

| EP3C5   | 3.0               |

| EP3C10  | 3.0               |

| EP3C16  | 4.1               |

| EP3C25  | 5.8               |

| EP3C40  | 9.6               |

| EP3C55  | 14.9              |

| EP3C80  | 20.0              |

| EP3C120 | 28.6              |

## Note to Table 10-3:

(1) Raw Binary File (.rbf)

Use the data in Table 10–3 only to estimate the file size before design compilation. Different configuration file formats, such as a Hexadecimal (.hex) or Tabular Text File (.ttf) formats, have different file sizes. However, for any specific version of the Quartus II software, any design targeted for the same device has the same uncompressed configuration file size. If you are using compression, the file size can vary after each compilation because the compression ratio is dependent on the design.

For more information about setting device configuration options or creating configuration files, refer to the *Software Settings* section in volume 2 of the *Configuration Handbook*.

# **Configuration Features**

Cyclone III devices offer configuration data decompression to reduce configuration file storage and provide remote system upgrade to allow you to remotely update your Cyclone III designs.

Table 10–4 summarizes which configuration features you can use in each configuration scheme.

**Table 10–4.** Cyclone III Configuration Features (*Note 2*)

| Configuration Scheme                      | Configuration Method                                | Decompression | Remote<br>System<br>Upgrade <i>(2)</i> |

|-------------------------------------------|-----------------------------------------------------|---------------|----------------------------------------|

| Active Serial Fast (AS Fast POR)          | Serial Configuration Device                         | <b>✓</b>      | ✓                                      |

| Active Serial Standard (AS Standard POR)  | Serial Configuration Device                         | <b>✓</b>      | ✓                                      |

| Active Parallel ×16 Fast (AP Fast POR)    | Supported flash memory (1)                          | _             | ✓                                      |

| Active Parallel ×16 (AP Standard POR)     | Supported flash memory (1)                          | _             | ✓                                      |

| Passive Serial Fast (PS Fast POR)         | MAX II device or a Microprocessor with flash memory | ~             | <del>_</del>                           |

|                                           | Download cable                                      | <b>✓</b>      | _                                      |

| Passive Serial Standard (PS Standard POR) | MAX II device or a Microprocessor with flash memory | <b>✓</b>      | _                                      |

|                                           | Download cable                                      | ✓             | _                                      |

| Fast Passive Parallel Fast (FPP Fast POR) | MAX II device or a Microprocessor with flash memory | _             |                                        |

| JTAG-based configuration                  | MAX II device or a Microprocessor with flash memory | _             |                                        |

|                                           | Download cable                                      | _             | <del>_</del>                           |

## Notes to Table 10-4:

- (1) For more information about the supported families for the Numonyx commodity parallel flash, refer to Table 10–10.

- (2) Remote update mode is supported when using remote system upgrade feature. You can enable or disable the remote update mode with an option setting in the Quartus II software. For more information about the remote system upgrade feature, refer to the Remote System Upgrade with Cyclone III Devices chapter in volume 1 of the Cyclone III Device Handbook.

# **Configuration Data Decompression**

Cyclone III devices support configuration data decompression, which saves configuration memory space and time. This feature allows you to store compressed configuration data in configuration devices or other memory and transmit this compressed bitstream to Cyclone III devices. During configuration, Cyclone III devices decompress the bitstream in real time and programs their SRAM cells.

Preliminary data indicates that compression typically reduces configuration bitstream size by 35 to 55%.

Cyclone III devices support decompression in the AS and PS configuration schemes. Decompression is not supported in the AP configuration scheme, FPP configuration scheme, or JTAG-based configuration scheme.

In PS mode, use the Cyclone III decompression feature to reduce configuration time. You should also use the Cyclone III decompression feature during AS configuration if you need to save configuration memory space in the serial configuration device.

When you enable compression, the Quartus II software generates configuration files with compressed configuration data. This compressed file reduces the storage requirements in the configuration device or flash memory and decreases the time needed to transmit the bitstream to the Cyclone III device. The time needed by a Cyclone III device to decompress a configuration file is less than the time needed to transmit the configuration data to the device.

There two methods for enabling compression for Cyclone III bitstreams in the Quartus II software are:

- Before design compilation (via the Compiler Settings menu)

- After design compilation (via the Convert Programming Files window)

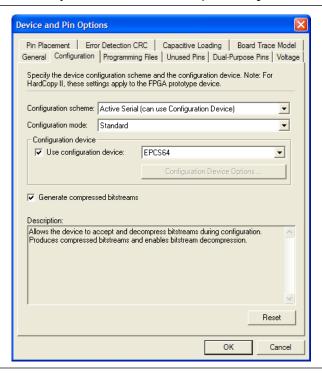

To enable compression in the project's compiler settings, perform the following steps in the Quartus II software:

- 1. On the Assignments menu, click **Device**. The **Settings** dialog box appears.

- 2. Click **Device and Pin Options**. The **Device and Pin Options** dialog box appears.

- 3. Click the **Configuration** tab.

- 4. Turn on **Generate compressed bitstreams** (Figure 10–1).

- 5. Click OK.

- 6. In the **Settings** dialog box, click **OK**.

Figure 10-1. Enabling Compression for Cyclone III Bitstreams in Compiler Settings

You can also enable compression when creating programming files from the **Convert Programming Files** window.

1. On the File menu, click **Convert Programming Files**.

- 2. Under **Output programming file**, from the drop-down menu, select your desired file type.

- 3. If you select Programmer Object File (.pof), you must specify a configuration device, directly under the file type.

- 4. In the Input files to convert box, select SOF Data.

- 5. Click **Add File** to browse to the Cyclone III device SRAM Object file (.sof) or files.

- On the Convert Programming Files window, select the .pof file you added to SOF Data and click Properties.

- 7. On the **SOF File Properties** dialog box, turn on **Compression**.

When multiple Cyclone III devices are cascaded, you can selectively enable the compression feature for each device in the chain.

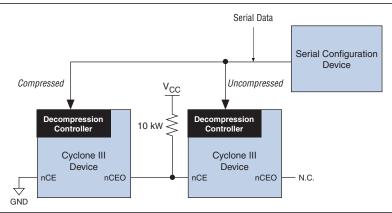

Figure 10–2 shows a chain of two Cyclone III devices. The first Cyclone III device has compression enabled and receives a compressed bitstream from the configuration device. The second Cyclone III device has the compression feature disabled and receives uncompressed data.

Figure 10–2. Compressed and Uncompressed Configuration Data in the Same Configuration File

You can generate programming files for this setup from the **Convert Programming Files** dialog box in the Quartus II software, from the File menu.

# **Remote System Upgrade**

Cyclone III devices support remote update mode when using the remote system upgrade feature. You can enable or disable remote update mode with an option setting in the Quartus II software. Remote system upgrades help deliver feature enhancements and bug fixes without costly recalls, reduce time-to-market, and extend product life.

Cyclone III devices support remote update in the AS and AP configuration schemes. You can implement remote update in conjunction with real-time decompression of configuration data if you need to save configuration memory space in the serial configuration device with the AS configuration scheme.

For more information about the remote system upgrade feature, refer to the *Remote System Upgrade with Cyclone III Devices* chapter in volume 1 of the *Cyclone III Device Handbook*.

# **Configuration Requirements**

## **Power-On Reset Circuit**

The POR circuit keeps the device in reset state until the power supply voltage levels have stabilized on power-up. Upon power-up, the device does not release nSTATUS until  $V_{\text{CCINT}}$ ,  $V_{\text{CCA}}$ , and  $V_{\text{CCIO}}$  of banks 1, 6, 7, and 8 are above the device's POR trip point. On power-up,  $V_{\text{CCINT}}$  and  $V_{\text{CCIN}}$  are monitored for brown-out conditions.

$V_{CCA}$  is the analog power to the phase-locked loop (PLL).

In Cyclone III devices, you can select between a fast POR time or standard POR time depending on the MSEL pin settings. The fast POR time is 3 ms <  $T_{\rm POR}$  < 9 ms for fast configuration time. The standard POR time is 50 ms <  $T_{\rm POR}$  < 200 ms, which has a lower power-ramp rate. In both cases, you can extend the POR time by using an external component to assert the nSTATUS pin low.

Table 10–5 shows the supported POR times for each configuration scheme.

| Table 10-5. | Cyclone III Supported Power-On Reset Times Across Configuration Schemes   | (Note 3)  |

|-------------|---------------------------------------------------------------------------|-----------|

| IUDIC IO O. | Official in Dupportou i Owor On Hosot Innos Across Conniquiation Concincs | (11010 0) |

| Configuration Scheme                      | Fast POR Time<br>(3 ms < T <sub>POR</sub> < 9 ms) | Standard POR Time<br>(50 ms < T <sub>POR</sub> < 200 ms) | Configuration<br>Voltage<br>Standard <i>(1)</i> |

|-------------------------------------------|---------------------------------------------------|----------------------------------------------------------|-------------------------------------------------|

| Passive Serial Standard (PS Standard POR) | _                                                 | ✓                                                        | 3.3/3.0/2.5 V                                   |

| Active Serial Standard (AS Standard POR)  | _                                                 | ✓                                                        | 3.3 V                                           |

| Active Serial Standard (AS Standard POR)  | _                                                 | ✓                                                        | 3.0/2.5 V                                       |

| Active Serial Fast (AS Fast POR)          | ✓                                                 | _                                                        | 3.0/2.5 V                                       |

| Active Parallel ×16 Fast (AP Fast POR)    | ✓                                                 | _                                                        | 3.3 V                                           |

| Active Parallel ×16 Fast (AP Fast POR)    | ✓                                                 | _                                                        | 1.8 V                                           |

| Active Parallel ×16 (AP Standard POR)     | _                                                 | ✓                                                        | 3.3 V                                           |

| Active Parallel ×16 (AP Standard POR)     | _                                                 | ✓                                                        | 1.8 V                                           |

| Active Parallel ×16 (AP Standard POR)     | _                                                 | ✓                                                        | 3.0/2.5 V                                       |

| Passive Serial Fast (PS Fast POR)         | ✓                                                 | _                                                        | 3.3/3.0/2.5 V                                   |

| Active Serial Fast (AS Fast POR)          | ✓                                                 | _                                                        | 3.3 V                                           |

| Fast Passive Parallel Fast (FPP Fast POR) | ✓                                                 | _                                                        | 3.3/3.0/2.5 V                                   |

| Fast Passive Parallel Fast (FPP Fast POR) | ✓                                                 | _                                                        | 1.8/1.5 V                                       |

| JTAG-based configuration                  | (2)                                               | (2)                                                      | _                                               |

## Notes to Table 10-5:

<sup>(1)</sup> Configuration voltage standard is applied to the  $V_{\text{CCIO}}$  supply of the bank in which the configuration pins reside.

<sup>(2)</sup> JTAG-based configuration takes precedence over other configuration schemes, which means MSEL pin settings are ignored. However, the POR time is dependent on the MSEL pin settings.

<sup>(3)</sup> Connect the MSEL pins to  $V_{\text{CCA}}$  or GND depending on the MSEL pin settings.

In some applications, it may be necessary for a device to wake up very quickly to begin operation. The Cyclone III device family offers the fast POR time option to support fast wake-up time applications. The fast POR time option has stricter power-up requirements compared to the standard POR time option. You can select either the fast POR option or the standard POR option using the MSEL pin settings.

The fast POR time feature in Cyclone III devices is similar to the Fast-On feature in Cyclone II devices designated with an "A" in the ordering code.

The Cyclone III devices' fast wake-up time meets the requirement of common bus standards in automotive applications, such as Media Orientated Systems Transport (MOST) and Controller Area Network (CAN).

For more information about wake-up time and POR circuit, refer to the *Hot Socketing* and *Power-On Reset* chapter in volume 1 of the *Cyclone III Device Handbook*.

## Configuration and JTAG Pin I/O Requirements

Cyclone III devices are manufactured using TSMC's 65-nm low-k dielectric process. Although Cyclone III devices use TSMC 2.5-V transistor technology in I/O buffers, the devices are compatible and able to interface with 2.5-, 3.0-, and 3.3-V configuration voltage standards. However, you must follow specific requirements when interfacing Cyclone III devices with 2.5-, 3.0-, and 3.3-V configuration voltage standards.

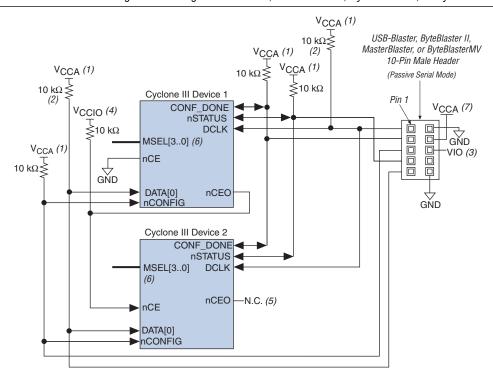

All I/O inputs must maintain a maximum AC voltage of 4.1 V. When using a serial configuration device in the AS configuration scheme, you must connect a 25- $\Omega$  series resistor at the near end of the serial configuration device for DATA [0]. When cascading Cyclone III devices in a multi-device configuration, you must connect repeater buffers between the Cyclone III master and slave device or the devices for DATA and DCLK. The output resistance of the repeater buffers must fit the maximum overshoot equation given by:

### Equation 10-1.

$$0.8Z_0 \le R_E \le 1.8Z_0$$

In this Equation 10–1,  $Z_O$  is the transmission line impedance and  $R_E$  is the equivalent resistance of the output buffer.

# **Active Serial Configuration (Serial Configuration Devices)**

In the AS configuration scheme, Cyclone III devices are configured using a serial configuration device. These configuration devices are low-cost devices with non-volatile memories that feature a simple four-pin interface and a small form factor. These features make serial configuration devices an ideal low-cost configuration solution.

For more information about serial configuration devices, refer to the *Serial Configuration Devices* (EPCS1, EPCS4, EPCS16, EPCS64, and EPCS128) Data Sheet in volume 2 of the *Configuration Handbook*.

In Cyclone III devices, the active master clock frequency runs at a maximum of 40 MHz, and typically at 30 MHz. Cyclone III devices only work with serial configuration devices that support up to 40 MHz. Existing batches of EPCS4 manufactured on 0.15  $\mu$  process geometry support AS configuration in Cyclone III devices up to 40 MHz. However, batches of EPCS4 manufactured on 0.18  $\mu$  process geometry support only up to 20 MHz. EPCS16, EPCS64, and EPCS128 are not affected.

For more information about product traceability and transition date to differentiate between 0.15  $\mu$  process geometry and 0.18  $\mu$  process geometry EPCS4 serial configuration devices, refer to PCN 0514 Manufacturing Changes on EPCS Family.

Serial configuration devices provide a serial interface to access configuration data. During device configuration, Cyclone III devices read configuration data via the serial interface, decompress data if necessary, and configures their SRAM cells. This scheme is referred to as the AS configuration scheme because the device controls the configuration interface. This scheme contrasts with the PS configuration scheme, where the external host controls the interface.

The Cyclone III decompression and remote system upgrade features are available when configuring your Cyclone III device using the AS configuration scheme.

Table 10–6 shows the MSEL pin settings when using the AS configuration scheme with different configuration voltage standards.

| Configuration Scheme                              | MSEL3<br>(5) | MSEL2 | MSEL1 | MSELO | Configuration<br>Voltage<br>Standard (3) |

|---------------------------------------------------|--------------|-------|-------|-------|------------------------------------------|

| Active Serial Standard (AS Standard POR) (1), (2) | 0            | 0     | 1     | 0     | 3.3 V (4)                                |

| Active Serial Standard (AS Standard POR) (1), (2) | 0            | 0     | 1     | 1     | 3.0/2.5 V <i>(4)</i>                     |

| Active Serial Fast (AS Fast POR) (1), (2), (6)    | 0            | 1     | 0     | 0     | 3.0/2.5 V <i>(4)</i>                     |

| Active Serial Fast (AS Fast POR) (1), (2)         | 1            | 1     | 0     | 1     | 3.3 V (4)                                |

**Table 10–6.** Cyclone III MSEL Pin Settings for AS Configuration Schemes (Note 7)

#### Notes to Table 10-6:

- (1) These schemes support the remote system upgrade feature. Remote update mode is supported when using the remote system upgrade feature. You can enable or disable remote update mode with an option setting in the Quartus II software. For more information about the remote system upgrade feature, refer to the Remote System Upgrade with Cyclone III Devices chapter in volume 1 of the Cyclone III Device Handbook.

- (2) These schemes support data decompression.

- (3) The configuration voltage standard is applied to the V<sub>CCIO</sub> supply of the bank in which the configuration pins reside.

- (4) You must follow specific requirements when interfacing Cyclone III devices with 2.5-, 3.0-, and 3.3-V configuration voltage standards (for more information about the requirements, refer to "Configuration and JTAG Pin I/O Requirements").

- (5) Some of the smaller Cyclone III devices or package options do not support the AP configuration scheme and do not have the MSEL[3] pin (for more information about the supported configuration schemes across device densities and package options, refer to Table 10–2).

- (6) AS Fast POR with a 2.5- or 3.0-V configuration voltage standard is not available for devices that do not have the MSEL [3] pin (for more information about devices that support AS Fast POR, refer to Table 10–2).

- (7) Connect the MSEL pins to  $V_{CCA}$  or GND depending on the MSEL pin settings.

## **Single-Device AS Configuration**

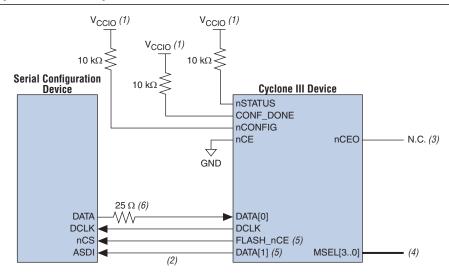

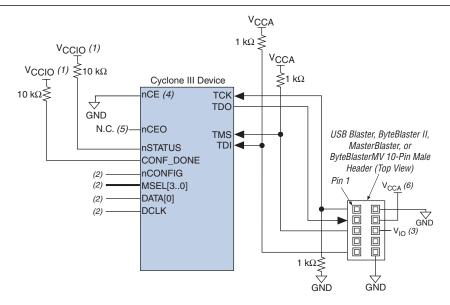

The four-pin interface of serial configuration devices consists of a serial clock input (DCLK), serial data output (DATA), AS data input (ASDI), and an active-low chip select (nCS).

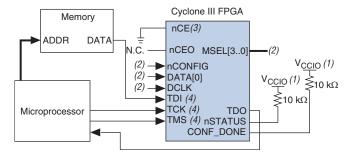

This four-pin interface connects to Cyclone III device pins, as shown in Figure 10–3.

Figure 10–3. Single-Device AS Configuration

#### Notes to Figure 10-3:

- (1) Connect the pull-up resistors to the  $V_{\text{CCIO}}$  supply of the bank in which the pin resides.

- (2) Cyclone III devices use the DATA [1] -to-ASDI path to control the configuration device.

- (3) The nceo pin can be left unconnected or used as a user I/O pin when it does not feed another device's nce pin.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect MSEL[3..0], refer to Table 10–6. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) These are dual-purpose I/O pins. The FLASH\_nCE pin functions as the nCSO pin in the AS configuration scheme. The DATA [1] pin functions as the ASDO pin in the AS configuration scheme.

- (6) Connect the series resistor at the near end of the serial configuration device.

When connecting a serial configuration device to the Cyclone III device in a single-device AS configuration, you must connect a 25- $\Omega$  series resistor at the near end of the serial configuration device for DATA [0]. The 25- $\Omega$  resistor in the series works to minimize the driver impedance mismatch with the board trace and reduce the overshoot seen at the Cyclone III DATA [0] input pin.

In a single-device AS configuration, the maximum board loading and board trace length between the supported serial configuration device and the Cyclone III device must follow the recommendations in Table 10–8.

If you use the AS configuration scheme for Cyclone III devices, the  $V_{\text{CCIO}}$  of I/O bank 1 must be 3.3, 3.0, or 2.5 V. Altera does not recommend using the level shifter between a serial configuration device and the Cyclone III device in the AS configuration scheme.

For information about electrical specification compatibility between the Cyclone III and the EPCS device at various configuration voltage levels, refer to *AN 523: Cyclone III Configuration Interface Guidelines with EPCS Devices* application note.

Upon power-up, Cyclone III devices go through a POR. POR delay depends on the MSEL pin settings, which corresponds to the configuration scheme that you selected. Depending on the configuration scheme, either a fast or standard POR time is available. The fast POR time is 3 ms <  $T_{POR}$  < 9 ms for a fast configuration time. The standard POR time is 50 ms <  $T_{POR}$  < 200 ms, which has a lower power-ramp rate. During POR, the device resets, holds nSTATUS and CONF\_DONE low, and tri-states all user I/O pins. When the device successfully exits POR, all user I/O pins continue to be tri-stated. The user I/O pins and dual-purpose I/O pins have weak pull-up resistors, which are always enabled (after POR) before and during configuration.

The value of the weak pull-up resistors on the I/O pins that are on before and during configuration can be found in the *DC* and Switching Characteristics chapter in volume 2 of the Cyclone III Device Handbook.

The three stages of the configuration cycle are reset, configuration, and initialization. When nconfig or nstatus are low, the device is in reset. After POR, the Cyclone III device releases nstatus, which is pulled high by an external 10-k $\Omega$  pull-up resistor and enters configuration mode.

To begin configuration, power  $V_{CCINT}$ ,  $V_{CCA}$ , and  $V_{CCIO}$  voltages (for the banks in which the configuration and JTAG pins reside) to the appropriate voltage levels.

The serial clock (DCLK) generated by the Cyclone III device controls the entire configuration cycle and provides timing for the serial interface. Cyclone III devices use an 40-MHz internal oscillator to generate DCLK. There is some variation in the internal oscillator frequency because of the process, voltage, and temperature conditions in Cyclone III devices. The internal oscillator is designed such that its maximum frequency is guaranteed to meet EPCS device specifications.

EPCS1 does not support Cyclone III devices because of its insufficient memory capacity.

For information about serial configuration devices, refer to the *Serial Configuration Devices* (EPCS1, EPCS4, EPCS16, EPCS64, and EPCS128) Data Sheet chapter in volume 2 of the *Configuration Handbook*.

Table 10–7 shows active serial DCLK output frequency.

**Table 10–7.** Active Serial DCLK Output Frequency

| Oscillator | Minimum | Typical | Maximum | Unit |

|------------|---------|---------|---------|------|

| 40 MHz     | 20      | 30      | 40      | MHz  |

In the AS configuration scheme, the serial configuration device latches input and control signals on the rising edge of DCLK and drives out configuration data on the falling edge. Cyclone III devices drive out control signals on the falling edge of DCLK and latch configuration data on the falling edge of DCLK.

The FLASH\_nCE and DATA[1] pins are dual-purpose I/O pins. The FLASH\_nCE pin functions as the nCSO pin in the AS configuration scheme. The DATA[1] pin functions as the ASDO pin in the AS configuration scheme.

In configuration mode, the Cyclone III device enables the serial configuration device by driving the FLASH\_nCE output pin low, which connects to the chip select (nCS) pin of the configuration device. The Cyclone III device uses the serial clock (DCLK) and serial data output (DATA[1]) pins to send operation commands and/or read address signals to the serial configuration device. The configuration device provides data on its serial data output (DATA) pin, which connects to the DATA[0] input of the Cyclone III device.

After all configuration bits are received by the Cyclone III device, it releases the open-drain CONF\_DONE pin, which is pulled high by an external  $10\text{-k}\Omega$  resistor. Initialization begins only after the CONF\_DONE signal reaches a logic-high level. All AS configuration pins (DATA [0], DCLK, FLASH\_nCE, and DATA [1]) have weak internal pull-up resistors that are always active. After configuration, these pins are set as input tri-stated and are driven high by weak internal pull-up resistors. The CONF\_DONE pin must have an external  $10\text{-k}\Omega$  pull-up resistor in order for the device to initialize.

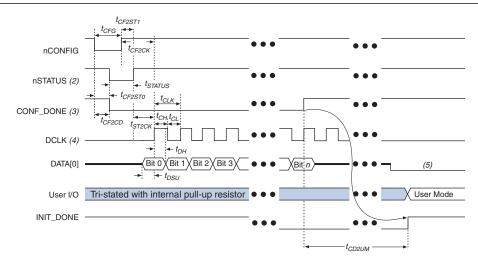

In Cyclone III devices, the initialization clock source is either the 10-MHz (typical) internal oscillator (separate from the active serial internal oscillator) or the optional CLKUSR pin. By default, the internal oscillator is the clock source for initialization. If you use the internal oscillator, the Cyclone III device provides itself with enough clock cycles for proper initialization. The advantage of using the internal oscillator is that you do not need to send additional clock cycles from an external source to the CLKUSR pin during the initialization stage. Additionally, you can use the CLKUSR pin as a user I/O pin. The timing parameters  $t_{\text{CF2CD}}$ ,  $t_{\text{CF2ST0}}$ ,  $t_{\text{CF2ST1}}$ , and  $t_{\text{CD2UM}}$  are identical to the one for PS mode which are shown in Table 10–13.

You also have the flexibility to synchronize initialization of multiple devices or to delay initialization with the CLKUSR option. Using the CLKUSR pin allows you to control when your device enters user mode. You can delay the device from entering user mode for an indefinite amount of time. Turn on the **Enable user-supplied start-up clock (CLKUSR)** option in the Quartus II software from the **General** tab of the **Device and Pin Options** dialog box. When you **enable** the **user supplied start-up clock** option, the CLKUSR pin is the initialization clock source. Supplying a clock on CLKUSR does not affect the configuration process. After all configuration data is accepted and CONF\_DONE goes high, Cyclone III devices require 3,185 clock cycles to initialize properly and enter user mode. Cyclone III devices support a CLKUSR f<sub>MAX</sub> of 133 MHz.

An optional INIT\_DONE pin is available, which signals the end of initialization and the start of user mode with a low-to-high transition. The **Enable INIT\_DONE Output** option is available in the Quartus II software from the **General** tab of the **Device and Pin Options** dialog box. If the INIT\_DONE pin is used, it will be high due to an external  $10\text{-k}\Omega$  pull-up resistor when nCONFIG is low and during the beginning of configuration. Once the option bit to enable INIT\_DONE is programmed into the device (during the first frame of configuration data), the INIT\_DONE pin goes low. When initialization is complete, the INIT\_DONE pin is released and pulled high. This low-to-high transition signals that the device has entered user mode. When initialization is complete, the device enters user mode. In user mode, the user I/O pins no longer have weak pull-up resistors and function as assigned in your design.

If an error occurs during configuration, Cyclone III devices assert the nSTATUS signal low, indicating a data frame error, and the CONF\_DONE signal stays low. If the **Auto-restart configuration after error** option (available in the Quartus II software from the **General** tab of the **Device and Pin Options** dialog box) is turned on, the Cyclone III device resets the configuration device by pulsing FLASH\_nCE, releases nSTATUS after a reset time-out period (maximum of 230 µs), and retries configuration. If this option is turned off, the system must monitor nSTATUS for errors and then pulse nCONFIG low for at least 500 ns to restart configuration.

When the Cyclone III device is in user mode, you can initiate reconfiguration by pulling the nCONFIG pin low. The nCONFIG pin needs to be low for at least 500 ns. When nCONFIG is pulled low, the Cyclone III device resets. The Cyclone III device also pulls nSTATUS and CONF\_DONE low and all I/O pins are tri-stated. When nCONFIG returns to a logic-high level and nSTATUS is released by the Cyclone III device, reconfiguration begins.

If you use the optional CLKUSR pin, and the nCONFIG pin is pulled low to restart configuration during device initialization, ensure the CLKUSR pin continues to toggle during the time nSTATUS is low (a maximum of 230  $\mu$ s).

For more information about configuration issues, refer to the *Debugging Configuration Problems* chapter in volume 2 of the *Configuration Handbook* and the FPGA Configuration Troubleshooter on the Altera website (www.altera.com).

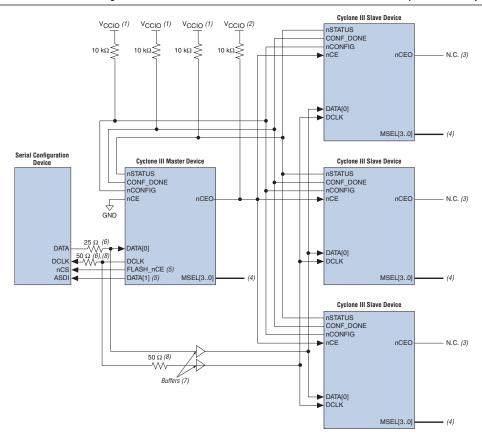

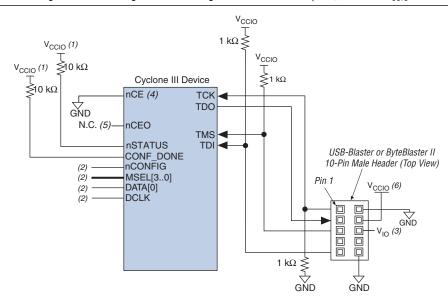

## **Multi-Device AS Configuration**

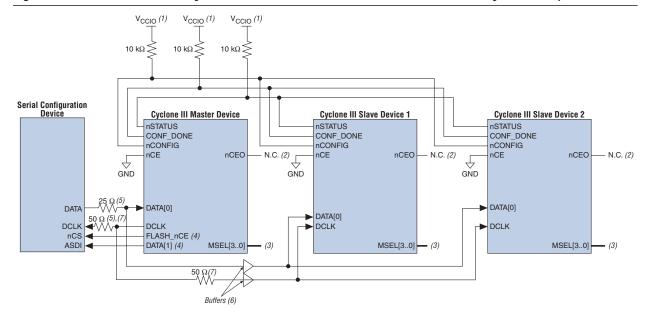

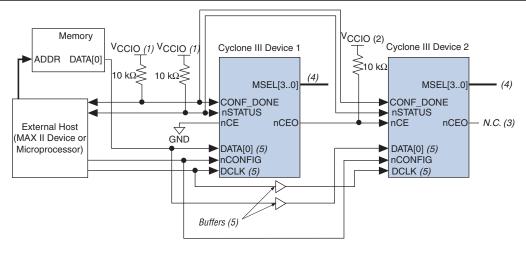

You can configure multiple Cyclone III devices using a single-serial configuration device. You can cascade multiple Cyclone III devices using the chip-enable (nCE) and chip-enable-out (nCEO) pins. The first device in the chain must have its nCE pin connected to GND. You must connect its nCEO pin to the nCE pin of the next device in the chain. Use an external  $10\text{-k}\Omega$  pull-up resistor to pull the nCEO signal high to its  $V_{\text{CCIO}}$  level to help the internal weak pull-up resistor. When the first device captures all of its configuration data from the bitstream, it drives the nCEO pin low, enabling the next device in the chain. You can leave the nCEO pin of the last device unconnected or use it as a user I/O pin after configuration if the last device in the chain is a Cyclone III device. The nCONFIG, nSTATUS, CONF\_DONE, DCLK, and DATA [0] pins of each device in the chain are connected (refer to Figure 10-4).

The first Cyclone III device in the chain is the configuration master and controls configuration of the entire chain. You must connect its MSEL pins to select the AS configuration scheme. The remaining Cyclone III devices are configuration slaves; you must connect their MSEL pins to select the PS configuration scheme. Any other Altera device that supports PS configuration can also be part of the chain as a configuration slave.

Figure 10–4 shows the pin connections for this setup.

VCCIO (1) V<sub>CCIO</sub> (1) V<sub>CCIO</sub> (1) VCCIO (2) 10 kΩ 10 kΩ  $10 k\Omega$ **Serial Configuration** Cyclone III Master Device Cyclone III Slave Device Device nSTATUS nSTATUS CONF\_DONE CONF\_DONE - N.C. (3) nCEO **nCONFIG** nCONFIG nCEO nCE nCE GND 25 Ω (6) DATA DATA[0] DATA[0] 50 Ω (6), (8) **DCLK** DCI K **DCLK** nCS FLASH nCE (5) **ASDI** DATA[1] (5) MSEL[3..0] MSEL[3..0] (4) 50 Ω (8)

Figure 10–4. Multi-Device AS Configuration

#### Notes to Figure 10-4:

- (1) Connect the pull-up resistors to the  $V_{\text{CCIO}}$  supply of the bank in which the pin resides.

- (2) Connect the pull-up resistor to the  $V_{\text{CCIO}}$  supply voltage of I/O bank in which the nCE pin resides.

- (3) You can leave the nceo pin unconnected or use it as a user I/O pin when it does not feed another device's nce pin.

Buffers (7)

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. You must set the Cyclone III master device in AS mode and the slave devices in PS mode. To connect MSEL [3..0] for the master device in AS mode, refer to Table 10–6. To connect MSEL [3..0] for the slave devices in PS mode, refer to Table 10–12. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) These are dual-purpose I/O pins. The FLASH\_nCE pin functions as the nCSO pin in the AS configuration scheme. The DATA [1] pin functions as the ASDO pin in the AS configuration scheme.

- (6) Connect the series resistor at the near end of the serial configuration device.

- (7) Connect the repeater buffers between the Cyclone III master and slave device or devices for DATA [0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements".

- (8) The 50-Ω series resistors are optional if the 3.3-V configuration voltage standard is applied. For optimal signal integrity, connect these 50-Ω series resistors if the 2.5- or 3.0-V configuration voltage standard is applied.

- When connecting a serial configuration device to the Cyclone III device in a multi-device AS configuration, you must connect a 25- $\Omega$  series resistor at the near end of the serial configuration device for DATA [0].

- In a multi-device AS configuration, the board trace length between the serial configuration device to the master Cyclone III device needs to follow the recommendations in Table 10–8. Additionally, you must connect the repeater buffers between the Cyclone III master and slave device or devices for DATA [0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements".

As shown in Figure 10–4, the nSTATUS and CONF\_DONE pins on all target devices are connected together with external pull-up resistors. These pins are open-drain bidirectional pins on the devices. When the first device asserts nCEO (after receiving all of its configuration data), it releases its CONF\_DONE pin. However, the subsequent devices in the chain keep this shared CONF\_DONE line low until they have received their configuration data. When all target devices in the chain have received their configuration data and have released CONF\_DONE, the pull-up resistor drives a high level on this line and all devices simultaneously enter initialization mode.

If an error occurs at any point during configuration, the nSTATUS line is driven low by the failing device. If you enable the **Auto-restart configuration after error** option, reconfiguration of the entire chain begins after a reset time-out period (a maximum of 230  $\mu$ s). If you turn off the **Auto-restart configuration after error** option, the external system must monitor nSTATUS for errors and then pulse nCONFIG low to restart the configuration. The external system can pulse nCONFIG if it is under system control rather than tied to  $V_{\text{CCIO}}$ .

While you can cascade Cyclone III devices, serial configuration devices cannot be cascaded or chained together.

If the configuration bitstream size exceeds the capacity of a serial configuration device, you must select a larger configuration device, enable the compression feature, or both. When configuring multiple devices, the size of the bitstream is the sum of the individual devices' configuration bitstreams.

## **Configuring Multiple Cyclone III Devices with the Same Design**

Certain designs require you to configure multiple Cyclone III devices with the same design through a configuration bitstream or a .sof file. You can do this through one of two methods, as described in this section. For both methods, serial configuration devices cannot be cascaded or chained together.

## **Multiple SRAM Object Files**

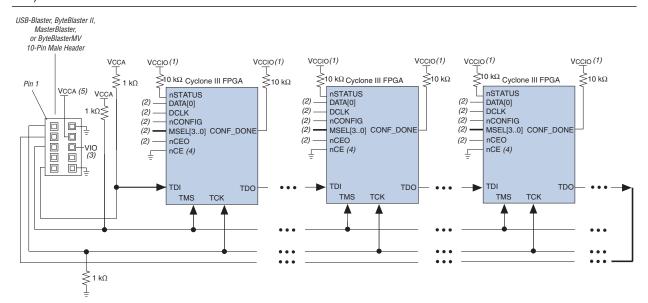

In the first method, two copies of the **.sof** files are stored in the serial configuration device. Use the first copy to configure the master Cyclone III device and the second copy to configure all remaining slave devices concurrently. All slave devices must be the same density and package. The setup is similar to Figure 10–4, in which the master is set up in active serial mode and the slave devices are set up in passive serial mode.

To configure four identical Cyclone III devices with the same .sof files, you must set up the chain similar to the example shown in Figure 10–5. The first device is the master device and its MSEL pins need to be set to select AS configuration. The other three slave devices are set up for concurrent configuration and their MSEL pins need to be set to select PS configuration. The nCEO pin from the master device drives the nCE input pins on all three slave devices. The DATA and DCLK pins connect in parallel to all four devices. During the first configuration cycle, the master device reads its configuration data from the serial configuration device while holding nCEO high. After completing its configuration cycle, the master drives nCE low and transmits the second copy of the configuration data to all three slave devices, configuring them simultaneously.

The advantage of using the setup in Figure 10–5 is that you can have a different **.sof** file for the Cyclone III master device. However, all the Cyclone III slave devices must be configured with the same **.sof** file. You can either compress or uncompress the **.sof** files in this configuration method.

You can still use this method if the master and slave Cyclone III devices use the same .sof file.

Figure 10-5. Multi-Device AS Configuration in which Devices Receive the Same Data with Multiple SRAM Object Files

### Notes to Figure 10-5:

- (1) Connect the pull-up resistors to the  $V_{CCIO}$  supply of the bank in which the pin resides.

- (2) Connect the pull-up resistor to the  $V_{CCIO}$  supply voltage of I/O bank in which the nCE pin resides.

- (3) The nceo pin can be left unconnected or used as a user I/O pin when it does not feed another device's nce pin.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. You must set the Cyclone III master device in AS mode and the slave devices in PS mode. To connect MSEL[3..0] for the master device in AS mode, refer to Table 10–6. To connect MSEL[3..0] for the slave devices in PS mode, refer to Table 10–12. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (5) These are dual-purpose I/O pins. The FLASH\_nce pin functions as the ncso pin in the AS configuration scheme. The DATA [1] pin functions as the ASDO pin in the AS configuration scheme.

- (6) Connect the series resistor at the near end of the serial configuration device.

- (7) Connect the repeater buffers between the Cyclone III master and slave device or devices for DATA[0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements".

- (8) The  $50-\Omega$  series resistors are optional if the 3.3-V configuration voltage standard is applied. For optimal signal integrity, connect these  $50-\Omega$  series resistors if the 2.5- or 3.0-V configuration voltage standard is applied.

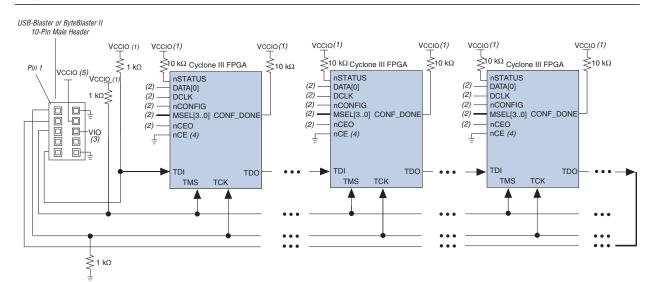

## Single SRAM Object File

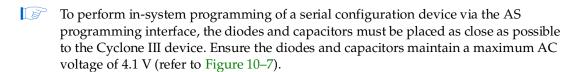

The second method configures both the master and slave Cyclone III devices with the same **.sof** file. The serial configuration device stores one copy of the **.sof** file. This setup is shown in Figure 10–6 where the master is setup in AS mode and the slave devices are setup in PS mode. You must setup one or more slave devices in the chain. All the slave devices must be setup in the same way as shown in Figure 10–6.

Figure 10-6. Multi-Device AS Configuration in which Devices Receive the Same Data with a Single SRAM Object File

### Notes to Figure 10-6:

- (1) Connect the pull-up resistors to the  $V_{CCIO}$  supply of the bank in which the pin resides.

- (2) The nceo pin can be left unconnected or used as a user I/O pin when it does not feed another device's nce pin.

- (3) The MSEL pin settings vary for different configuration voltage standards and POR time. You must set the Cyclone III master device in AS mode and the slave devices in PS mode. To connect MSEL[3..0] for the master device in AS mode, refer to Table 10–6. To connect MSEL[3..0] for the slave devices in PS mode, refer to Table 10–12. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (4) These are dual-purpose I/O pins. The FLASH\_nCE pin functions as the nCSO pin in the AS configuration scheme. The DATA [1] pin functions as the ASDO pin in the AS configuration scheme.

- (5) Connect the series resistor at the near end of the serial configuration device.

- (6) Connect the repeater buffers between the Cyclone III master and slave device or devices for DATA[0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements".

- (7) The 50-Ω series resistors are optional if the 3.3-V configuration voltage standard is applied. For optimal signal integrity, connect these 50-Ω series resistors if the 2.5- or 3.0-V configuration voltage standard is applied.

In this setup, all the Cyclone III devices in the chain are connected for concurrent configuration. This can reduce the AS configuration time because all the Cyclone III devices are configured in one configuration cycle. Connect the nCE input pins of all the Cyclone III devices to ground. You can either leave the nCEO output pins on all the Cyclone III devices unconnected or use the nCEO output pins as normal user I/O pins. The DATA and DCLK pins are connected in parallel to all the Cyclone III devices.

You need to put a buffer before the DATA and DCLK output from the master Cyclone III device to avoid signal strength and signal integrity issues. The buffer should not significantly change the DATA-to-DCLK relationships or delay them with respect to other AS signals (ASDI and nCS). Also, the buffer should only drive the slave Cyclone III devices, so that the timing between the master Cyclone III device and serial configuration device is unaffected.

This configuration method supports both compressed and uncompressed **.sof** files. Therefore, if the configuration bitstream size exceeds the capacity of a serial configuration device, you can enable the compression feature in the **.sof** file used or you can select a larger serial configuration device.

# Guidelines for Connecting Serial Configuration Device to Cyclone III Device on AS Interface

For single- and multi-device AS configurations, the board trace length and loading between the supported serial configuration device and Cyclone III device must follow the recommendations in Table 10–8.

| Table 10-0. Waximum made Length and Loading for Ao Configuration |                                                                                                  |                            |  |  |  |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------|--|--|--|

| Cyclone III AS<br>Pins                                           | Maximum Board Trace Length from<br>Cyclone III Device to Serial Configuration<br>Device (Inches) | Maximum Board Load<br>(pF) |  |  |  |

| DCLK                                                             | 10                                                                                               | 15                         |  |  |  |

| DATA[0]                                                          | 10                                                                                               | 30                         |  |  |  |

| FLASH_nCE                                                        | 10                                                                                               | 30                         |  |  |  |

| DATA[1]                                                          | 10                                                                                               | 30                         |  |  |  |

Table 10-8. Maximum Trace Length and Loading for AS Configuration

# **Estimating AS Configuration Time**

Active serial configuration time is dominated by the time it takes to transfer data from the serial configuration device to the Cyclone III device. This serial interface is clocked by the Cyclone III DCLK output (generated from an internal oscillator).

As listed in Table 10–7, the DCLK minimum frequency when using the 40-MHz oscillator is 20 MHz (50 ns). Therefore, the maximum configuration time estimate for EP3C10 (3,000,000 bits of uncompressed data) is:

## Equation 10-2.

$$\mathsf{RBF}\;\mathsf{Size}\times\left(\frac{\mathsf{maximum}\;\mathsf{DCLK}\;\mathsf{period}}{1\;\mathsf{bit}}\right)\;=\;\mathsf{estimated}\;\mathsf{maximum}\;\mathsf{configuration}\;\mathsf{time}$$

## Equation 10-3.

$$3,000,000 \text{ bits} \times \left(\frac{50 \text{ ns}}{1 \text{ bit}}\right) = 150 \text{ ms}$$

To estimate the typical configuration time, use the typical DCLK period as listed in Figure 10–7. With a typical DCLK period of 33.33 ns, the typical configuration time is 116.7 ms. Enabling compression reduces the amount of configuration data that is transmitted to the Cyclone III device, which also reduces configuration time. On average, compression reduces configuration time by 50%.

## **Programming Serial Configuration Devices**

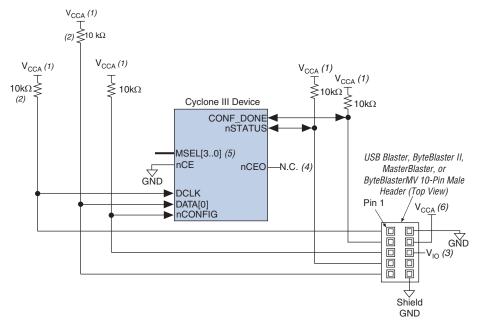

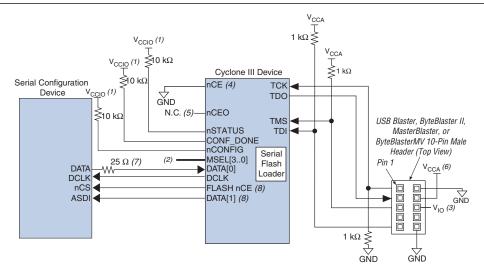

Serial configuration devices are non-volatile, flash-memory-based devices. You can program these devices in-system using the USB-Blaster™or ByteBlaster II™ download cable. Alternatively, you can program them using the Altera Programming Unit (APU), supported third-party programmers, or a microprocessor with the SRunner software driver.

You can perform in-system programming of serial configuration devices via the AS programming interface. During in-system programming, the download cable disables device access to the AS interface by driving the nCE pin high. Cyclone III devices are also held in reset by a low level on nCONFIG. After programming is complete, the download cable releases nCE and nCONFIG, allowing the pull-down and pull-up resistors to drive GND and  $V_{\rm CC}$ , respectively.

If you wish to use the same setup shown in Figure 10–7 to perform in-system programming of a serial configuration device and single- or multi-device AS configuration, you do not need a series resistor on the DATA line at the near end of the serial configuration device. The existing diodes and capacitors are sufficient.

Altera has developed the Serial FlashLoader (SFL), a JTAG-based in-system programming solution for Altera serial configuration devices. The SFL is a bridge design for the Cyclone III device that uses its JTAG interface to access the EPCS JTAG Indirect Configuration Device Programming (.jic) file and then uses the AS interface to program the EPCS device. Both the JTAG interface and AS interface are bridged together inside the SFL design (for more information about implementing the SFL with Cyclone III devices, refer to "Programming Serial Configuration Devices In-System Using the JTAG Interface").

For more information about the USB-Blaster download cable, refer to the *USB-Blaster Download Cable User Guide*. For more information about the ByteBlaster II cable, refer to the *ByteBlaster II Download Cable User Guide*.

Figure 10–7 shows the download cable connections to the serial configuration device.

Figure 10–7. In-System Programming of Serial Configuration Devices

#### Notes to Figure 10-7:

- (1) Connect these pull-up resistors to the  $V_{CCIO}$  supply of the bank in which the pin resides.

- (2) The nceo pin can be left unconnected or used as a user I/O pin when it does not feed other device's nce pin.

- (3) Power up the ByteBlaster II or USB-Blaster cable's V<sub>CC</sub> with the 3.3-V supply.

- (4) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect MSEL [3..0], refer to Table 10–6. Connect the MSEL pins directly to V<sub>CCA</sub> or ground.

- (5) These are dual-purpose I/O pins. The FLASH\_nce pin functions as the ncso pin in the AS configuration scheme. The DATA [1] pin functions as the ASDO pin in the AS configuration scheme.

- (6) The diodes and capacitors must be placed as close as possible to the Cyclone III device. You must ensure the diodes and capacitors maintain a maximum AC voltage of 4.1 V. The external diodes and capacitors are required to prevent damage to the Cyclone III AS configuration input pins due to possible overshoot when programming the serial configuration device using a download cable. Altera recommends using the Schottky diode, which has a relatively lower forward diode voltage (VF) than the switching and Zener diodes, for effective voltage clamping.

- (7) When cascading Cyclone III devices in a multi-device AS configuration, connect the repeater buffers between the Cyclone III master and slave device or devices for DATA[0] and DCLK. All I/O inputs must maintain a maximum AC voltage of 4.1 V. The output resistance of the repeater buffers must fit the maximum overshoot equation outlined in "Configuration and JTAG Pin I/O Requirements".

You can use the Quartus II software with the APU and appropriate configuration device programming adapter to program serial configuration devices. All serial configuration devices are offered in an 8- or 16-pin small outline integrated circuit (SOIC) package.

In production environments, serial configuration devices using multiple methods. You can use Altera programming hardware or other third-party programming hardware to program blank serial configuration devices before they are mounted onto PCBs. Alternatively, you can use an on-board microprocessor to program the serial configuration device in-system by porting the reference C-based software driver provided by Altera (that is, the SRunner software driver).

You can program a serial configuration device in-system by an external microprocessor using SRunner. SRunner is a software driver developed for embedded serial configuration device programming, which can be easily customized to fit in different embedded systems. SRunner is able to read a raw programming data (.rpd) file and write to the serial configuration devices. The serial configuration device programming time using SRunner is comparable to the programming time with the Quartus II software.

- For more information about SRunner, refer to the *AN 418: SRunner: An Embedded Solution for Serial Configuration Device Programming* and the source code on the Altera website (www.altera.com).

- For more information about programming serial configuration devices, refer to the *Serial Configuration Devices (EPCS1, EPCS4, EPCS16, EPCS64, and EPCS128) Data Sheet* chapter in volume 2 of the *Configuration Handbook*.

# **Active Parallel Configuration (Supported Flash Memories)**

Cyclone III devices offer the AP configuration scheme for Altera's devices. In the AP configuration scheme, Cyclone III devices are configured using commodity 16-bit parallel flash memory. These external non-volatile configuration devices are industry standard microprocessor flash memories. The flash memories provide a fast interface to access configuration data. The speed-up in configuration time is mainly due to the 16-bit wide parallel data bus, which is used to retrieve data from the flash.

Some of the smaller Cyclone III devices or package options do not support the AP configuration scheme and do not have the MSEL [3] pin (for more information, refer to Table 10–2).

During device configuration, Cyclone III devices read configuration data via the parallel interface, and configure their SRAM cells. This scheme is referred to as the AP configuration scheme because the device controls the configuration interface. This scheme contrasts with the FPP configuration scheme, where an external host controls the interface.

The Cyclone III remote system upgrade feature is available when you configure your Cyclone III device using the AP configuration scheme.

Table 10–9 shows the MSEL pin settings when using the AP configuration scheme with different configuration voltage standard.

| Configuration Scheme                                 | MSEL3 (5) | MSEL2 | MSEL1 | MSELO | Configuration Voltage<br>Standard <i>(4)</i> |

|------------------------------------------------------|-----------|-------|-------|-------|----------------------------------------------|

| Active Parallel ×16 Fast (AP Fast POR) (1), (2), (3) | 0         | 1     | 0     | 1     | 3.3 V (6)                                    |

| Active Parallel ×16 Fast (AP Fast POR) (1), (2), (3) | 0         | 1     | 1     | 0     | 1.8 V                                        |

| Active Parallel ×16 (AP Standard POR) (1), (2), (3)  | 0         | 1     | 1     | 1     | 3.3 V (6)                                    |

| Active Parallel ×16 (AP Standard POR) (1), (2), (3)  | 1         | 0     | 0     | 0     | 1.8 V                                        |

| Active Parallel ×16 (AP Standard POR) (1), (2), (3)  | 1         | 0     | 1     | 1     | 3.0/2.5 V (6)                                |

**Table 10–9.** Cyclone III MSEL Pin Settings for AP Configuration Schemes (Note 7)

#### Notes to Table 10-9:

- (1) These schemes support the remote system upgrade feature. Remote update mode is supported when using remote system upgrade feature. You can enable or disable remote update mode with an option setting in the Quartus II software. For more information about the remote system upgrade feature, refer to the *Remote System Upgrade With Cyclone III Devices* chapter in volume 1 of the *Cyclone III Device Handbook*.

- (2) Some of the smaller Cyclone III devices or package options do not support the AP configuration scheme (for more information, refer to Table 10–2).

- (3) In the AP configuration scheme, the commodity parallel flash is used as configuration memory (for information about the supported families for the commodity parallel flash, refer to Table 10–10).

- (4) Configuration voltage standard is applied to the  $V_{\text{CCIO}}$  supply of the bank in which the configuration pins reside.

- (5) Some of the smaller Cyclone III devices or package options do not support the AP configuration scheme and do not have the MSEL [3] pin (for more information about the supported configuration schemes across device densities and package options, refer to Table 10–2).

- (6) You must follow specific requirements when interfacing Cyclone III devices with 2.5-, 3.0-, and 3.3-V configuration voltage standards (for more information about these requirements, refer to "Configuration and JTAG Pin I/O Requirements").

- (7) You must connect the MSEL pins to  $V_{CCA}$  or GND depending on the MSEL pin settings.

## **AP Configuration Supported Flash Memories**

The AP configuration controller in Cyclone III devices is designed to interface with the Numonyx StrataFlash® Embedded Memory P30 flash family and the Numonyx StrataFlash Embedded Memory P33 flash family, which are two industry standard flash families. Unlike serial configuration devices, both of the flash families supported in AP configuration scheme are designed to interface with microprocessors. By configuring from an industry standard microprocessor flash which allows access to the flash once in user mode, the AP configuration scheme allows you to combine configuration data and user data (microprocessor boot code) on the same flash memory.

The Numonyx P30 flash family and the P33 flash family are similar because both support a continuous synchronous burst read mode at 40 MHz DCLK frequency for reading data from the flash. Additionally, the Numonyx P30 and P33 flash families have identical pin-out and adopt similar protocols for data access.

Cyclone III devices use a 40-MHz oscillator for the AP configuration scheme.

Table 10–10 shows the supported families of the commodity parallel flash for the AP configuration scheme.

Flash Memory

Density

Numonyx P30 Flash Family (2)

Numonyx P33 Flash Family (3)

64 Mbit

128 Mbit

256 Mbit

**Table 10–10.** Cyclone III Supported Commodity Flash for AP Configuration Scheme (*Note 1*)

#### Notes to Table 10-10:

- (1) The AP configuration scheme only supports flash memory speed grades of 40 MHz and above. You must refer to the respective flash datasheets to check for supported speed grades and package options.

- (2) 3.3-, 3.0-, 2.5-, and 1.8-V I/O options are supported for Numonyx P30 flash family.

- (3) 3.3-, 3.0- and 2.5-V I/O options are supported for Numonyx P33 flash family.

The AP configuration of Cyclone III devices supports the Numonyx P30 and P33 family 64-Mbit, 128-Mbit, and 256-Mbit flash memories. Configuring Cyclone III devices from the Numonyx P30 and P33 family 512-Mbit flash memory is possible, but you need to properly drive the extra address and chip select pins as required by these flash memories.

You must refer to the respective flash datasheets to check for supported speed grades and package options. For example, the Numonyx P30 and P33 families have only a single speed grade at 40 MHz. The synchronous burst read operation is permitted with all options of the P30 and P33 256-Mbit Thin Small Outline Package (TSOP) package when the clock frequency does not exceed 40 MHz and the P30 device does not operate below a minimum  $V_{\rm CC}$  of 1.85 V. Therefore, the P30 and P33 FBGA packages and only 256-Mbit TSOP devices are supported for the AP configuration scheme at this time.

However, they do not support 40 MHz on the TSOP packages. Therefore, the P30 and P33 FBGA packages are supported for the AP configuration scheme while the TSOP packages are not supported.

The AP configuration scheme in Cyclone III devices support flash speed grades of 40 MHz and above. However, AP configuration for all these speed grades must be capped at 40 MHz. The advantage of the faster speed grades is realized when your design in the Cyclone III devices accesses flash memory in user mode.

# **Single-Device AP Configuration**

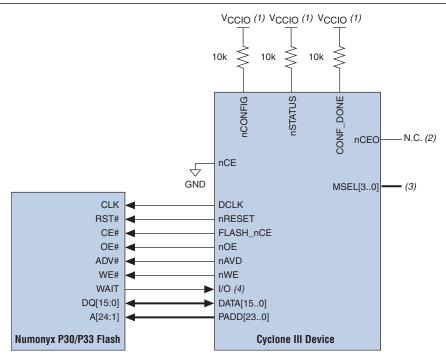

The three groups of interface pins supported in Numonyx P30 and P33 flash memories are the control pins, address pins, and data pins. In the AP configuration scheme, both of the supported parallel flash memories accept:

DCLK, active-low reset (RST#)

- active-low chip enable (CE#)

- active-low output enable (OE#)

- active-low address valid (ADV#), and

- active-low write enable (WE#)

as control signals from the Cyclone III device. The supported parallel flash memories output a control signal (WAIT) to the Cyclone III device to indicate when synchronous data is ready on the data bus. The Cyclone III device has a 24-bit address bus which connects to the address bus (A [24:1]) of the flash memory. A 16-bit bidirectional data bus (DATA [15..0]) provides data transfer between the Cyclone III device and the flash memory.

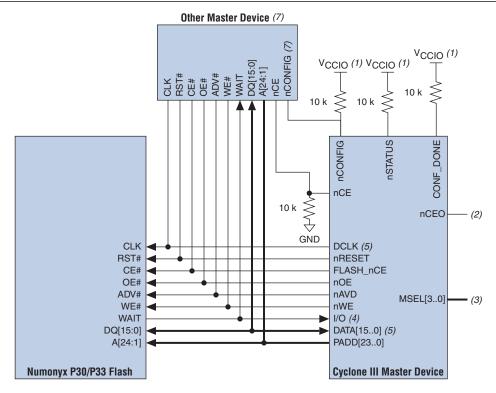

The control signals from the Cyclone III device to flash memory include DCLK, nRESET, FLASH\_nCE, nOE, nAVD, and nWE. The interface for the Numonyx P30 flash memory and P33 flash memory connects to Cyclone III device pins, as shown in Figure 10–8.

Figure 10-8. Single-Device AP Configuration Using Numonyx P30 and P33 Flash Memory

#### Notes to Figure 10-8:

- (1) Connect the pull-up resistors to the  $V_{CCIO}$  supply of the bank in which the pin resides.

- (2) The nceo pin can be left unconnected or used as a user I/O pin when it does not feed another device's nce pin.

- (3) The MSEL pin settings vary for different configuration voltage standards and POR time. To connect MSEL [3..0], refer to Table 10–9. Connect the MSEL pins directly to V<sub>CCA</sub> or GND.

- (4) AP configuration ignores the WAIT signal during configuration mode. However, if you are accessing flash during user mode with user logic, you can optionally use normal I/O to monitor the WAIT signal from the Numonyx P30 or P33 flash.

In a single-device AP configuration, the maximum board loading and board trace length between supported parallel flash and the Cyclone III device must follow the recommendation in Table 10–11.

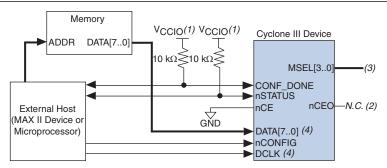

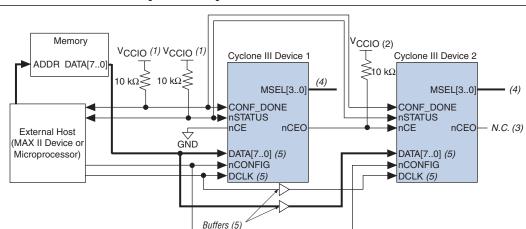

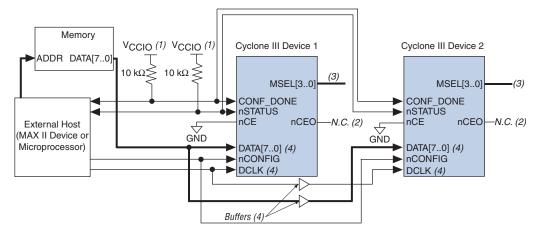

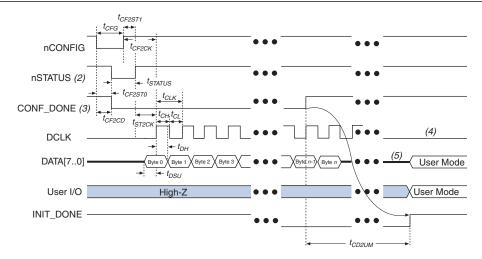

If you use the AP configuration scheme for Cyclone III devices, the  $V_{\text{CCIO}}$  of I/O banks 1, 6, 7, and 8, must be 3.3, 3.0, 2.5, or 1.8-V. Altera does not recommend using the level shifter between the Numonyx P30/P33 flash and the Cyclone III device in the AP configuration scheme.