# Challenges in Firmware Re-Hosting, Emulation, and Analysis

CHRISTOPHER WRIGHT, Purdue University

WILLIAM A. MOEGLEIN, Sandia National Laboratories

SAURABH BAGCHI, Purdue University

MILIND KULKARNI, Purdue University

ABRAHAM A. CLEMENTS, Sandia National Laboratories

System emulation and firmware re-hosting have become popular techniques to answer various security and performance related questions, such as, does a firmware contain security vulnerabilities or meet timing requirements when run on a specific hardware platform. While this motivation for emulation and binary analysis has previously been explored and reported, starting to either work or research in the field is difficult. To this end, we provide a comprehensive guide for the practitioner or system emulation researcher. We layout common challenges faced during firmware re-hosting, explaining successive steps and surveying common tools used to overcome these challenges. We provide classification techniques on five different axes, including emulator methods, system type, fidelity, emulator purpose, and control. These classifications and comparison criteria enable the practitioner to determine the appropriate tool for emulation. We use our classifications to categorize popular works in the field and present 28 common challenges faced when creating, emulating and analyzing a system, from obtaining firmwares to post emulation analysis.

CCS Concepts: • Computer systems organization  $\rightarrow$  Embedded and cyber-physical systems; Firmware; Embedded hardware; Embedded software; Real-time systems; • Hardware  $\rightarrow$  Simulation and emulation.

Additional Key Words and Phrases: Firmware re-hosting, system emulation, embedded systems, emulation fidelity, emulator classification, binary analysis, reverse engineering, emulation challenges

## **ACM Reference Format:**

Christopher Wright, William A. Moeglein, Saurabh Bagchi, Milind Kulkarni, and Abraham A. Clements. 2020. Challenges in Firmware Re-Hosting, Emulation, and Analysis. *ACM Comput. Surv.* 1, 1 (September 2020), 35 pages. https://doi.org/0000001.0000001

Sandia National Laboratories is a multimission laboratory managed and operated by National Technology and Engineering Solutions of Sandia, LLC, a wholly owned subsidiary of Honeywell International Inc., for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA0003525. This paper describes objective technical results and analysis. Any subjective views or opinions that might be expressed in the paper do not necessarily represent the views of the U.S. Department of Energy or the United States Government. SAND2020-10079 J

Authors' addresses: Christopher Wright, christopherwright@purdue.edu, Purdue University; William A. Moeglein, wmoegle@sandia.gov, Sandia National Laboratories; Saurabh Bagchi, sbagchi@purdue.edu, Purdue University; Milind Kulkarni, milind@purdue.edu, Purdue University; Abraham A. Clements, aacleme@sandia.gov, Sandia National Laboratories.

Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for third-party components of this work must be honored. For all other uses, contact the owner/author(s).

© 2020 Copyright held by the owner/author(s). 0360-0300/2020/9-ART

https://doi.org/0000001.0000001

#### 1 INTRODUCTION

The number of connected devices, from appliances to smart home and personal gadgets, has increased dramatically with the explosion of Internet of Things (IoT). Along with these every day gadgets, large scale infrastructures such as the electric grid, cellular networks, and other large control systems have become smarter, digital, and interconnected. [62, 98, 107, 120, 178]. Understanding how these systems work and discovering vulnerabilities in their firmware is an important and growing topic in academic and industrial research, with large companies paying millions of dollars for bugs found in their devices [1, 30, 32, 77, 118, 140]. The increased effort to protect connected devices has come from an increased awareness of their vulnerability and the attacks targeting them [3, 43, 82, 85, 101, 123, 166, 174, 183]. Many of these systems have access to sensitive financial data, personal information, or control critical processes. Malicious actors are exploiting vulnerabilities in these systems to cause harm to businesses, individuals, and critical systems such as electrical grids and cellular infrastructure.

Emulation of embedded systems is an emerging technique to accelerate discovery and mitigation of vulnerabilities in embedded system firmware. Embedded system emulation has traditionally been used during development to allow embedded software to be written and tested without the need for hardware. In cases where hardware is concurrently being developed, is costly to have in quantity, or is susceptible to damage, emulation is an appealing option. Just as emulation can be used to verify system behavior during development, it can be used for vulnerability research and analysis. Emulation provides the ability to deeply observe and instrument firmware in ways that are not possible on physical hardware. It can help analyze what operations are actually being performed at a lower level than static analysis of either the high level source code or even the binary level, and is a useful tool that is the basis for a host of vulnerability discovering techniques [35, 44, 91, 137, 146, 151, 160, 169] among other uses outlined in Section 2.

For a practitioner to use emulation or re-host¹ a firmware, there is a learning curve and a plethora of tools available. Our primary purpose is to provide an end-to-end guide to the practitioner for firmware re-hosting. We limit our focus on emulation and re-hosting to the embedded space, as virtually any system will have embedded devices, from wearable IoT devices to power plants, which if vulnerable will affect the entire system's security and functionality. We present an overview of current techniques/tools for the practitioner along with classification categories and techniques for evaluating which tool is best for the emulation task at hand. We provide tables for the practitioner to reference in subsequent challenge sections that specify whether a tool attempts to address the presented challenges, giving a starting point for the practitioner to evaluate the right tool to overcome challenges.

We proceed with a brief history and background of emulation in Section 2. We then introduce surveyed works in Section 3 before introducing different comparison techniques in Section 4. We continue by comparing surveyed works for emulation in Section 5. We discuss the necessary pre conditions and challenges for re-hosting firmware in Section 6. We then proceed to break the challenges into three categories, Pre-Emulation, Emulation and Post Emulation and provide tool comparisons in Section 7, Section 8, and Section 9 respectively. We finish by discussing different considerations when choosing re-hosting tools in Section 10 and a summary in Section 11.

<sup>&</sup>lt;sup>1</sup>Re-hosting specifies that a binary that would run on a specific hardware is instead run on a host system using system emulation, and is therefore "re-hosted"

## 2 EMULATION BACKGROUND

#### 2.1 Evolution of Emulation

Since before the era of personal computers, emulation has been a technique used to broaden hardware use and increase simulation speed. For example, most printing software used to be designed for HP, so many non-HP printers would write an emulator to re-host the software designed for HP [73]. Re-using HP software allowed for faster time to market for new printers and reduced the development time and effort for creating new products.

Emulation theory was first developed in the early 1960s, with the 7070 Emulator for the IBM System/360 series of mainframe computers being the first implemented emulator [83]. This emulator allowed IBM's customers to continue running their existing applications after upgrading their hardware. As was the case for the 7070 emulator, early uses of emulation was to avoid obsolescence and increase hardware compatibility with the limited available software. Over time, manufacturers started creating hardware emulators to allow software development before the hardware production; decreasing product development time. Emulators are now becoming a popular tool for security analysis and logic debugging [91, 129, 160, 169].

Around the same time frame, simulation was also used, but it allowed for executing and expanding systems beyond what existed. Simulation is sometimes referred to in scientific modeling and investigating, but in this context, simulation is another technique to model the internals of a system. In the computer science context, simulation is modeling a system with implementation of the internals, whereas emulation is modeling by replacing some of the internals of the system. By replacing some of the internals, emulation can sometimes reduce complexity or increase firmware re-hosting speed. Emulation will often allow for original machine code to run directly on the emulator. Beyond the computer science context, simulation and emulation are sometimes used interchangeably, with simulation sometimes refering to a system being replaced by software. For our case, the distinction is not important, but the tools we survey mostly refer to their techniques as emulation.

One of the early emulation successes was Bochs [96], which was released in the early 90's. It emulated the underlying hardware needed for PC operating systems development, which enabled completely isolating the OS from the hardware. This isolation enabled restarting the emulator instead of reconfiguring hardware during OS development. Bochs was originally commercial licensed but was open sourced in 2000. In addition to Bochs, many other emulators were created including DOSBox [52], FX!32[27], and PCem[126]. These solutions were mainly geared for x86 or PC emulation.

As multiple emulators emerged, the *execution and memory fidelity* (*i.e.*, how closely the emulated system matches the real system, sometimes referred to as accuracy) varied from high (cycle and register accurate) to low (module and black box accurate). We discuss fidelity and give more classification points in Section 4.3, but fidelity and emulator speed are perhaps the greatest distinguishing factors between different emulators.

## 2.2 Emulation Bases

In the early 2000's, **Simics** [105] was created and evolved to emulate multiple architectures including Alpha, x86-64, IA-64, ARM, MIPS (32- and 64-bit), MSP430, PowerPC (32- and 64-bit), SPARC-V8 and V9, and x86 ISAs. It was originally developed by the Swedish Institute of Computer Science (SICS) before moving to Virtutech and eventually working its way to Wind River Systems, who currently sells it. Simics is designed to have fidelity at the instruction level, allowing for interrupt testing to occur between any pair of instructions. It also provides configuration management, scripting, automated debugging (forward and reverse), and other built in static and dynamic analysis tools to

help with constructing an emulated system. One popular use for Simics was during the DARPA Cyber Grand Challenge to automatically vet submissions to check whether the submitted binaries adhered to the competition infrastructure [168].

In contrast to Simics and emulators that work at the instruction level fidelity, **QEMU** [11] gives up some accuracy to improve emulation speed. Instead of working as a sub-instruction simulator (performing multiple actions per instruction), QEMU execution and emulation occurs at the basic block level (sequential, non-control flow instructions), by translating entire blocks of instructions to the host system's instruction set and executing the translated instructions. This allows QEMU to work much faster, as it does not have to check for interrupts at each instruction, and caching of blocks greatly reduces translation overhead. Because of its open-source license and community, QEMU has become one of the staples in academia and for industry professionals. It emulates the IA-32, x86, MIPS, SPARC, ARM, SH4, PowerPC, ETRAX CRIS, MicroBlaze, and RISC-V architectures, and provides peripherals for many systems, making it and Simics two of the most widely used emulators.

One of the newest emulators available is **Ghidra Emulator**. Ghidra [119] is an open source software reverse engineering tool developed by the National Security Agency (NSA). The initial release in March 2019 contains emulation tools that allow for traditional software reverse engineering and emulation to be combined into the same environment. Because of the richness of features in these tools, there has been a large user base since release. Ghidra uses their own processor modeling language called Sleigh and an intermediate register transfer language called P-code, with each machine instruction translating to up to 30 P-code instructions. This implies that the Ghidra Emulator works at the sub-instruction level (multiple emulator instructions performed per machine instruction), giving a relatively high execution fidelity as a base. Ghidra currently supports various existing architectures including X86 16/32/64, ARM/AARCH64, PowerPC 32/64, VLE, MIPS, MSP430, Z80, AVR, etc. To add a new architecture is simple in their framework, with the user only specifying how the new architectures instructions are dissassembled into the intermediate P-code language. Ghidra includes loaders, disassemblers, decompiler and analysis tools with the base of supplied analyses written in Java. Beyond the built-in emulator, there have been Ghidra P-code emulators emerging that allow for partial re-hosting of firmwares [153].

## 2.3 Related Vulnerability Discovery Techniques

As emulation has been used more frequently for vulnerability discovery, it is worth mentioning some closely related vulnerability discovery techniques that often leverage emulation. The techniques introduced are integrated into some frameworks that work with the base emulators, requiring at least some familiarity during discussion. We do not go into extensive depth for the areas, but rather overview the techniques briefly, and recommend further reading for an in depth review. We mention some of the tools that are more popular, but it is not necessary to understand their differences or techniques in the scope of our review, rather the techniques are mentioned briefly in subsequent sections when integrated into a tool.

**Symbolic Execution** is where symbols representing arbitrary values are supplied as inputs to a program (similar to letters in algebra representing numbers). The goal of symbolic execution is to analyze a program to determine what inputs can cause different parts of a program to execute. Rather than analyze and follow a single path with concrete values, a symbolic execution engine will use symbols to describe all program execution paths that can execute by using constraints on symbols.

**Concolic Execution** is when the tool will switch between using symbolic symbols and concrete symbols (like an algebra symbol having a set value, eg x=5) during emulation or execution. When reverse engineering firmware, an analyst will occasionally want to determine under what conditions

a program will execute a certain portion of code. Symbolic and Concolic execution are tools that help solve this problem among other vulnerability discovery uses. Symbolic execution is now a common software testing practice, even though it was introduced in the '70s [20]. Commonly used symbolic and concolic execution tools include [10, 13, 15, 16, 19, 23, 24, 28, 38, 47, 61, 79, 103, 111, 141, 144, 147, 151].

**Fuzzing** is an automated vulnerability/bug discovery technique where random inputs are provided, and the system observed for undesired behavior (*e.g.*, crashes). There are many challenges to fuzzing and various tools that try to address these challenges. In the context of emulation, fuzzers often leverage the visibility into, and control over, a binary's execution to optimize their random inputs to improve their exploration of the binary. Some popular fuzzing tools that can be integrated with emulation are [2, 14, 39, 51, 63–71, 80, 108, 127, 134, 135, 145, 156–158, 184].

## 3 SURVEYED WORKS

Prior to introducing emulation comparison axes, we introduce surveyed works that enable emulation and firmware re-hosting. We do not discuss or reintroduce Simics, QEMU, or Ghidra Emulator, as they are described in Section 2.2, but they are the base emulators used in the tools introduced in this section. Base emulators can either run in user mode emulation (*i.e.*, running just user level applications) or full system emulation; with full-system emulation currently being the primary mode used for firmware re-hosting. Full-system emulation will emulate the processor as well as hardware peripherals; however, the set of emulated peripherals available in the base emulators are small compared to the diversity of hardware found in embedded systems. Much of the work in firmware emulation aims at solving this lack of emulated peripherals.

**Avatar**<sup>2</sup> [112] is a *dynamic multi-target orchestration and instrumentation framework* that focuses on firmware analysis. This tool was created by the same group as Avatar, but is a multi-target orchestration tool that has completely been re-designed from the original Avatar implementation [185].

The main contribution of this tool is that it allows various other tools (angr, QEMU, gdb) to interact and transfer data. Using these tools it can enable hardware in the loop emulation, where portions of execution or memory accesses are carried out by physical hardware.

angr [151] is a symbolic execution engine, that has been integrated with Avatar<sup>2</sup> to enable combining symbolic execution and other analysis into the concrete base QEMU emulator. angr is a binary analysis framework that provides building blocks for many analyses, both static and dynamic. angr provides an architecture library, an executable and library loader, a symbolic execution engine, built in analyses, and a python wrapper around a binary code lifter. It is actively developed and used in various other academic works including [9, 104, 124, 128, 148, 150, 158, 175, 176]. We include this as one of the surveyed works because of its ability to use base emulators while providing new approaches and solutions to overcome emulation challenges from beginning to end.

**HALucinator** [35] addresses the challenge of providing peripherals not implemented in the base emulator by observing that the interactions with peripherals are often performed by a Hardware Abstraction Layer (HAL). It uses Avatar<sup>2</sup> and QEMU as bases to intercept HAL calls and replace them. They do this by manually providing replacements for HAL functions that execute during re-hosting. It uses a library matching tool to identify the HAL functions in the firmware. The tool relies on the assumption that the majority of firmware programmers use Hardware Abstraction Libraries when writing firmware, which in our experience is a relatively safe assumption.

**PANDA** [50] is an open-source platform that builds on top of the QEMU whole system emulator that is used for architecture-neutral *dynamic analysis*. The main advantage of PANDA is that it adds the ability to record and replay executions, allowing for deep, whole-system analyses. System record has partially been addressed in a hardware-software co-design approach [161] as well as

under more restrictive assumptions, using a purely software approach [159, 162]. Such whole system record and replay is challenging especially considering the timing requirements. PANDA, using the QEMU base and abstracting some of the analyses, allows for using a single analysis implementation across multiple computer architectures while maintaining the speed of QEMU, allowing some timing challenges to be addressed.

**Muench2018**, titled "What You Corrupt Is Not What You Crash: Challenges in Fuzzing Embedded Devices" [113] demonstrate that tools used for desktop vulnerability discovery and testing do not necessarily transfer to the embedded space. In their paper they present different techniques used for vulnerability assessment implemented by instrumenting an the emulator used for re-hosting the firmware. They implement segment tracking, format specifier tracking, heap object tracking, call stack tracking, call frame tracking, and stack object tracking by combining PANDA and Avatar<sup>2</sup>.

Using QEMU as a base, both **Firmadyne** [25] and Costin Firmware Analysis (referred herafter as **CostinFA** [43, 44] "A Large-Scale Analysis of the Security of Embedded Firmwares" and "Automated Dynamic Firmware Analysis at Scale: A Case Study on Embedded Web Interfaces"), will extract the filesystem from a given firmware and re-host the filesystem on their own kernel. They perform system emulation using only software, not involving any physical embedded devices. Their tools work only for software images that can natively use chroot with QEMU. They then perform static and dynamic analysis on their re-hosted firmware to report vulnerabilities. Recent efforts that use the same type of approach as Costin and Firmadyne is ARMX [146]. ARMX requires more user interaction and configuration and only works for ARM architecture devices while requiring the rootfs from the firmware and the extracted NVRAM from the firmware. Given these extra requirements, the results of the emulated devices using their technique is usually of high quality.

**PROSPECT** [84] and **SURROGATES** [90] enable emulation by forwarding hardware and peripheral accesses to the actual device; a technique known as hardware in the loop. PROSPECT forwards peripheral and hardware interactions through a normal bus connection to the device, but allows for analysis and implementation without needing to know the details about the peripherals and external hardware connected to the system. SURROGATES, in contrast, uses a custom low-latency FPGA bridge between the host PCI Express bus and the system under test, allowing forwarding and state transfer to and from the system's peripherals with transfers much faster than the original Avatar [185] system.

**P**<sup>2</sup>**IM** [57] uses a drop-in fuzzer (AFL[2]) to provide inputs to their base QEMU emulator. They abstract peripheral and hardware IO and then use the fuzzer for providing the feedback to the base emulator. Their approach is different from existing emulation approaches as it does not use hardware or detailed knowledge of the peripherals, as the fuzzer provides interactions. The fuzzer enables executing firmware with simple peripherals to be emulated, but its ability to enable emulation of firmware processing data from complex and stateful hardware is unknown.

In contrast to using a random fuzzer, **Pretender** [72] attempts to re-host firmware by using machine learning to provide models of hardware interactions. Their system will record hardware interactions and all accesses to memory mapped input and output (interacting with peripherals is done through a specified memory-mapped address - MMIO) regions along with any interrupt that occurs during execution before performing a peripheral clustering and dividing the recordings into sub-recordings for each peripheral. They then train a memory model, trying to select and train on known models for each peripheral. The analyst then decides how to introduce inputs into the system.

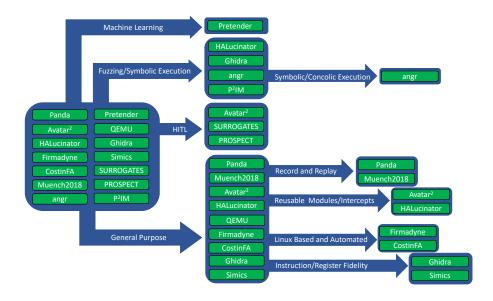

In summary of the tools that are surveyed (highlighted in bold throughout Section 2 and Section 3) the general purpose emulators surveyed that have a wide variety of specialties and uses include Avatar<sup>2</sup>, CostinFA, Firmadyne, Ghidra, HALucinator, Muench2018, Panda, QEMU, and Simics. Emulators that use hardware in the loop include Avatar<sup>2</sup>, SURROGATES, and PROSPECT. Emulators

that can use symbolic execution and/or fuzzing include angr, Ghidra, HALucinator, and  $P^2$ IM. The only emulator that uses machine learning for models is Pretender, which at the moment to be successful requires fairly simple firmware. If the reader is anxious for a flow-chart of which tool to use, refer to Figure 4 that is explained in Section 10. While this is not an exhaustive list of tools or methods, as there are many more available including [17, 18, 33, 40, 48, 48, 60, 75, 76, 82, 86, 87, 92, 94, 99, 136, 139, 155, 156, 164, 167, 173] among others, we believe the scope of tools and their applicability is encompassed in the tools mentioned above.

## 4 EMULATION COMPARISON AXES

Prior to discussing the core challenges of emulation, we first introduce axes over which the comparison of different emulators can be compared. Various emulators and emulation techniques are used for different purposes, and thus make different design decisions. Establishing common axes to evaluate emulators is necessary to enable the practitioner to do a useful comparison before choosing the ideal emulation tool for their use.

# 4.1 Emulation Techniques

A significant challenge to re-hosting firmware is the large expanse of hardware peripherals that need to be emulated; thus, one evaluation axis is the fundamental technique the emulator uses to provide these peripherals. The technique employed will directly relate to another axis of comparison – the complexity of the hardware that is feasible to emulate. Some systems are simple with no peripherals, whereas others may be connected to Remote Terminal Units (RTU), Programmable Logic Controllers (PLC), Field-Programable Gate Array (FPGAs), multiple sensors, databases, Human Machine Interface controllers (HMI), etc. The amount of hardware the practitioner wants to emulate will range from a single chip or sensor, all the way up to the entire large scale system. The amount of hardware and complexity of the hardware emulation is largely limited by the peripheral emulation technique used.

The main peripheral interaction techniques used include *hardware in the loop* (HITL), *learning, fuzzing*, and *abstraction replacement*. *HITL* will use the emulator to perform instruction execution, but if accesses are made to hardware peripherals they are forwarded to the actual hardware. *Learning* refers to using machine learning to provide hardware interactions, whereas *fuzzing* will use random generation to provide simulated hardware interactions. *Abstraction replacement* provides peripheral hardware functionality by identifying software abstractions within the firmware and replaces execution of these abstractions with its own implementations. Examples of surveyed works that allow HITL are SURROGATES[90] and Avatar<sup>2</sup> [112]. P<sup>2</sup>IM[57] uses fuzzing, and Pretender[72] uses Learning, whereas Firmadyne [25], CostinFA[43, 44], and HALucinator[35] use abstraction replacement.

## 4.2 Types of Systems

In addition to how hardware peripherals are provided, it is important to consider the type of system the emulator is designed to support. The range and capabilities of embedded systems ranges from large multi-processor systems running customized versions of desktop OSes (e.g., Linux) to low cost, low power micro-controllers running a few KB of code without an OS. The challenges and techniques in emulating these systems vary and may or may not translate from system to system. We reuse the classification presented by Muench et al. [113], though use our own names instead of numbers for the types of systems, splitting the embedded system types into three different classes, based on the type of firmware they execute.

General Purpose Embedded Systems (GPES): also known as Type 1 embedded system, use a general purpose operating system that is primarily used on servers and desktop systems. Examples include real-time Linux, embedded Windows, and Raspberry Pi. The operating systems are retrofitted for the embedded space, but retain many desktop level features, but with stripped down components, and are coupled with lightweight user space environments such as busybox or uClibc. Tools such as Firmadyne and CostinFA require the embedded system they work on to be Linux based systems and will only work on this type of system. Emulating these types of systems greatly benefits from the work done to enable emulation of desktop software and operating systems (e.g., QEMU directly supports emulating the Linux Kernel).

**Special Purpose Embedded System (SPES)**: (Type 2 devices from [113]) use operating systems specifically developed for embedded systems. They are often commercial products and closed source. Examples include,  $\mu$ Clinux, ZephyrOS, and VxWorks. These systems are usually single-purpose electronics or control systems. Some of the features that distinguish these systems are that the OS and applications may be compiled separately and the system is not derived from a desktop operating system. Thus, many emulation techniques from the desktop space do not work, and emulation must start from scratch. Re-hosting these systems requires re-hosting both the kernel and user space. Also adding to the challenge of emulating these systems is the fact that the separation between the Kernel and user space is often blurred.

**Bare-metal Embedded Systems (BMES)**: Type 3 devices are embedded systems without a true OS abstraction that we refer to as bare-metal embedded systems (BMES). They often do not have an OS, or may include a light-weight OS-Library. An example is an Arduino system. In both cases, the application will directly access hardware and the OS (if present) and applications are statically linked into a single binary. Recent work [35, 57, 72] focuses on re-hosting these systems.

We find this axis of comparison useful as it helps to determine what emulation techniques an analyst should consider for a given firmware. However, in practice, classifying a system is not necessarily cut and dry. Rather the classification is a continuum on the embedded space. For example, an embedded system that started out using UNIX OS 30 years ago may have originally been classified as a GPES, but as the system morphed over time, the same system currently may now be better classified as a SPES.

## 4.3 Fidelity

Introduced in Section 2, *fidelity* is perhaps the most important comparison axis, but also the most difficult to quantify. The difficulty comes from limited ability to inspect the internal state of hardware, and is further complicated by the ability to compare states. In an effort to enable better understanding of fidelity, we classify fidelity along the conceptual axis of *execution fidelity* and data or *memory fidelity*. This enables comparison of the conceptual limits of fidelity on a 2D plane. Work by Costin [44] has a general classification of emulators that have kernels and applications. The classification we present here is more general, applies to both re-hosting and emulators, has more classification points, and is applicable to all types of systems – GPES, SPES and BMES. The fidelity classifications are from the perspective of the firmware (software), and whether the emulation "looks" and "acts" like real hardware. This implies that we do not need to differentiate between memory (whether DRAM, SRAM, Flash, etc.) that looks the same to the firmware, we just refer to this as internal memory. If there is another driver required to use specific memory (such as an SD card), then we consider this external memory.

Execution fidelity describes how closely execution in the emulator can match that of the physical system. We bin techniques into the categories *BlackBox*, *Module*, *Function*, *Basic Block*, *Instruction*, *Cycle*, *and Perfect*, with execution fidelity increasing from BlackBox to Perfect. A system emulated with *BlackBox* fidelity exhibits the same (or sufficiently similar) external behavior as the real system,

but internally may or may not execute any of the same instructions a real system would execute. Module fidelity provides fidelity at the module level. For example, Firmadyne replaces the original firmware's kernel with its own to enable re-hosting the original firmware. Thus some modules of the firmware are executed unmodified, and others completely replaced. Function level fidelity accurately models the system at the function level (e.g., HALucinator replaces entire functions to enable emulation). Similarly, basic block and instruction level fidelity accurately emulate at the basic block and instruction level layers. Beyond instruction level is cycle level which faithfully emulates to cpu instruction cycle (e.g., the gem5 [12] simulator). Perfect emulation means that emulation is exactly the same as it would be on the actual hardware, which to our knowledge no current emulator achieves.

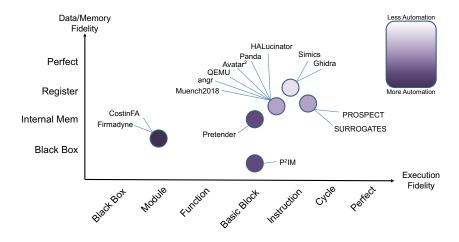

We categorize data/memory fidelity increasing from the coarsest granularity to finest granularity as BlackBox, Internal Memory, Register, and Perfect. BlackBox fidelity means that the data externally visible to the system or external memory (e.g., HDD or SDD) is the same (e.g., for a given input we get the same output). Internal Memory means that the internal memory (e.g., RAM) is consistent with hardware for a given point in execution. Register level fidelity means that both internal memory and registers are correct at the given execution fidelity and perfect means that all memory components work the exact same as the given system at the level of execution fidelity needed. In Blackbox, Internal Memory, and Register Memory levels, these classifications are usually for specific areas of interest in the firmware. This means that there is a blur between the classification points, as some sections of the firmware may be at the Blackbox level where the user does not care much about the internals, but in a few sections of high interest the firmware emulation may be at the Internal or Register Level fidelity. The Perfect Emulation level is on the scale but currently is virtually unobtainable. Depending on the practitioner, Perfect Emulation level can mean Register level throughout the entire firmware, or it could mean everything is exact, down to the cache for every execution cycle. In Figure 1 we show how the most prevalent firmware emulation techniques fit into this classification framework.

## 4.4 Purpose of emulator

Of the surveyed research works in firmware re-hosting, the main focus points have been *Creating Emulators*, *Dynamic Analysis*, *Static Analysis*, *and Fuzzing*. Each of these focus points enables the emulator to answer specific questions. The purpose of emulators include vulnerability detection, enabling running legacy code, hardware replacement, development assistance, and system behavioral analysis. The purpose of the emulator directly influences the techniques employed, types of systems the emulator will work on and for, and determine the fidelity of the system.

#### 4.5 Level of Control

Another axis for comparison related to the purpose of the emulator, is the ability to control the exploration in firmware and what the tool can/should be used for. Control may perhaps be thought of as another axis in fidelity, quantifying whether you can control emulation and what is actually executed during emulation. It also refers to the level of interaction available to the practitioner. For example, HALucinator enables interactive emulation making it suitable for building virtual testbeds, whereas P<sup>2</sup>IM enables fuzzing and would not be a feasible tool for testbeds.

For visualization ease we do not combine fidelity and exploration, but it is important to note that some tools and emulators do not allow for controlled exploration. For example, if your emulator is just fuzzing everything from memory to inputs, it may have very high execution fidelity, and low memory fidelity, but it has almost no exploration customization to specify what to execute, it solely relies on a random generator. Randomization and fuzzing enable high coverage fuzzing and vulnerability discovery, but it does not give a clear picture of actual real possibilities of execution.

Fig. 1. Categories of Fidelity

## 5 CLASSIFICATION OF SURVEYED WORKS

Now that we have discussed different axes of fidelity, we further categorize and compare surveyed works in firmware re-hosting and emulation. Figure 1 shows a 2D space of fidelity categorization. On the horizontal axis is execution fidelity and on the vertical axis is data fidelity. As can be seen in the figure, there is not a single point for each category, rather a blurry bubble, emphasizing that fidelity categorizations are conceptual and a continuum from black box to perfect fidelity. As can be seen in Figure 1, the points on the plot range from dark to light shading. The darker the circle indicates that the tools is more automated, requiring less user interaction and requirements for setting up the tool. The lighter the circle in the plot indicates that the default tool requires more user interaction to get the tool setup. We purposefully do not give concrete numbers to the automation or the fidelity levels, rather we visually categorize automation and place fidelity in regions to re-emphasize that these categorizations are not concrete and may slightly move/change depending on tool use and the practitioner's opinions.

## 5.1 Hardware In The Loop

As various works modify a core emulator, the fidelity can be improved or reduced. When the fidelity is improved there is often a trade off made in performance or complexity. SURROGATES uses QEMU as a base emulator, but adds specialized hardware to enable faster communication with real hardware. Specialized hardware allows for higher execution fidelity as the peripheral access is then perfect. HITL also increases the data fidelity, as there is no generalization for the peripheral model as is the case for PROSPECT. However, specialized hardware and HITL in general increases the complexity and cost of performing emulation while reducing scalability, as dedicated hardware is needed for each emulated system.

## 5.2 Instruction Level Execution Fidelity

We categorize Simics and Ghidra Emulator as instruction level execution fidelity while also having register level data fidelity because of their sub-instruction execution. While the coloring of the automation is the lightest of the works surveyed, there are ready made implementations of both of these emulators that can be copied or used out of the box to make the automation much closer to

no interaction required. Yet, we color the automation at this level because of the tools defaults and to show the open ended-ness of using one of these emulators.

# 5.3 Basic Block Level Execution Fidelity

As mentioned previously, QEMU has basic block execution fidelity, and RAM fidelity as a default on the data fidelity axis. These are the default categorizations, and they can be affected by other tools. Muench2018, angr, Panda, and HALucinator use QEMU as a base emulator without HITL, so in general their fidelity will be less than or equal to that of QEMU.

For any memory interaction, P<sup>2</sup>IM will do random fuzzing, meaning there is not even blackbox fidelity for the data axis. Pretender uses machine learning to attempt to provide peripheral software replacement modules, reducing the data fidelity but still has some internal memory correct and at least blackbox fidelity on the data axis. As these works reduce fidelity (on either axis) they also decrease the amount of effort needed for their emulation. Muench2018 and PANDA perform tracking/recording as mentioned in Section 3. While replaying and replication is enabled, the fidelity is still maxed out at the Basic Block and Internal Memory/Register fidelity because of the QEMU base emulator fidelity.

angr also uses QEMU for the emulation part of the tool, while also using symbolic execution. Symbolic execution is difficult to put on the emulation fidelity grid because it has multiple states as it executes, but by using QEMU for concolic and concrete execution, angr receives the same fidelity as the QEMU base. In contrast, Avatar<sup>2</sup> enables the interaction between virtually any of the tools, allowing the fidelity to be at any of the tools fidelity categorization depending on what is programmed by the analyst, but we show its fidelity point defaulting around QEMU, angr, PANDA, and HALucinator because they are default tools that are easy to get running in the Avatar<sup>2</sup> framework.

# 5.4 Module Level Execution Fidelity

Firmadyne and CostinFA lose both execution and data fidelity from their base QEMU emulator as they only extract the filesystem and run the code through their own kernel. However, by doing this they drastically increase the automation of their tools, making mass analysis of firmware more scalable.

## **6 QUESTIONS AND CHALLENGES**

The remainder of the paper focuses on you, the analyst wanting to re-host a firmware, and discusses the challenges that are encountered, along with techniques and tools that can be used to address them. The challenges and tools surveyed provides a reference for the average practitioner or a starting point for new researchers in the area of firmware re-hosting and system emulation.

## 6.1 Questions of Purpose and Value

Each emulation tool has requirements that must be met before being able to re-host firmware. Some tools will bypass common emulation challenges with the technique they use. Ideally the tool will overcome challenges automatically, otherwise the practitioner must do so manually. Common preconditions are discussed in Section 7, however this discussion covers the challenges faced and not necessarily why they are encountered.

Before deciding to emulate a system or re-host a firmware, an analyst has a question they want answered. The idea of why to emulate a system is key to building emulators and is often not emphasized in emulation papers. When an analyst wants to find vulnerabilities, there are vulnerabilities that may be discovered at each fidelity level. It is therefore important to know what types of vulnerabilities you are looking for, e.g. is it a firmware logic error that can be detected

by just correctly emulating the memory, or is it an instruction or hardware bug that needs higher execution fidelity?

Before emulating a system it is also important to do an analysis on the estimated cost and value-for-money evaluation of getting the emulation to work correctly and the tools to be used to perform emulation. To emulate some systems it may take a small team of engineers 6 months to a year to build and test for the desired system. This may be a bargain or may be too expensive. Analyzing the tools available and how to use them can speed up or even change the traditional approach of building an emulator (manually reverse-engineering the hardware, re-hosting firmware until failure and incrementally adding functionality).

## 6.2 Key Research Questions

We wish we could say that you should research one specific area, but for every solution/tool that currently exists, there are shortcomings. To understand what is *key* to your research, it is necessary to understand what you would like to solve with emulation. The key area we see that needs addressed is speeding up the time to emulate a system – this includes tools from all the subsequent sections to overcome the challenges. A script written for one tool may work to address a specific challenge, but that script needs to be ported if using another tool, *e.g.*, a script for Ghidra to help find the entry point will not necessarily work with angr or Simics.

This *key* research area of speeding up emulation really encompasses research across all types of embedded systems (GPES, SPES and BMES) and includes new ways of overcoming problems presented in Section 7, Section 8, and Section 9. Any tool or technique that more efficiently addresses the challenges is a useful area of research.

# 6.3 Challenges

Now that we have introduced surveyed works and classification criteria, we present some of the core challenges faced during firmware re-hosting and system emulation. During the emulation pipeline, various challenges are encountered and we split these challenges into:

- Pre-Emulation

- Emulation

- Post Emulation

Pre-Emulation are challenges that are pre-requisites to emulation execution and overcoming these challenges enables executing the first instruction in the emulator. These challenges include obtaining firmware, unpacking the firmware and gaining and understanding how to configure the emulator to re-host the firmware. Once the first instruction is executed in the emulator, we consider the Emulation stage to have been started, however, as execution progresses, greater understanding of the firmware is obtained, which leads to refinement of the emulator configuration and implementation. Thus, we break Emulation into Emulator Setup — challenges that enable further refinement of the emulator and more complete execution — and Emulation Execution — challenges fundamental to emulation itself. Finally after emulation there is the Post Emulation stage where the execution is analyzed and validated. The challenges presented here have been mentioned in part and used as the foundation for multiple industrial and academic works, but we present them in entirety here for completeness.

In the tables throughout the rest of the paper, we survey different techniques that attempt to overcome the various challenges faced during emulation and binary analysis. If there is a checkmark, then the tool attempts to address the issue; but, it does not necessarily solve the problem and some tools work better than others, though we do not specify our opinions on the matter. If there is a dash, that means the tool bypasses the challenge by the technique they employ. If there

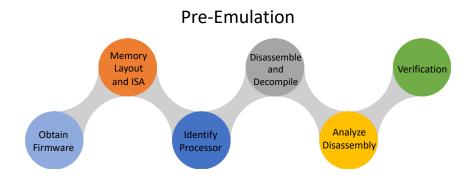

Fig. 2. Categorization and flow of some of the steps required for system emulation during Pre-Emulation.

is no mark or dash, then the tool does not address the challenge. In some cases the tools have prerequisites to work correctly. The emulator may require the analyst/user to figure out some of the challenges manually and pass the solution to the emulator to get past the challenge.

We provide some of the flow and common challenges faced during emulation in Figure 2, and Figure 3 though the figures do not encompass all the challenges that may be faced, with some challenges left off the figures all together for brevity. These figures are general flows and each bubble represents one or more challenges encountered through the process. The different challenges are further addressed in detail in Section 7, Section 8, and Section 9.

## 7 PRE-EMULATION

In Figure 2 we show the flow that a practitioner will usually explore during the Pre-Emulation stage of re-hosting a firmware. With each step indicating challenges that need addressed before continuing to address the next. The challenges presented here are similar to those presented by Costin [43]. Here we focus on the challenges of emulating and analyzing a single firmware, whereas Costin focuses on challenges for acquiring and analyzing thousands of firmwares available to download from the Internet automatically.

Before re-hosting a firmware, an analyst or practitioner will usually have a system they want to emulate or a firmware they want re-hosted. In some cases the system architecture is unknown or the analyst may not even have the firmware (e.g., when working on a bug bounty or proprietary hardware). Even after obtaining the system or firmware in mind, key information must be identified prior to re-hosting a firmware. Steps and challenges prior to setting up the emulator is what we refer to as the Pre-Emulation stage. This stage may also include verification of information and understanding gained prior to actual emulation (i.e., Disassembly, Initial Analysis, and CFG Recovery), though verification is not strictly necessary. We note that verification of correctness (which can include formal verification and/or behavioral verification) is useful when challenges in subsequent phases are encountered, as it narrows down where certain problems stem from.

The information required to begin emulation varies by emulation technique but includes obtaining firmware, determining memory layout, figuring out the instruction set architecture (ISA), identifying the processor, analyzing the binary, lifting/disassembly of firmware, and an initial firmware analysis. As a quick reference to the practitioner, different techniques that attempt to address the challenges present in Pre-Emulation are summarized in Table 1.

One of the main tools used to address these challenges is binwalk [139]. Binwalk is mostly used for extraction of the content from firmware images, but has other features that are useful. It can try

to determine ISA (not necessarily the processor), extract files from a blob, do a string search, find signatures such as common encryption formats, disassemble using capstone [22], calculate entropy, and perform binary diffing. Some of the other tools are mentioned in the subsequent subsections. A simple example of reverse engineering from a blob that mentions some of the challenges below was presented at BlackHat 2013 [41]. They present an end-to-end unpacking of firmware with some of their formats that may be helpful to reference for a newcomer in the field. Another helpful reference for IoT firmware based on OpenWrt is maintained by OWASP. They provide a platform to educate software developers and security professionals on vulnerabilities in IoT devices [121].

# 7.1 Obtaining Firmware

The first challenge to re-hosting firmware is obtaining the firmware. In the simplest case it can be downloaded from the vendor's website. If not directly available from the vendor, 3rd party sites, such as Github, have firmware available that has been used for academic research. Other ways to get firmwares include obtaining example firmwares from development boards that can be compiled with various operating systems and toolchains.

Downloading the firmware is not always possible, and even when possible, the firmware can have embedded proprietary file formats that are not easily extracted. For example, files can be compressed or contain firmware for multiple architecture files with final compilation of the firmware being done on the hardware during boot-loading. In some cases, firmware is combined with the operating system, such as the case of BMES or SPES types of systems, whereas for others downloaded firmware is only the user level application and the operating system kernel also must be obtained separately to perform full-system emulation as is sometimes the case for GPES. To overcome embedded unpacking issues, sometimes a network capture tool (*e.g.*, [31, 53, 55, 88, 106, 116, 117, 125, 130, 163, 165, 179]) connected to the actual hardware may be used to capture network traffic during a firmware update. The firmware is then extracted from the captured packet payloads.

In addition to downloading, firmware can sometimes be extracted from hardware. Vasile et al. [170] in their survey of hardware-based firmware extraction techniques showed a high percentage of systems expose UART interfaces that are sufficient to obtain firmware dumps. In addition to UART ports, debug ports (e.g., JTAG), and USB ports can be used to dump firmware [56, 186]. On some devices, a physical acquisition my be achieved by using the flash memory read command after reverse engineering the firmware update protocol in the bootloader [182]. If these ports are locked and secured, another option is to remove the memory from the circuit board and connect to another system to dump the firmware. Removing memories from the printed circuit boards comes at considerable risk of damaging or destroying the hardware. Using debug ports requires the debug port be present, and unlocked, both of which are increasingly considered poor security design.

Of the tools we surveyed, Firmadyne and CostinFA obtained firmware from vendor websites, whereas P<sup>2</sup>IM, angr, and Pretender used firmware available from a 3rd party vendor (Github). HALucinator and Pretender also used development examples from real embedded boards in their evaluation. For the case of Simics, QEMU, and Ghidra they are base emulator tools and not academic papers, hence they do not specify how to obtain firmware, expecting the user to have a firmware before using the tool. The other surveyed works did not specify how their firmware samples were obtained, just what the firmware was, or what the system was that they did emulation for.

The authors of Firmadyne developed and released a scraper that crawls embedded system vendors websites and downloads any firmware that they can identify. They then unpacked the firmwares in a generic way and if the firmware unpacked correctly, Firmadyne would continue with emulation, otherwise it would crash. Of the 23,035 firmwares Firmadyne scraped, they extracted 9,486 of them. Of those extracted, 1,971 were successful in naive emulation. The large percentage of failure (90%) shows obtaining and extracting firmware is a real challenge and is difficult to overcome in many

circumstances. CostinFA posted URL publicly that would try to unpack and analyze a firmware [42]. CostinFA collected an initial set of 759,273 files scraped from publicly accessible firmware update sites, and filtered that down to 172,751 potential firmware images. A sampled set of 32,356 images were then analyzed and 38 vulnerabilities were discovered [43], though it is unclear the level of emulation or re-hosting involved. Other resources that may be helpful in obtaining firmware include Python scraper tools and other open source repositories [59, 131, 142, 172]

#### 7.2 Instruction Set Architecture

After obtaining the firmware, it is necessary to determine what the instruction set architecture (ISA) the firmware uses so that the emulator can disassemble the firmware into the correct machine instructions, endianness (*e.g.*, little- or big-endian), and word-size. In addition to determining the ISA family (e.g ARM, PowerPC, X86, MIPS, ARM64, AVR, etc.), sometimes the ISA version is needed to correctly disassemble instructions *e.g.*, is it ARM with Thumb support and floating point instructions or not?

The ISA can most commonly be determined from a datasheet of the processor being emulated. If the hardware is unknown and a datasheet cannot be identified, static analysis techniques can be used. These techniques first try to determine if the file format is of a known file format (*e.g.*, ELF, PE2, Mach-O) using the file utility, then looking at other signatures in the firmware (*e.g.*, encryption, compression, etc.), or analyzing strings in the binary to guess the ISA. One well known tool that may help determine the ISA is binwalk [139]. Binwalk will use the capstone disassembler and try disassembling the binary for various types of ISA. If there are more than a specified number of instructions in a row (default 500) of a given architecture, then that is a strong candidate for the ISA. Of the tools surveyed, Firmadyne and CostinFA use binwalk and existing extraction tools to determine the ISA and then extract the filesystem, or extract the filesystem first and then determine the ISA – with the order of these two steps being highly specific to the firmware and analysis process at hand. Ghidra has headless scripts that can be run to try and determine the ISA (including one using binwalk), whereas angr provides the *boyscout* [5] tool that will try to determine the architecture and the endianess of the firmware. The other surveyed tools expect the ISA to be given to work correctly.

There is also recent research on using machine learning to classify ISA and endianness. These techniques usually rely on doing a binary similarity detection. They will use known architectures for training binaries, decomposing the binaries into smaller comparable fragments and transforming them to vectors to work with machine learning and stochastic gradient descent optimization methods. One such work by Clemens et al. [34] experiments on 16,785 different firmwares from 20 different architectures, and was accurate in classifying 17 of the architectures over 99% of the time, and the remaining 3 architectures (mips, mipsel, cuda) 50% of the time. De Nicolao et al. [49] leverages supervised sequential learning techniques to locate code section boundaries of binary files to help ease difficulty in analysis using a similar sized database for learning. Kairajärvi et al. [81] uses the ideas from both Clemens [34] and Nicolao [49] with improvements while using and publicly releasing a much larger and more balanced database for learning and testing. Other machine learning techniques that could be modified to determine the ISA are mentioned in [181] along with other machine learning techniques for binary analysis. These techniques require large datasets for training to be accurate and will only work as well as their training data.

If the above automated methods fail, the practitioner can attempt to manually identify the ISA by looking at signatures and strings in the firmware (certain compressions, signatures, copyrights, etc.) and/or brute force decompilation and performing an "eye" test on what looks promising.

#### 7.3 Determine Base Address

In order for the firmware to execute in an emulator, it must be loaded at the correct address(es). Determining the base address is difficult if the firmware being re-hosted is a binary-blob (e.g. just a binary with no symbols or metadata). The base address where the firmware should be loaded can sometimes be found by hardware datasheets (for firmware executing from internal memory). If source and compilation tools are available, base address information can be found in linker scripts.

Finding the base address is fundamental to many binary analysis techniques, and thus techniques to (try to) automatically determine it have been researched. Zhu et al. use strings and LDR instructions, comparing them and matching the offsets to determine the image base of the firmware [187, 188]. This is similar to the technique of listing the dwords occurring in a file with the list of strings in a file and lining up the distances between occurrences if possible. If there is a match, then subtracting the offsets will give you the image base address.

Firmalice [150] leverages jump tables in the binary by analyzing the jump table positions and the memory access pattern of indirect jump instructions. In a jump table there are a set of absolute code addresses which can give a better idea of where the firmware needs to be located at for the absolute addresses to work correctly. To find the jump tables, they scan through the binary for consecutive values that differ in their least significant two bytes. Finding the jump table is successful in many cases as jump tables are typically stored consecutively in memory. After finding the jump table, they then analyze all the indirect jumps found in the disassembly phase and the memory locations that they read their jump targets from. The binary is then relocated so that the maximum number of these accesses are associated with a jump table.

angr also attempts to determine the base address with their analysis script called *girlscout* [6]. This script will try to decide the base address by looking at functions and doing a statistical analysis to vote on the most likely base address. If automatic techniques do not work, the base address may be discovered by brute force guessing and checking, as most base addresses are multiples of powers of two.

In the case of Firmadyne and and CostinFA, the filesystem from the firmware is extracted after determining the ISA, and then the filesystem is used in a custom kernel given to QEMU. By using their own kernel, these tools bypass the need to determine the base address, but it also reduces the execution fidelity, as it does not execute the original kernel. For the other surveyed tools it is assumed the base address is provided by the practitioner.

## 7.4 Finding Entry Point

After determining the base address of the firmware, the practitioner needs to determine the entry point (*i.e.*, address from where to start execution). Entry point information can be encoded in the binary (*e.g.*, Executable Linker Format, ELF defines the entry point in metadata), or different analysis can be run to help give the practitioner entry point options.

For binary-blob firmware, angr, Ghidra, and IDA[136] have scripts that scan through the binary attempting to find function prologue instructions and function returns. From function information a directed function call graph can be generated and analyzed. Any root node of a weakly-connected component in the call graph can be treated as a potential entry point. Function call graph creation and analysis requires that you already know the ISA (so the function prologue, function epilogue, and call instructions can be analyzed). The call graph technique often returns multiple entry points, from which the correct entry point for emulation must be identified. Additionally, firmware will often have multiple valid entry points (*e.g.*, bootloader and interrupt service routines).

Instead of looking at the firmware to identify the entry point, some techniques rely on knowledge of the hardware they support to determine the entry point. For example, HALucinator targets ARM

Cortex-M devices. The Cortex-M architecture defines that the initial program counter's value be stored at address 0x4 on reset. Thus, HALucinator finds the entry point by looking at address 0x4. If the hardware is known, the datasheet will likely provide information about how the system begins execution.

For techniques that use a replacement kernel, as is the case for CostinFA and Firmadyne, finding the entry point challenge is essentially bypassed, as the entry point of the kernel is known because they built the kernel themselves. If the practitioner is dealing with a known operating system or compiler toolchain, the entry point function name may be specified (such as \_start or \_init). There are then techniques that can do function matching giving you the actual entry point. One such example is VxHunter[122] that will work for many firmwares with the VxWorks OS and compilation toolchain.

# 7.5 Determine Memory Layout

Determining the memory layout enables configuring where in the processors layout different types of memory are located. It sets the address for RAM, Flash, and MMIO. If the system is available with specifications, usually the memory layout can be determined from datasheets. For ARM systems, there may be a CMSIS-SVD file that also defines the memory layout. These files are in a specified format that can be loaded into a reverse engineering (RE) tool such as Ghidra or IDA and an automatic analysis can be run to update the memory layout [97]. Other types of files that sometimes specify memory layout include EDC files and hwconf files.

If no documentation exists and RE tools fail, physical examination of the components on the device that is being emulated may help to determine memory layout. Often markings and manufacture printing on the parts can be used to identify datasheets for the parts. If the memory layout is still unknown, the emulator can be over provisioned with memory (e.g., giving significantly more memory than the physical system) and trial and error must be used to determine where code is located and where external peripherals are, then these interactions are usually mapped into memory mapped IO. Of the surveyed tools, memory layout must be specified by the practitioner, though in some cases tools make it easier *e.g.*, Ghidra when CMSIS-SVD file is present.

## 7.6 Identify Processor and/or Board Support Package (BSP)

Depending on the fidelity the practitioner is targeting, often times identifying the exact processor is not necessary. As the case is with QEMU, the emulator only works off the ISA level features. For fidelity at the cycle level of emulation, tools such as gem5 [12] require knowing the exact processor as the same ISA instruction can be implemented differently at the cycle level for various processors. In QEMU, if a versatile machine is not used, there can also be errors, even if the ISA specified is correct.

In the case that the practitioner needs to solve the challenge of identifying the processor, solving memory layout may help. However, if the processor is known, often the documentation for the processor will specify the memory layout. If you have access to the hardware, most likely the processor will be labeled, solving the challenge.

If you do not have access to the hardware, the practitioner could do an aggressive instruction finding, followed by an analysis on how the instructions interact with memory. This analysis can then be compared against analysis on known processors to narrow down the processor candidates. This is still a manual process for the practitioner to then select and test different processors. If the vendor is known, projects that leverage known information from other reversed firmware may be used [138]. If the previous analysis are unsuccessful, the practitioner could run a brute force script to test all available processors in the base emulator. If still not successful, access to labeled

hardware is required. For surveyed works based off QEMU, identifying the processor is not strictly necessary in all cases, though if the QEMU target is not versatile it may be required.

# 7.7 Disassembly, Initial Analysis, and CFG Recovery

As mentioned at the beginning of Pre-Emulation, disassembly, initial analysis, and recovering the Control Flow Graph (CFG) are not strictly Pre-Emulation challenges. However, it is important to verify that the work the practitioner has performed and challenges addressed to this point in time are correct. Verification of previous work is perhaps skipped in some pipelines, but we have found that verification before continuing on to the next stages will save time and reduce headaches in the Emulation phase, *e.g.*, when multiple possible entry points (which may occur when there is a bootloader in addition to the main firmware under analysis), doing a validation and verification that you have the right entry point is worth the extra time to save the practitioner from wasting time re-hosting the bootloader that may not answer the emulation question at hand.

In the case that the practitioner has an idea of what the firmware is doing, such as is usually the case when the hardware is known, analyzing the CFG can help determine if the previous challenges such as base address, ISA, entry point are correct. When the CFG is recovered, it also conveys how well the disassembler and decompiler performed. This will give an idea of how successful emulation execution will be and/or the fidelity of emulation moving forward. Of the works surveyed, there are relatively few core disassemblers. angr uses capstone for parts of its disassembler, whereas QEMU and Ghidra use C/C++ to implement their disassembly. The other surveyed tools use a base emulator that will reuse one of these disassembly implementations. If the disassembler works perfectly, then the instructions have been disassembled correctly and the CFG can be recovered trivially if the control flow does not leave the main processor.

If the control flow leaves the main processor and goes to a co-processor (e.g., GPU or DSP) chip for initialization, it is near impossible to recover the CFG for what occurs in the co-processor. The practitioner at this point can try to determine what state and memory changes occur by comparing the state of memory before and after control is passed to the co-processor. If control flow leaves the emulated processor, fidelity of emulation is limited for that portion of the re-hosting, but in most cases is not a limiting factor in emulation.

If the hardware is not known and the practitioner does not have any idea of the control logic the firmware is trying to perform, disassembly and analysis can still be of use for validation. Disassembly will ensure the correct ISA is known and possibly help validate the processor. A control flow graph can still be created and analyzed to determine if there are valid flows throughout the graph, giving at least a weak reassurance that the base address and entry point are correct.

Disassembly and analysis are iterative, meaning the practitioner will perform the disassembly, then analyze the results in iterations. Between iterations, they will then modify the inputs and parameters to the disassembly slightly depending on the analysis results. This process will continue until the analysis results match what is expected from the practitioner. During this iteration process, there will be tweaks to the ISA, processor, base address, entry point, memory layout, etc. To solidify the ISA, processor and memory layout, the practitioner may analyze multiple firmwares for the same system concurrently, aggregating the analysis results to solidify results.

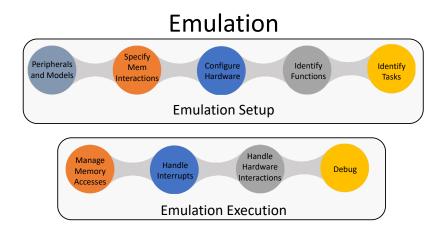

#### 8 EMULATION

In Figure 3 we show the flow that a practitioner will usually explore during Emulation setup and execution stages of re-hosting a firmware. The stages will usually be interspersed during iterations of emulator development. These challenges generally are not linear, but rather occur in different orders depending on the firmware being re-hosted.

Table 1. Pre-Emulation Challenges

| Paper/Technique           | Obtaining | Determine | Finding      | Finding     | Determine     | Identify  | Disassembly/ |

|---------------------------|-----------|-----------|--------------|-------------|---------------|-----------|--------------|

|                           | Firmware  | ISA       | Base Address | Entry Point | Memory Layout | Processor | Recover CFG  |

| angr [151]                |           | ~         | <b>✓</b>     | ~           |               | <b>/</b>  | ~            |

| Avatar <sup>2</sup> [112] |           |           |              |             |               |           | ~            |

| CostinFA [43, 44]         |           | ~         | _            | _           | _             | -         | ~            |

| Firmadyne [25]            | ~         | ~         | _            | _           | _             | -         | _            |

| Ghidra [119]              |           | ~         | ~            | ~           | <b>✓</b>      | ~         | ~            |

| HALucinator [35]          |           |           |              | _           |               |           | ~            |

| Muench2018 [113]          |           |           |              |             |               |           | ~            |

| $P^{2}IM$ [57]            |           |           |              |             |               |           | ~            |

| PANDA [50]                |           |           |              |             |               |           | ~            |

| Pretender [72]            |           |           |              |             |               |           | ~            |

| PROSPECT [84]             |           |           |              |             |               |           | ~            |

| QEMU [11]                 |           |           |              |             |               |           | ~            |

| Simics [105]              |           |           |              |             |               |           | ~            |

| SURROGATES [90]           |           |           |              |             |               |           | ~            |

| ARMX [146]                |           | _         | _            | _           | _             | -         | _            |

| BANG [75]                 |           | ~         | <b>✓</b>     | ~           | <b>✓</b>      | <b>✓</b>  | ~            |

| BAT [74]                  |           | ~         | ~            | <b>~</b>    | <b>✓</b>      | <b>✓</b>  |              |

| Binwalk [139]             |           | ~         | <b>✓</b>     | <b>✓</b>    | <b>✓</b>      | <b>✓</b>  |              |

| CLIK on PLCs [82]         |           |           |              |             |               |           | ~            |

| Datasheets                |           | ~         |              |             | <b>✓</b>      | ~         |              |

| Dtaint [26]               |           |           |              |             |               |           | ~            |

| Dytan [33]                |           |           |              |             |               |           | ~            |

| FIE [48]                  |           |           |              |             |               | _         | ~            |

| Firmalice [150]           |           | ~         | <b>✓</b>     | <b></b>     |               |           | ~            |

| firminsight [59]          | ~         | ~         |              |             | <b>✓</b>      |           |              |

| firmware-mod-kit [60]     |           | ~         | ~            | <b>/</b>    | <b>✓</b>      | <b>✓</b>  |              |

| firmwaredb [172]          | <b>/</b>  |           |              |             |               |           |              |

| FirmUSB [76]              |           |           |              |             |               | _         | ~            |

| HumIDIFy [167]            |           | ~         | ~            | <b>/</b>    | <b>✓</b>      | <b>✓</b>  |              |

| ICSREF [86]               |           | ~         | <b>✓</b>     | ~           | ~             | <b>✓</b>  | ~            |

| IDA-PRO [136]             |           | ~         | ~            | ~           | <b>✓</b>      | <b>✓</b>  | ~            |

| Inception [40]            |           |           |              |             |               |           | ~            |

| KLEE [19]                 |           |           |              |             |               |           | ~            |

| OFFDTAN [177]             |           |           |              |             |               |           | ~            |

| PIE: Parser [36]          |           |           |              |             |               |           | ~            |

| Radare2 [164]             |           | ~         | ~            | ~           | ~             | <b>✓</b>  | ~            |

| Scraper (python)          | <b>✓</b>  |           |              |             |               |           |              |

| subzero                   | ~         | ~         |              |             |               |           |              |

| Spedi [87]                |           | ~         | ~            | ~           | ~             | <b>✓</b>  | ~            |

| strings (linux command)   |           | ~         |              |             |               | <b>✓</b>  |              |

weans the tool attempts to address the given challenge. '—' means the tool bypasses this challenge, usually by the emulation technique used. A blank means the tool does not address the challenge. The first 14 entries in the table are bolded and are the main tools profiled in detail throughout.

After the practitioner has determined the processor, memory layout, entry point and base address of the firmware, verifying support in the base emulator is performed. Ideally the base emulator has support for the processor, if not, the practitioner will have to create a new specification for the base emulator. QEMU and Ghidra have instructions on how to add support for a new processor [114, 171]. After a base emulator is available, the next challenges can be addressed.

Overcoming the challenges in pre-emulation enables loading the firmware into the emulator and beginning execution. For the execution to be faithful to the real system, additional challenges must be overcome. We break these challenges into sub-categories—setup and execution. Setup

Fig. 3. Categorization and flow of some of the steps required for system emulation during Emulation Setup and Execution

challenges are usually done statically when the emulator is either paused or stopped whereas execution challenges are when the emulator is actually running. As a reference to the practitioner, we provide Table 2, but do not provide a reference table for the execution, as all the surveyed works attempt to overcome the given challenges.

## 8.1 Emulation Setup

After you have overcome the challenges in Pre-Emulation, now you need to determine how to handle configuration, external interactions and memory. Emulation setup encompasses these problems and is closely tied with the actual emulation execution. Setup is often iterative between execution stages, and with each iteration more knowledge is gained about the firmware and its dependencies on the emulator and peripherals. The emulator is improved and execution of the firmware is also iteratively performed. This continues until the question the analyst was trying to address has been answered.

As mentioned in Section 4.1, the scope of emulation may vary from a single chip or micro-controller to a subsystem or a large distributed system. The scope of emulation that is targeted will affect the challenges faced during emulation. The problems we discuss here are not all encompassing, though we believe it is a sufficient basis to demonstrate major challenges currently faced during the Emulation Setup phase.

8.1.1 Peripherals, External Hardware, and Modeling. Handling peripheral accesses is where a large amount of research is currently focused. Because of the variety of peripherals and vendors, it is likely the peripheral that is being accessed by the firmware is not implemented in the base emulator. Handling External Hardware and Peripheral interactions encompasses how to handle or represent interactions between the emulator and the peripherals. As mentioned in Section 7.5, statically determining the memory map will specify where the peripherals are located, not if they are used or when they are used. Dynamic analysis and execution can provide some of this information, discovering what peripherals are used when valid inputs for the given subset of peripherals analyzed. Depending on the fidelity of the peripheral model, i.e. the extent to which the peripherals are modeled, will constrain the dynamic execution to specific paths. Providing more realistic peripheral