IOP Publishing Nanotechnology

Nanotechnology 26 (2015) 055306 (5pp)

doi:10.1088/0957-4484/26/5/055306

# Laser direct synthesis of silicon nanowire field effect transistors

Woongsik Nam<sup>1,3</sup>, James I Mitchell<sup>1,3</sup>, Peide D Ye<sup>2,3</sup> and Xianfan Xu<sup>1,3</sup>

- <sup>1</sup> School of Mechanical Engineering, Purdue University, West Lafayette, IN 47907, USA

- <sup>2</sup> School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47907, USA

E-mail: xxu@purdue.edu

Received 8 October 2014, revised 28 November 2014 Accepted for publication 10 December 2014 Published 15 January 2015

### **Abstract**

We demonstrate a single-step, laser-based technique to fabricate silicon nanowire field effect transistors. Boron-doped silicon nanowires are synthesized using a laser-direct-write chemical vapor deposition process, which can produce nanowires as small as 60 nm, far below the diffraction limit of the laser wavelength of 395 nm. In addition, the method has the advantages of *in situ* doping, catalyst-free growth, and precise control of nanowire position, orientation, and length. Silicon nanowires are directly fabricated on an insulating surface and ready for subsequent device fabrication without the need for transfer and alignment, thus greatly simplifying device fabrication processes. Schottky barrier nanowire field effect transistors with a back-gate configuration are fabricated from the laser-direct-written Si nanowires and electrically characterized.

Keywords: nanowire, laser chemical vaport deposition, field effect transistor

(Some figures may appear in colour only in the online journal)

# 1. Introduction

Since Si and Ge nanowires were first synthesized via the vapor-liquid-solid mechanism [1], semiconductor nanowires have attracted a great deal of attention due to their demonstrated potential for high-performance nanoscale devices such as transistors [2], sensors [3], solar cells [4], and thermoelectric systems [5]. The ultra-thin bodies of nanowires allow excellent electrostatic control which is required for highperformance electronic devices. The one-dimensional morphology of nanowires enables straightforward implementation of semicylindrical gate or gate-all-around architectures. However, despite these advantages, the difficulty in controlling the placement and orientation of these nanowires remains an obstacle for widespread applications of nanowire devices. Since 'bottom-up' nanowires are often produced as entangled mesh, additional fabrication procedures are required to position them for device fabrication. Various alignment techniques [6-9] have been attempted and achieved successful integration of nanowires into individual devices or small-scale circuits, but none of them has demonstrated the capability to create the high density and precision required for integrated circuit manufacturing. Metal contamination from catalysts used for nanowire growth is another drawback. Alternative 'top-down' approaches do not have these shortcomings, but require complex, multiple fabrication steps for nanowire patterning, etching, and doping. Therefore, it will be meaningful to develop a simple and precise method to synthesize and position nanowires.

Material synthesis by laser heating has been demonstrated for photonic metamaterials [10], semiconductor pattern deposition [11], microelectronic [12, 13] and sensing applications [14]. Although these methods have advantages of flexibility and possible three-dimensional fabrication, the critical dimensions remained in the range of hundreds of nanometers due to the diffraction limit of light. On the other hand, it has been shown that direct writing of laser-induced periodic surface structures (LIPSS) can form feature sizes below the processing laser wavelength in nearly all kinds of materials [15–17], but the application of LIPSS has been limited to surface modification and material removal [18, 19].

In this work, we demonstrate a single-step method to fabricate doped silicon nanowires for silicon nanowire field effect transistors (SiNW FETs). Boron-doped silicon

1

<sup>&</sup>lt;sup>3</sup> Birck Nanotechnology Center, Purdue University, West Lafayette, IN 47907, USA

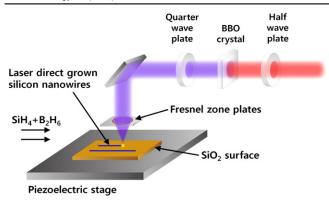

**Figure 1.** Schematic diagram of the laser-direct-write method. A laser beam is focused on a localized spot where a silicon nanowire is synthesized. Fresnel phase zone plates are used as a focusing element and there is a flow of silane and diborane in the laser CVD chamber.

nanowires are fabricated using a laser-direct-write chemical vapor deposition (CVD) method which we previously reported [20]. By combining laser synthesis of materials with the sub-diffraction feature sizes of LIPSS, our method overcomes scaling limitations of traditional laser-based CVD, resulting in nanowire diameters as small as 60 nm, far below the diffraction limit of the 395 nm laser wavelength we used. The method has advantages of both CVD and laser direct writing-in situ doping, catalyst-free growth, and precise control of nanowire position, orientation, and length. The silicon nanowires are directly deposited on an insulating SiO<sub>2</sub> surface and therefore ready for subsequent device fabrication without the need for transfer and alignment. SiNW FETs are fabricated from the laser-direct-written nanowires using standard micro-fabrication techniques. We characterize the electrical properties of fabricated FETs and demonstrate that our approach offers a simple and promising way to fabricate SiNW FETs.

# 2. Experimental details

Figure 1 shows a schematic diagram of the laser-direct-write CVD method. A laser beam is focused on a substrate to locally heat the surface and the thermal energy of the laser decomposes reactive gases on the laser spot. During the growth, the underlying substrate is translated by a piezoelectric stage to create silicon nanowires in a desired pattern. We used a femtosecond Ti:Sapphire laser which was frequency-doubled to 395 nm and Fresnel phase zone plates to focus the laser beam. Note that because the zone plates are flat and compact, they can be packed together in a small area and have potential for parallel writing of nanowires. The writing speed was  $0.5-2 \,\mu\mathrm{m \, s}^{-1}$ . The chamber pressure was  $2.5 \,\mathrm{Torr}$ with a flow rate of 10 sccm of 10% silane in argon and a flow rate of 0.025 sccm of 500 ppm diborane in hydrogen. The substrates used for nanowire growth were a 200 nm thick silicon dioxide top layer over a 200 nm thick polycrystalline silicon (poly-Si) layer on quartz. The silicon dioxide top layer provides electrical isolation of nanowires for easy fabrication of electrical devices, while the underlying poly-Si layer serves as a back gate. The poly-Si layer was heavily doped with phosphorus using ion implantation in advance for high conductivity. Further details of nanowire growth as well as the methods of zone plate fabrication can be found in [20].

Once silicon nanowires are synthesized using the laserdirect-write CVD method, the nanowires were annealed at 800 °C for 6 h in N2 to crystallize. Fabrication of nanowire FETs follows common micro-fabrication procedures. A contact hole was defined and etched on the 200 nm thick SiO<sub>2</sub> layer using buffered oxide etch (BOE) to create a contact to the underlying poly-Si layer which is used as a back gate. Ni source and drain contacts were then patterned and deposited by electron beam evaporation. Immediately before Ni evaporation, the patterned device chip was etched in BOE for 5 s to remove native oxide on the surface. The metalized devices were annealed at 350 °C in forming gas (4% H<sub>2</sub>/96% N<sub>2</sub>) for 1 min using rapid thermal annealing in order to form nickel silicide at the interfaces between the nanowires and the Ni electrodes. Electrical properties of the fabricated FETs were measured at ambient conditions with a Keithley 4200-SCS semiconductor parameter analyzer.

### 3. Results and discussion

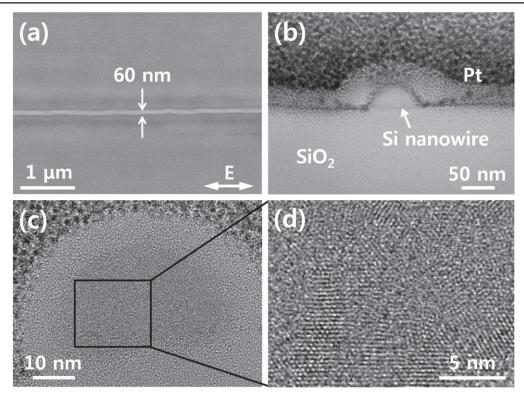

Figure 2(a) shows a scanning electron microscope (SEM) image of a Si nanowire synthesized using the laser-directwrite CVD method. The diameter of the nanowire is 60 nm, which is less than 1/6 of the laser wavelength of 395 nm. A horizontally polarized laser light was used because nanowires form parallel to the direction of laser polarization. We emphasize that our nanowire formation process is not a conventional laser CVD which is limited by the diffraction limit of light, but involves the interference effect between the incident laser beam and the surface scattered laser radiation within a diffraction limited spot, which causes spatially confined, periodic heating needed for nanowire synthesis. The mechanism of the nanowire synthesis has been described previously [20]. The nanowire has a semicircular crosssection with a height of around 30 nm as shown in the transmission electron microscopy (TEM) image in figure 2(b). No periodic atomic structure is observed in figure 2(b), indicating that the as-synthesized nanowire is amorphous. The silicon oxide layer under the nanowire is completely intact which demonstrates that laser irradiation during the nanowire formation causes no damage on the oxide surface. The platinum layers over the nanowire were deposited for TEM sample preparation. Figures 2(c) and (d) show crosssection TEM images of nanowire annealed in N2. Unintended oxidation of the outer shell of nanowire is observed in figure 2(c). To avoid oxidation, a nitrogen purge step was added before annealing and little oxidation in the nanowires was observed by comparing the diameters of nanowire before and after BOE etching. Grains of a few nanometers in size are observed in the annealed nanowire and this indicates that the nanowire was crystallized to poly-crystalline silicon.

**Figure 2.** (a) SEM image of a laser-direct-written Si nanowire. The white arrow indicates the electric field polarization direction of the incident laser. (b) Cross-section TEM images of an as-deposited nanowire and (c), (d) annealed nanowire. The annealed nanowire was crystallized to polycrystalline silicon with grain sizes of a few nanometers. The Pt layers over the nanowire were deposited for TEM sample preparation.

Crystallization of amorphous silicon to single-crystalline silicon is unlikely to occur unless the annealing temperature increases significantly [21].

The electrical resistivity of the nanowire annealed at 800 °C is measured to be 66  $\Omega$ cm using a four-point measurement which minimizes the effect of contact resistance. The resistivity corresponds to the doping concentration of  $2 \times 10^{14}$  cm<sup>-3</sup> in single-crystalline silicon [22]. However, the resistivity of poly-Si depends not only on doping concentration, but also on grain size, deposition method and temperature, and can be a few orders of magnitude greater than that of single-crystalline silicon due to carrier trapping states and dopant atom segregation in grain boundaries [23, 24]. Therefore, the doping concentration of  $2 \times 10^{14} \,\mathrm{cm}^{-3}$  is the lower limit of the doping concentration of our nanowire and the actual doping concentration can be as high as  $10^{17}\,\mathrm{cm}^{-3}$ [23, 24]. Note that the diborane/silane ratio during the nanowire synthesis was 1:80 000 and this ratio corresponds to the boron concentration of  $10^{17} \sim 10^{18} \, \text{cm}^{-3}$  if considering the ratio of boron and silicon atoms.

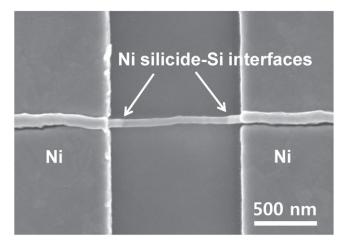

Figure 3 shows an SEM image of a fabricated SiNW FET. In our work, Ni was chosen as a contact metal because nickel silicides are widely used as contacts for semiconductor nanowires [25–27] and are considered as midgap metals with a hole Schottky barrier (SB) height of 0.39–0.49 eV [26–28]. Since Ni is the dominant diffusing species in the Ni–Si reaction [27], the growth of nickel silicide along the nanowire is observed adjacent to the Ni electrodes in figure 3. The Ni

**Figure 3.** SEM image of a SiNW FET. Ni source/drain contacts are deposited on a laser-direct-written Si nanowire. Rapid thermal annealing leads to the axial diffusion of Ni along the nanowire and nickel silicide forms near the Ni pads.

silicide areas are brighter than the remaining Si nanowire area. Elongation of a Si nanowire which is often caused by the incorporation of Ni in Si was not observed in our work due to the relatively short lengths of nickel silicide.

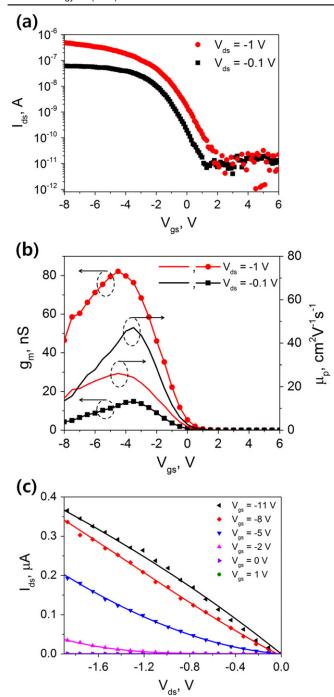

Figure 4(a) shows the transfer characteristics of a laser-direct-written SiNW FET with a channel length of  $1.8 \,\mu\text{m}$ . The drain current of the p-type device increases as a higher negative gate voltage is applied. Since the threshold voltage  $V_{\text{T}}$  is -0.91 V, determined by the linear extrapolation method,

**Figure 4.** (a) Transfer  $(I_{\rm ds}-V_{\rm gs})$  characteristics, (b) transconductance  $(g_{\rm m})$  and field-effect mobility  $(\mu_p)$  versus gate voltage  $(V_{\rm gs})$ , and (c) output  $(I_{\rm ds}-V_{\rm ds})$  characteristics of a laser-direct-written SiNW FET with a channel length of 1.8  $\mu$ m. Solid lines are a guide for the eye.

the device is mainly operated in accumulation-mode. No inversion-mode characteristic is observed with a positive gate voltage, which is most likely due to the much higher SB height between the p-type Si nanowire and the Ni silicide for electrons (0.66–0.75 eV) than for holes (0.39–0.48 eV) [26–28]. The on-off ratio is larger than  $10^4$  and the on-current reaches  $7.9 \,\mu\text{A} \,\mu\text{m}^{-1}$  at  $V_{\rm ds}$  = -1 V, which is within the same order of magnitude as on-current values previously reported in poly-Si NW FETs (12–40  $\mu\text{A} \,\mu\text{m}^{-1}$ ) [29, 30]. The on-

current of our device is normalized by the diameter of the semi-circular nanowire. The maximum transconductance is 81.2 nS  $(1.35 \,\mu\text{S}\,\mu\text{m}^{-1})$  at  $V_{\rm ds} = -1 \,\text{V}$  and 15 nS  $(0.25 \,\mu\text{S}\,\mu\text{m}^{-1})$  at  $V_{\rm ds} = -0.1 \,\text{V}$  as shown in figure 4(b). The drain-induced barrier lowering (DIBL), which is defined as  $\Delta V_{\rm gs}/\Delta V_{\rm ds}$  at  $I_{\rm ds} = 10^{-9} \,\text{A}$ , is measured to be 898 mV V<sup>-1</sup> and the subthreshold swing (SS) is 860 mV dec<sup>-1</sup>. The large DIBL and SS are in part attributed to the thick gate dielectric and SB transistor nature of the device.

The low-field mobility  $(\mu_p)$  is calculated to be  $47.4~{\rm cm}^2~{\rm V}^{-1}~{\rm s}^{-1}$  at  $V_{\rm ds}=-0.1~{\rm V}$  using the equation  $\mu_p=g_{\rm m}L^2/C_{\rm ox}V_{\rm ds}$  with  $g_{\rm m}$  as the maximum transconductance of the device, L as the channel length, and  $C_{\rm ox}$  as the gate capacitance. The 'metallic cylinder on an infinite metal plate model' is often used to calculate the gate capacitance in typical backgate NWFET geometries, yielding an analytical equation for the gate capacitance [31]:

$$C_{\rm ox} = \frac{2\pi\varepsilon_0\varepsilon_{r,\rm eff}L}{\ln(2t_{\rm ox}/r)},\tag{1}$$

where  $\varepsilon_{r,\text{eff}}$  is the effective dielectric constant of SiO<sub>2</sub>,  $t_{\text{ox}}$  is the thickness of the gate oxide, and r is the radius of the nanowire. However, equation (1) is inaccurate with the dielectric constant for SiO<sub>2</sub> of  $\varepsilon_r$  = 3.9 unless an infinitely long, metallic nanowire is completely surrounded by the gate oxide. Therefore, we use an effective dielectric constant of  $\varepsilon_r$ eff = 2.65, which is calculated for a triangular nanowire on SiO<sub>2</sub> [31], and the gate capacitance is calculated to be 102 aF. Note that although the extracted mobility is comparable to a previously reported value of 52.7 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> in poly-Si NW transistors [29], the intrinsic mobility value of our device should be even higher if we consider the contact resistance induced by the SBs at the silicon/silicide interfaces. Hence, the electrical performance of the SiNW FET can be further improved by either heavily doping the source/drain regions or using low SB silicides. For example, platinum silicide provides a low SB of 0.23 eV for holes [32] while erbium silicide has a low barrier height of 0.28 eV for electrons [33].

Figure 4(c) shows the drain current  $I_{\rm ds}$  versus drain voltage  $V_{\rm ds}$  characteristics of the SiNW FET. The device shows an enhancement-mode operation and non-saturated drain current is observed, indicating the presence of Schottky source/drain contacts. The non-saturated drain current can be explained using the thinning of the SB width induced by drain voltage [33, 34]. With a negative gate voltage, the SB width at the source contact becomes thinner as a drain bias increases. The thinner SB allows more tunneling of holes across the barrier and the increased number of holes injected from the source results in the increase of drain current without saturation. This non-saturation behavior of drain current in SB SiNW FETs has been previously reported [26, 34].

# 4. Conclusion

In this work, we have demonstrated fabrication of SiNW FETs using a laser-direct-write CVD method. Nanowires far

below the diffraction limit with widths of 60 nm were synthesized using our single-step, laser-based approach and fabricated into SiNW FETs using standard micro-fabrication techniques. The direct deposition of Si nanowires at a desired location on an insulating surface as well as *in situ* doping greatly simplify device fabrication processes and thus facilitate integration of Si nanowires into FET devices. The fabricated device functioned as a SB transistor and enhancement-mode, p-type characteristics were demonstrated. We believe that our approach could be an alternative to fabricate future nanowire electronics.

# **Acknowledgments**

We acknowledge the support of the Defense Advanced Research Projects Agency (Grant No. N66001-08-1-2037) and the National Science Foundation (Grant No. CMMI-1120577).

## References

- Morales A M and Lieber C M 1998 A laser ablation method for the synthesis of crystalline semiconductor nanowires *Science* 279 208–11

- [2] Cui Y and Lieber C M 2001 Functional nanoscale electronic devices assembled using silicon nanowire building blocks Science 291 851–3

- [3] Cui Y, Wei Q, Park H and Lieber C M 2001 Nanowire nanosensors for highly sensitive and selective detection of biological and chemical species *Science* 293 1289–92

- [4] Garnett E C and Yang P 2008 Silicon nanowire radial p-n junction solar cells J. Am. Chem. Soc. 130 9224-5

- [5] Hochbaum A I, Chen R, Delgado R D, Liang W, Garnett E C, Najarian M, Majumdar A and Yang P 2008 Enhanced thermoelectric performance of rough silicon nanowires *Nature* 451 163–8

- [6] Huang Y, Duan X, Cui Y, Lauhon L J, Kim K-H and Lieber C M 2001 Logic gates and computation from assembled nanowire building blocks Science 294 1313–7

- [7] Lee C H, Kim D R and Zheng X 2010 Orientation-controlled alignment of axially modulated pn silicon nanowires *Nano Lett.* 10 5116–22

- [8] Freer E M, Grachev O, Duan X, Martin S and Stumbo D 2010 High-yield self-limiting single-nanowire assembly with dielectrophoresis Nat. Nanotechnology 5 525–30

- [9] Yao J, Yan H and Lieber C M 2013 A nanoscale combing technique for the large-scale assembly of highly aligned nanowires *Nat. Nanotechnology* 8 329–35

- [10] Rill M S, Plet C, Thiel M, Staude I, von Freymann G, Linden S and Wegener M 2008 Photonic metamaterials by direct laser writing and silver chemical vapour deposition *Nat. Mater.* 7 543–6

- [11] Ishizu A, Inoue Y, Nishimura T, Akasaka Y and Miki H 1986 Direct writing of silicon lines by pyrolytic argon laser CVD Japan. J. Appl. Phys. 25 1830–3

- [12] McWilliams B M, Herman I P, Mitlitsky F, Hyde R A and Wood L L 1983 Wafer-scale laser pantography: fabrication of n-metal-oxide-semiconductor transistors and small-scale integrated circuits by direct-write laser-induced pyrolytic reactions Appl. Phys. Lett. 43 946-8

- [13] Baum T H and Comita P B 1992 Laser-induced chemical vapor deposition of metals for microelectronics technology *Thin* Solid Films 218 80–94

- [14] Nam W, Mitchell J I, Tansarawiput C, Qi M and Xu X 2013 Laser direct writing of silicon field effect transistor sensors Appl. Phys. Lett. 102 093504

- [15] Bonse J, Krüger J, Höhm S and Rosenfeld A 2012 Femtosecond laser-induced periodic surface structures J. Laser Appl. 24 042006

- [16] Huang M, Zhao F, Cheng Y, Xu N and Xu Z 2009 Origin of laser-induced near-subwavelength ripples: interferencee between surface plasmons and incident laser ACS Nano 3 4062-70

- [17] Öktem B, Pavlov I, Ilday S, Kalaycıoğlu H, Rybak A, Yavaş S, Erdoğan M and Ilday F Ö 2013 Nonlinear laser lithography for indefinitely large-area nanostructuring with femtosecond pulses *Nat. Photonics* 7 897–901

- [18] Halbwax M, Sarnet T, Delaporte P, Sentis M, Etienne H, Torregrosa F, Vervisch V, Perichaud I and Martinuzzi S 2008 Micro and nano-structuration of silicon by femtosecond laser: application to silicon photovoltaic cells fabrication *Thin Solid Films* 516 6791–5

- [19] Vorobyev A Y and Guo C 2008 Colorizing metals with femtosecond laser pulses Appl. Phys. Lett. 92 041914

- [20] Mitchell J I, Zhou N, Nam W, Traverso L M and Xu X 2014 Sub-diffraction laser synthesis of silicon nanowires Sci. Rep. 4 3908

- [21] Olson G L and Roth J A 1988 Kinetics of solid phase crystallization in amorphous silicon *Mater. Sci. Rep.* 3 1–78

- [22] Sze S M and Ng K K 2007 *Physics of Semiconductor Devices* (Hoboken, NJ: Wiley)

- [23] Seto J Y W 1975 The electrical properties of polycrystalline silicon films J. Appl. Phys. 46 5247–54

- [24] Fripp A L 1975 Dependence of resistivity on the doping level of polycrystalline silicon J. Appl. Phys. 46 1240–4

- [25] Wu Y, Xiang J, Yang C, Lu W and Lieber C M 2004 Singlecrystal metallic nanowires and metal/semiconductor nanowire heterostructures *Nature* 430 61–5

- [26] Weber W M et al 2006 Silicon-nanowire transistors with intruded nickel-silicide contacts Nano Lett. 6 2660–6

- [27] Tang W, Dayeh S A, Picraux S T, Huang J Y and Tu K-N 2012 Ultrashort channel silicon nanowire transistors with nickel silicide source/drain contacts *Nano Lett.* 12 3979–85

- [28] Bucher E, Schulz S, Luxsteiner M C, Munz P, Gubler U and Greuter F 1986 Work function and barrier heights of transition metal silicides Appl. Phys. A 40 71–7

- [29] Sheu J-T, Huang P-C, Sheu T-S, Chen C-C and Chen L-A 2009 Characteristics of gate-all-around twin poly-Si nanowire thin-film transistors *IEEE Electron Device Lett.* 30 139–41

- [30] Im M et al 2008 Multiple-gate CMOS thin-film transistor with polysilicon nanowire IEEE Electron Device Lett. 29 102–5

- [31] Wunnicke O 2006 Gate capacitance of back-gated nanowire field-effect transistors Appl. Phys. Lett. 89 083102

- [32] Fritze M, Chen C L, Calawa S, Yost D, Wheeler B, Wyatt P, Keast C L, Snyder J and Larson J 2004 High-speed Schottky-barrier pMOSFET with  $f_T$  = 280 GHz *IEEE Electron Device Lett.* **25** 220–2

- [33] Jang M, Oh J, Maeng S, Cho W, Lee S, Kang K and Park K 2003 Characteristics of erbium-silicided n-type Schottky barrier tunnel transistors Appl. Phys. Lett. 83 2611

- [34] Koo S-M, Edelstein M D, Li Q, Richter C A and Vogel E M 2005 Silicon nanowires as enhancement-mode Schottky barrier field-effect transistors *Nanotechnology* 16 1482–5