### FROM LAST TIME...

#### **Computer Systems**

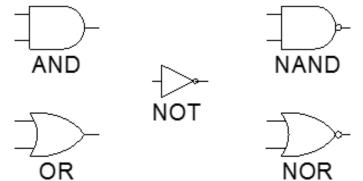

Implementing Boolean Logic

### UNIT 3: COMBINATIONAL LOGIC

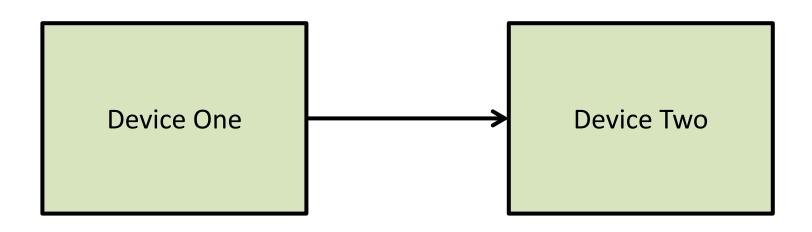

# IDEAL DEVICES ARE INSTANTANEOUS AND NOISE-FREE

- Device One sends a "o" ⇒ Device Two reads exactly "0"

- Device One sends a "1" ⇒ Device Two reads exactly "1"

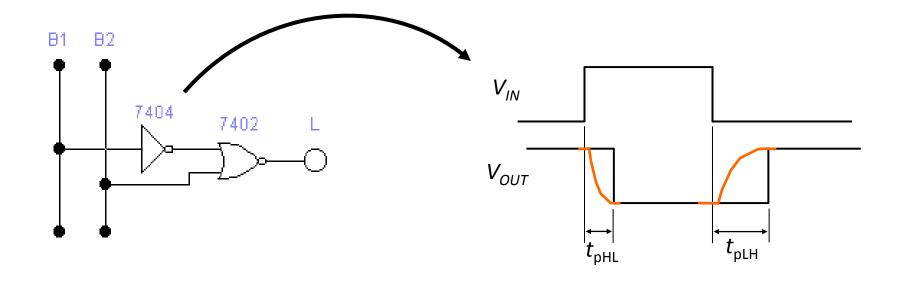

# REAL DEVICES EXPERIENCE PROPAGATION DELAY

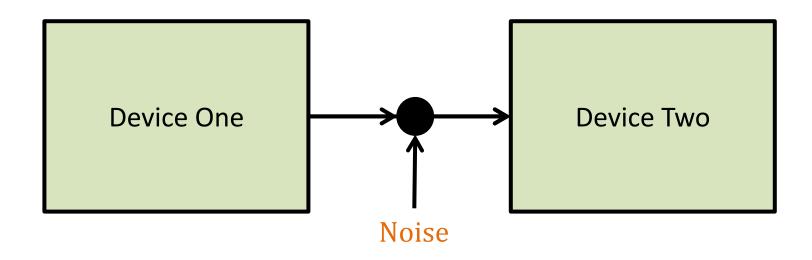

#### REAL DEVICES EXPERIENCE NOISE

- Device One sends a "o" ⇒ Device Two may read a "0" or "1"

- Device One sends a "1" ⇒ Device Two may read a "1" or "0"

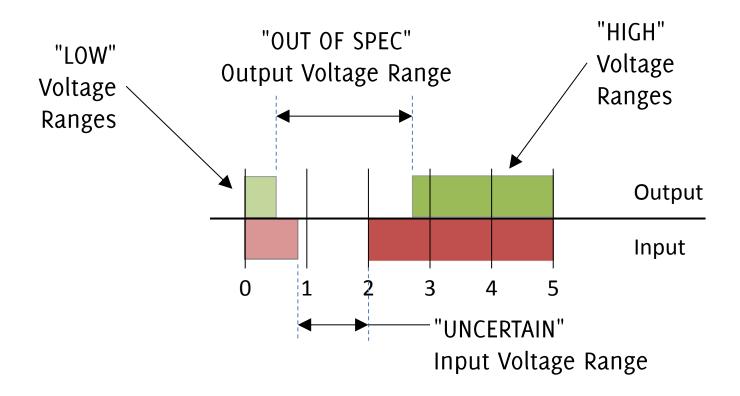

# VOLTAGE RANGES DEFINE LOGIC LEVELS FOR "o" AND "1"

# VOLTAGE RANGES DEFINE LOGIC LEVELS FOR "o" AND "1"

**Table 2–5** Characteristics of TTL families.

|                                     |                      |      | ·     |      | Fami  | ly   |       |       |

|-------------------------------------|----------------------|------|-------|------|-------|------|-------|-------|

| Description                         | Symbol               | 74   | 74L   | 74H  | 74S   | 74LS | 74AS  | 74ALS |

| Typical propagation delay (ns)      |                      | 9    | 33    | 6    | 3     | 9    | 1.6   | 5     |

| Power consumption per gate (mW)     |                      | 10   | 1     | 22   | 20    | 2    | 20    | 1.3   |

| Speed-power product (pJ)            |                      | 90   | 33    | 132  | 60    | 18   | 32    | 6.5   |

| LOW-level input voltage (V)         | $V_{ILmax}$          | 0.8  | 0.7   | 0.8  | 0.8   | 0.8  | 0.8   | 0.8   |

| LOW-level output voltage (V)        | $V_{OLmax}$          | 0.4  | 0.4   | 0.4  | 0.5   | 0.5  | 0.5   | 0.5   |

| HIGH-level input voltage (V)        | $V_{IHmin}$          | 2.0  | 2.0   | 2.0  | 2.0   | 2.0  | 2.0   | 2.0   |

| HIGH-level output voltage (V)       | $V_{OHmin}$          | 2.4  | 2.4   | 2.4  | 2.7   | 2.7  | 2.7   | 2.7   |

| LOW-level input current (mA)        | $I_{\rm ILmax}$      | -1.6 | -0.18 | -2.0 | -2.0  | -0.4 | -2.0  | -0.2  |

| LOW-level output current (mA)       | $I_{OLmax}$          | 16   | 3.6   | 20   | 20    | 8    | 20    | 8     |

| HIGH-level input current (µA)       | $I_{\mathrm{IHmax}}$ | 40   | 10    | 50   | 50    | 20   | 200   | 20    |

| HIGH-level output current $(\mu A)$ | $I_{\mathrm{OHmax}}$ | -400 | -200  | -500 | -1000 | -400 | -2000 | -400  |

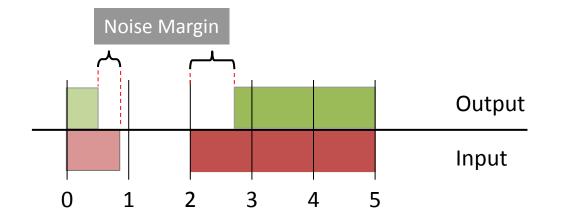

# NOISE MARGIN IS THE PEAK ALLOWABLE VOLTAGE VARIABILITY

- Binary o: Max. Output < Max. Input</p>

- Binary 1: Min. Output > Min. Input

# NOISE MARGINS VARY WITH DEVICE FAMILY

| Family.        |             | Guarantee         | Noise Margin |          |          |         |

|----------------|-------------|-------------------|--------------|----------|----------|---------|

| Family         | $V_{ m IH}$ | $V_{\mathrm{OH}}$ | $V_{ m IL}$  | $V_{OL}$ | High (1) | Low (0) |

| 74 TTL         | 2.0         | 2.4               | 0.8          | 0.4      | 0.4      | 0.4     |

| 74LS TTL       | 2.0         | 2.7               | 0.8          | 0.5      | 0.7      | 0.3     |

| 74ALS TTL      | 2.0         | 2.7               | 0.8          | 0.5      | 0.7      | 0.3     |

| 74F TTL (Fast) | 2.0         | 2.7               | 0.8          | 0.5      | 0.7      | 0.3     |

| Hi-Speed CMOS  | 3.5         | 4.9               | 1.0          | 0.1      | 1.4      | 0.9     |

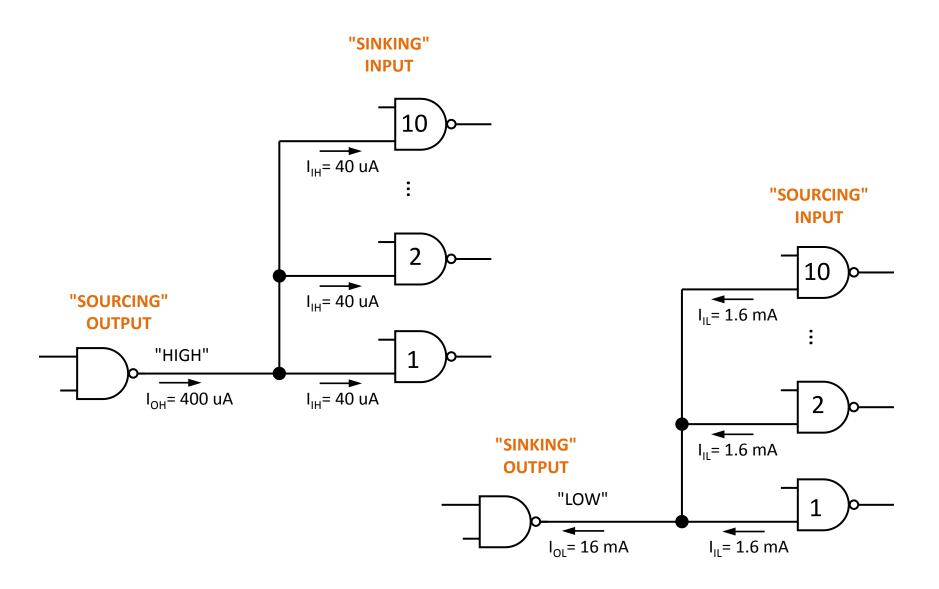

#### **FAN-OUT AND FAN-IN**

**Fan-In** – maximum number of inputs a logic gate can accept

**Fan-Out** – the maximum number of gate inputs a gate output can drive before logic levels are degraded beyond worst-case specifications

- Normally limited by current constraints

- TTL devices have a fan-out of between 2 and 10 other

TTL devices of the same type

- CMOS devices have a typical DC fan-out of 50 other CMOS devices.

#### DC SINKS AND SOURCES

"Sinking" Output

Provides a path to ground

"Sourcing" Output

Provides a path from voltage source

Devices often have unequal capacities for sinking and sourcing current

#### DC SINKS AND SOURCES

"Sourcing" Input

Provides a path from voltage source

"Sinking" Input

Provides a path to ground

Sinking and sourcing of current is a device-specific phenomenon

Table 2–5 Characteristics of TTL families.

|                                 |                      |      | Family |      |       |      |       |       |

|---------------------------------|----------------------|------|--------|------|-------|------|-------|-------|

| Description                     | Symbol               | 74   | 74L    | 74H  | 74S   | 74LS | 74AS  | 74ALS |

| Typical propagation delay (ns)  |                      | 9    | 33     | 6    | 3     | 9    | 1.6   | 5     |

| Power consumption per gate (mW) |                      | 10   | 1      | 22   | 20    | 2    | 20    | 1.3   |

| Speed-power product (pJ)        |                      | 90   | 33     | 132  | 60    | 18   | 32    | 6.5   |

| LOW-level input voltage (V)     | $V_{ILmax}$          | 0.8  | 0.7    | 0.8  | 0.8   | 0.8  | 0.8   | 0.8   |

| LOW-level output voltage (V)    | $V_{\mathrm{OLmax}}$ | 0.4  | 0.4    | 0.4  | 0.5   | 0.5  | 0.5   | 0.5   |

| HIGH-level input voltage (V)    | $V_{IHmin}$          | 2.0  | 2.0    | 2.0  | 2.0   | 2.0  | 2.0   | 2.0   |

| HIGH-level output voltage (V)   | $V_{\mathrm{OHmin}}$ | 2.4  | 2.4    | 2.4  | 2.7   | 2.7  | 2.7   | 2.7   |

| LOW-level input current (mA)    | $I_{\rm ILmax}$      | -1.6 | -0.18  | -2.0 | -2.0  | -0.4 | -2.0  | -0.2  |

| LOW-level output current (mA)   | $I_{OLmax}$          | 16   | 3.6    | 20   | 20    | 8    | 20    | 8     |

| HIGH-level input current (µA)   | $I_{\rm IHmax}$      | 40   | 10     | 50   | 50    | 20   | 200   | 20    |

| HIGH-level output current (µA)  | I <sub>OHmax</sub>   | -400 | -200   | -500 | -1000 | -400 | -2000 | -400  |

Currents going into device are considered positive

#### TTL SINKS AND SOURCES

Table 2-5 Characteristics of TTL families.

|                                 | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |      | ,     |      | Famil | y    |       |       |

|---------------------------------|-----------------------------------------|------|-------|------|-------|------|-------|-------|

| Description                     | Symbol                                  | 74   | 74L   | 74H  | 74S   | 74LS | 74AS  | 74ALS |

| Typical propagation delay (ns)  |                                         | 9    | 33    | 6    | 3     | 9    | 1.6   | 5     |

| Power consumption per gate (mW) |                                         | 10   | 1     | 22   | 20    | 2    | 20    | 1.3   |

| Speed-power product (pJ)        |                                         | 90   | 33    | 132  | 60    | 18   | 32    | 6.5   |

| LOW-level input voltage (V)     | $V_{ILmax}$                             | 0.8  | 0.7   | 0.8  | 0.8   | 0.8  | 0.8   | 0.8   |

| LOW-level output voltage (V)    | $V_{ m OLmax}$                          | 0.4  | 0.4   | 0.4  | 0.5   | 0.5  | 0.5   | 0.5   |

| HIGH-level input voltage (V)    | $V_{IHmin}$                             | 2.0  | 2.0   | 2.0  | 2.0   | 2.0  | 2.0   | 2.0   |

| HIGH-level output voltage (V)   | $V_{\mathrm{OHmin}}$                    | 2.4  | 2.4   | 2.4  | 2.7   | 2.7  | 2.7   | 2.7   |

| Input Sourcing current (mA)     | $I_{\rm ILmax}$                         | -1.6 | -0.18 | -2.0 | -2.0  | -0.4 | -2.0  | -0.2  |

| Output Sinking current (mA)     | $I_{OLmax}$                             | 16   | 3.6   | 20   | 20    | 8    | 20    | 8     |

| Input Sinking current (mA)      | I <sub>IHmax</sub>                      | 40   | 10    | 50   | 50    | 20   | 200   | 20    |

| Output Sourcing current (uA)    | I <sub>OHmax</sub>                      | -400 | -200  | -500 | -1000 | -400 | -2000 | -400  |

**Table 2–6** Characteristics of CMOS families operating with  $V_{\rm CC}$  between 4.5 and 5.5 V.

|                                             |                                 |                                                                               | Family                     |                            |                         |                         |

|---------------------------------------------|---------------------------------|-------------------------------------------------------------------------------|----------------------------|----------------------------|-------------------------|-------------------------|

| Description                                 | Symbol                          | Condition                                                                     | 74HC                       | 74HCT                      | 74AC                    | 74ACT                   |

| Typical propagation delay (ns)              | . 197                           |                                                                               | 18                         | 18                         | 5.25                    | 4.75                    |

| Quiescent power dissipation per gate (mW)   |                                 | $V_{\rm in} = 0$ or $V_{\rm CC}$<br>$V_{\rm in} = 2.4$ V                      | 0.0025<br>n/a              | 0.0025<br>12               | 0.005<br>n/a            | 0.005<br>7.5            |

| Power dissipation capacitance (pF)          | $C_{ m PD}$                     |                                                                               | 24                         | 24                         | 30                      | 30                      |

| Dynamic power dissipation per gate (mW/MHz) |                                 |                                                                               | 0.60                       | 0.60                       | 0.75                    | 0.75                    |

| Total power dissipation per gate (mW)       |                                 | f = 100  kHz<br>f = 1  MHz<br>f = 10  MHz                                     | 0.0625<br>0.6025<br>6.0025 | 0.0625<br>0.6025<br>6.0025 | 0.080<br>0.755<br>7.505 | 0.080<br>0.755<br>7.505 |

| Speed-power product (pJ)                    |                                 | f = 100  kHz<br>f = 1  MHz<br>f = 10  MHz                                     | 1.1<br>10.8<br>108         | 1.1<br>10.8<br>108         | 0.4<br>3.9<br>39        | 0.4<br>3.6<br>36        |

| Input leakage current (µA)                  | $I_{\mathrm{Imax}}$             | $V_{\rm in} = {\rm any}$                                                      | ±1                         | ±1                         | ±1                      | ±1                      |

| LOW-level input voltage (V)                 | $V_{\mathrm{ILmax}}$            |                                                                               | 1.35                       | 0.8                        | 1.35                    | 0.8                     |

| HIGH-level input voltage (V)                | $V_{ m IHmin}$                  |                                                                               | 3.85                       | 2.0                        | 3.85                    | 2.0                     |

| LOW-level output current (mA)               | $I_{ m OLmaxC}$ $I_{ m OLmaxT}$ | CMOS load<br>TTL load                                                         | 0.02<br>4.0                | 0.02<br>4.0                | 0.05<br>24.0            | 0.05<br>24.0            |

| LOW-level output voltage (V)                | $V_{ m OLmaxC} \ V_{ m OLmaxT}$ | $I_{\text{out}} \le I_{\text{OLmaxC}}$ $I_{\text{out}} \le I_{\text{OLmaxT}}$ | 90                         | 0.1<br>0.33                | 0.1<br>0.37             | 0.1<br>0.37             |

| HIGH-level output current (mA)              | $I_{ m OHmaxC}$ $I_{ m OHmaxT}$ | CMOS load<br>TTL load                                                         | 6                          | -0.02<br>-4.0              | -0.05<br>-24.0          | -0.05<br>-24.0          |

| HIGH-level output voltage (V)               | $V_{ m OHminC} \ V_{ m OHminT}$ | $ I_{\text{out}}  \le  I_{\text{OH}} $ $ I_{\text{out}}  \le  I_{\text{OH}} $ | 4.4<br>3.84                | 4.4<br>3.84                | 4.4<br>3.76             | 4.4<br>3.76             |

**Table 2–6** Characteristics of CMOS families operating with  $V_{\rm CC}$  between 4.5 and 5.5 V.

|                                             |                                   |                                                                                          |                  | Fai           | mily           |                |

|---------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------|------------------|---------------|----------------|----------------|

| Description                                 | Symbol                            | Condition                                                                                | 74HC             | 74НСТ         | 74AC           | 74ACT          |

| Typical propagation delay (ns)              | 200                               | 8 0 0                                                                                    | 18               | 18            | 5.25           | 4.75           |

| Quiescent power dissipation per gate (mW)   |                                   | $V_{\rm in} = 0 \text{ or } V_{\rm CC}$<br>$V_{\rm in} = 2.4 \text{ V}$                  | 0.0025<br>n/a    | 0.0025<br>12  | 0.005<br>n/a   | 0.005<br>7.5   |

| Power dissipation capacitance (pF)          | $C_{ m PD}$                       |                                                                                          | 24               | 24            | 30             | 30             |

| Dynamic power dissipation per gate (mW/MHz) |                                   |                                                                                          | 0.60             | 0.60          | 0.75           | 0.75           |

| Total power dissipation per gate (mW)       |                                   | f = 100  kHz<br>f = 1  MHz                                                               | 0.0625<br>0.6025 | 0.0625        | 0.080          | 0.080          |

| Speed-power product (pJ)                    |                                   | $ \begin{array}{c c} f \\ f \\ f \\ f = 10 \text{ MHz} \end{array} $                     | static           | powe          | r con          | sumpt          |

| Input leakage current (µA)                  | $I_{\mathrm{Imax}}$               | $V_{\rm in} = $ any                                                                      | ±1               | ±1            | ±1             | ±1             |

| LOW-level input voltage (V)                 | $V_{\mathrm{ILmax}}$              |                                                                                          | 1.35             | 0.8           | 1.35           | 0.8            |

| HIGH-level input voltage (V)                | $V_{ m IHmin}$                    |                                                                                          | 3.85             | 2.0           | 3.85           | 2.0            |

| LOW-level output current (mA)               | $I_{\rm OLmaxC}$ $I_{\rm OLmaxT}$ | CMOS load<br>TTL load                                                                    | 0.02<br>4.0      | 0.02<br>4.0   | 0.05<br>24.0   | 0.05<br>24.0   |

| LOW-level output voltage (V)                | $V_{ m OLmaxC} \ V_{ m OLmaxT}$   | $I_{\text{out}} \le I_{\text{OLmaxC}}$ $I_{\text{out}} \le I_{\text{OLmaxT}}$            | 0.1<br>0.33      | 0.1<br>0.33   | 0.1<br>0.37    | 0.1<br>0.37    |

| HIGH-level output current (mA)              | $I_{ m OHmaxC}$ $I_{ m OHmaxT}$   | CMOS load<br>TTL load                                                                    | -0.02<br>-4.0    | -0.02<br>-4.0 | -0.05<br>-24.0 | -0.05<br>-24.0 |

| HIGH-level output voltage (V)               | $V_{ m OHminC} \ V_{ m OHminT}$   | $ I_{\text{out}}  \le  I_{\text{OHmaxC}} $<br>$ I_{\text{out}}  \le  I_{\text{OHmaxT}} $ | 4.4<br>3.84      | 4.4<br>3.84   | 4.4<br>3.76    | 4.4<br>3.76    |

# EXCESS LOADING HAS NEGATIVE EFFECTS

Loading an output with more than rated fan-out or current capacity has the following effects:

- In the LOW state, the output voltage (V<sub>OL</sub>) may increase beyond the rated maximum

- In the HIGH state, the output voltage (V<sub>OH</sub>) may drop below the rated minimum

- The propagation delay from the input to the output may increase beyond the rated maximum

- The rise and fall time from LO-to-HI and HI-to-LO transition may increase beyond the rated maximum

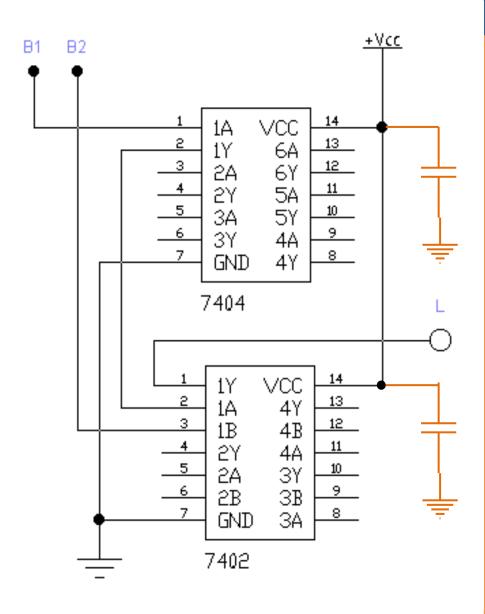

### **DECOUPLING CAPACITORS**

Provide local power to meet transient needs of ICs during operation

- As components operate, their need for current varies. These transients can cause component interaction through the power supply circuitry

- General rule of thumb: decoupling capacitor for each IC to be 0.01 0.1 μF

- Need to be placed across the +5 V and GND for each IC chip (with short leads!)

- More sophisticated approaches needed above 50 MHz

### A FLOATING INPUT CAN ACT AS AN ANTENNA

Never leave unused inputs unattached (floating), as they can pick up noise...

- To force a HI:

- for TTL, connect input to  $V_{CC}$  through a 1 k $\Omega$  resistor

- for CMOS, connect input directly to V<sub>CC</sub>

- To force a LO:

- connect inputs directly to digital ground

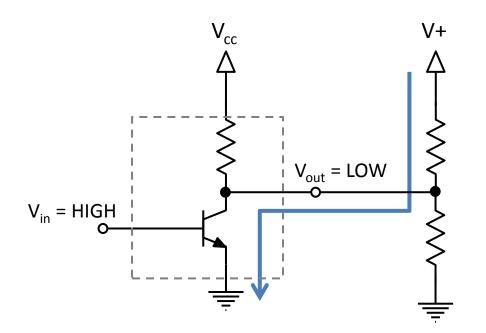

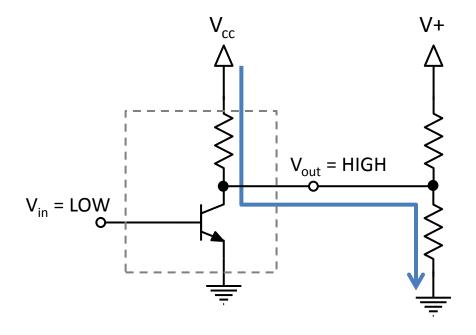

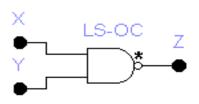

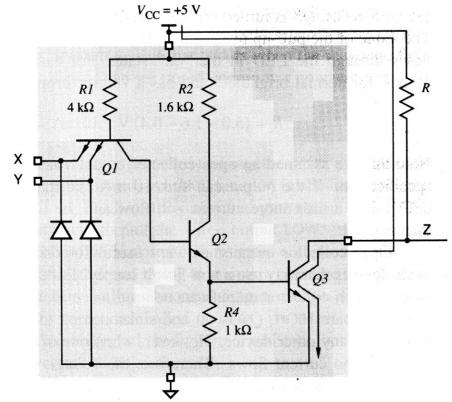

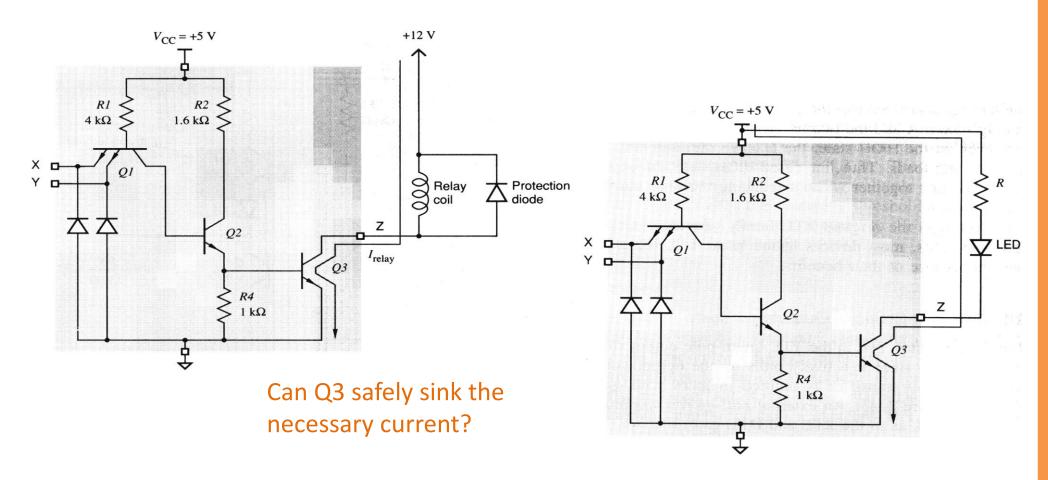

#### **OPEN COLLECTOR OUTPUT**

- Gate output without the active pull-up transistor. The output of the gate is the open collector terminal of the output transistor.

- To convert open collector output to voltage, an external pull-up resistor (on the order of 1 k $\Omega$ ) is used to connect the output to a 5 volt source.

- Pull-up resistor choice is lower bounded by the maximum allowable current sink of the device.

- Smaller pull-up for higher speed, but with higher power drain.

### **OPEN COLLECTOR OUTPUT**

Drive light-emitting diodes (LEDs), relays and other devices

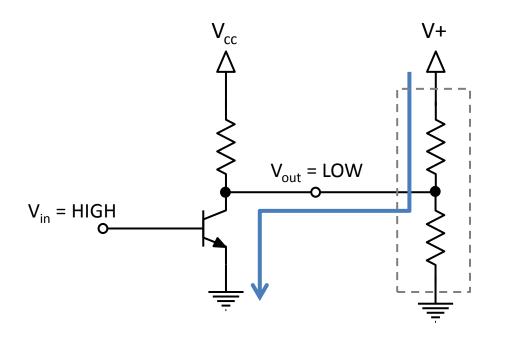

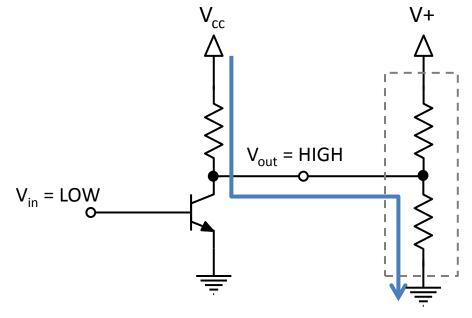

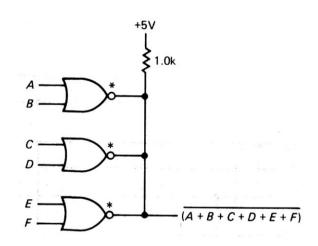

#### **OPEN COLLECTOR OUTPUT**

#### Wired Logic

Depends on the logic convention, a free AND/OR gate can be constructed by wiring the open collector outputs together

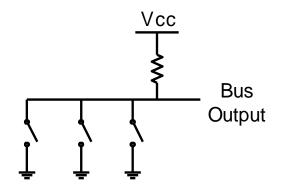

#### **Bus Connection**

Allowing several device to share an output wire. Any device that closes its switch determines the state of the output

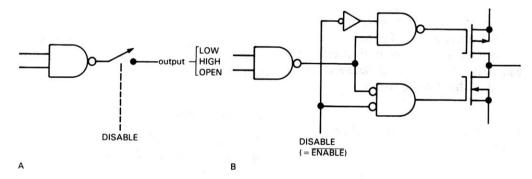

# THREE STATE OUTPUT DISCONNECTS DEVICE FROM BUS

Figure 8.19. Three-state CMOS NAND gate. A. Conceptual diagram. B. Realization with internal CMOS gates.

- When disconnected, the device is referred to as being in the high impedance state – Does not mean three logic states!

- Uses a separate ENABLE input to determine the status of the output

a more complicated circuit

- More noise immune and faster than open collector outputs. Also called Tri-State Logic (trade name of Nat'l Semiconductor)

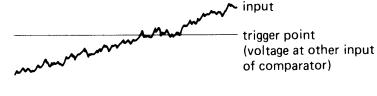

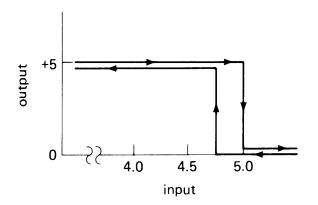

### **SCHMITT TRIGGER**

1-bit analog-to-digital conversion

- The "converter" is the switching device

- Sharp switching boundary can cause multiple switches if there are oscillations in the analog signal

Schmitt trigger uses a boundary defined with hysteresis to minimize the switching transients

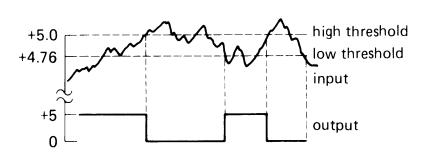

### **SCHMITT TRIGGER**

7414 – Hex Inverter with Schmitt Trigger Inputs

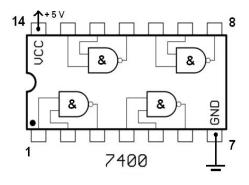

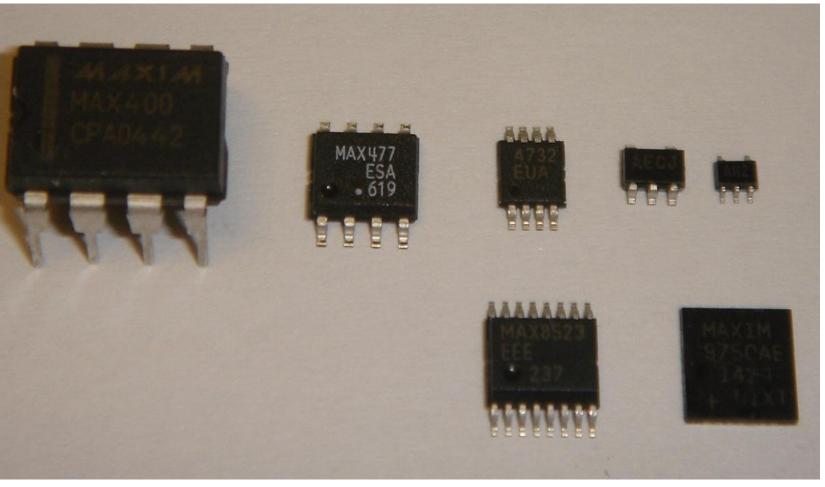

# INTEGRATED CIRCUIT (IC) PACKAGES

DIP (Dual Inline Package)

SMD (Surface Mount Device)

Image: https://i.cmpnet.com/planetanalog/2006/04/C0039-Figure%201.jpg

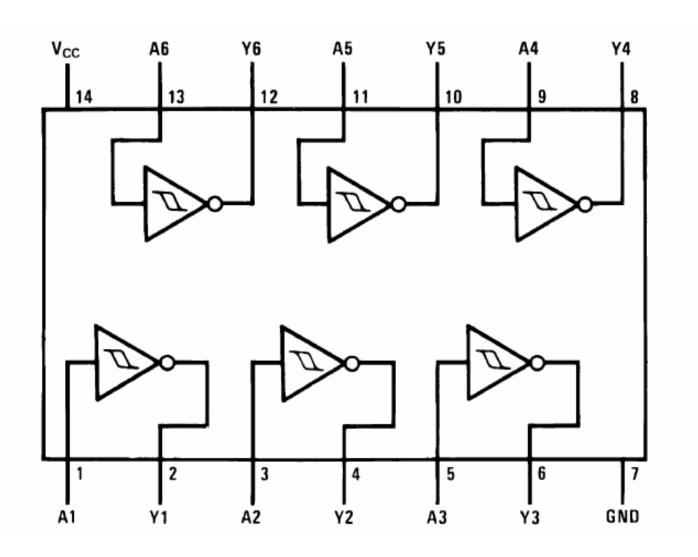

#### INTEGRATED CIRCUITS

One or more gates fabricated on a single silicon chip:

#### **Small-Scale Integration (SSI)**

- 1 to 20 gates, basic building blocks of digital design

- Uses dual in-line package (DIP), standard pinout for 7400 series ICs

- Gradually been replaced by programmable logic devices (PLDs)

#### Medium-Scale Integration (MSI)

- 20 to 200 gates

- Functional building blocks, e.g. decoder, multiplexer, counter, ...

#### Large-Scale Integration (LSI)

- 200 to 20,000 gates

- Memories, microprocessors, PLDs, ...

#### **Very Large-Scale Integration (VLSI)**

Any thing above 500,000 transistors

# WHY PROGRAMMABLE LOGIC DEVICES?

- Electronic systems often consist of a few small logic circuits that "glue" together large-scale ICs. Not infrequently, the precise system configuration needs to be "tweaked" to account for application-specific inputs or data formatting.

- Programmable logic devices (PLDs) allow systems to be easily configured, often late in the design cycle. Rather than possessing a fixed function at the time of manufacture, a PLD must be "programmed" prior to use.

- Very fast much faster than a microcontroller.

#### COMING UP...

#### **Computer Systems**

- Programmable devices

- Sequential logic

- Finite state machines