June 18 – 20, 2012 The Pennsylvania State University University Park, Pennsylvania

# DEVICE RESEARCH CONFERENCE

Conference Digest

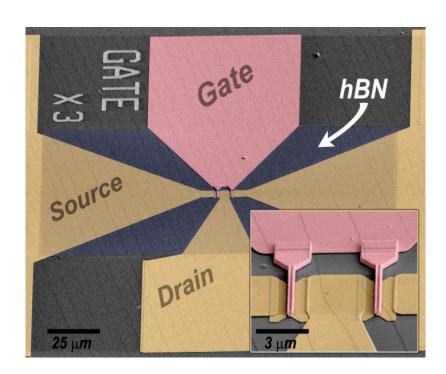

**Front Cover Image**: False color SEM image of a high frequency graphene FET utilizing h-BN as the dielectric material. © 2012 Penn State

Copyright and Reprint Permission: Abstracting is permitted with credit to the source. Libraries are permitted to photocopy beyond the limit of U.S. copyright law for private use of partrons those articles in this volume that carry a code at the bottom of the first page, provided the per-copy fee indicated in the code is paid though Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923. For other copying, reprint or republication permission, write to IEEE Copyrights manager, IEEE Operations Center, 445 Hoes lane, P.O. Box 1331, Piscataway, NJ 08855-1331. All rights reserved. Copyright ©2012 by the Institute of Electrical and Electronics Engineers, Inc.

IEEE Catalog Number: CFP12DRC-CDR

ISBN: 978-1-4673-1161-8

ISSN: 1548-3770

June 18 – 20, 2012 The Pennsylvania State University University Park, PA

# DEVICE RESEARCH CONFERENCE

#### **OFFICERS**

| Miguel Urteaga   | General Program Chair        |

|------------------|------------------------------|

| Suman Datta      | Technical Program Chair      |

| Ioannis Kymissis | Technical Program Vice Chair |

| Tom Jackson      | Treasurer                    |

## **Technical Program Committee**

Seth Bank, University of Texas Austin Brian Doyle, Intel Corporation Dan Green, ONR Avik Ghosh, University of Virginia Yongtaek Hong, Seoul National University Mantu Hudait, Virginia Tech Debdeep Jena, University of Notre Dame Andy Kent, NYU Siyuranga Koswatta, IBM Corporation Ioannis Kymissis, Columbia University Kirsten Moselund, IBM Zurich Mikael Östling, KTH Jamie Phillips, University of Michigan Eric Pop, University of Illinois Urbana-Champaign Joshua Robinson, Penn State University Sayeef Salahuddin, University Of California, Berkeley Michael Schlectweg, Fraunhofer IAF Yanning Sun, IBM Mitsuru Takenaka, University of Tokyo

Sponsored by the IEEE Electron Devices Society

June % - 2\$, 201& The DYbbgmj Ub]U GHJHY I b]j Yfg]hm I b]j Yfg]hmDUf\_ž D5

# DEVICE RESEARCH CONFERENCE

IEEE Catalog Number: CFP12DRC-CDR

ISBN: 978-1-4673-1161-8

ISSN: 1548-3770

# **Schedule of Events**

| SUNDAY PM, JUNE 17 <sup>TH</sup> , 2012             |    |

|-----------------------------------------------------|----|

| Check-In/RegistrationLocation                       |    |

| Welcoming Reception Location                        |    |

| MONDAY AM, JUNE 18 <sup>TH</sup> , 2012             |    |

| Check-In/Registration                               |    |

| Plenary SessionLocation                             |    |

| Buffet LunchLocation                                |    |

| MONDAY PM, JUNE 18 <sup>TH</sup> , 2012             |    |

| Session II.A. CMOS Plus: MEMS, Sensors and Ha       |    |

| Session II.B. Alternate Transistor ConceptLocation  |    |

| Session III. Poster Session & Reception<br>Location |    |

| TUESDAY AM, JUNE 19 <sup>TH</sup> , 2012            | 2  |

| Check-In/RegistrationLocation                       |    |

| Session IV.A. Wide Bandgap/High Speed               |    |

| Session IV.B. 1/2-Dimensional FETsLocation          |    |

| Buffet LunchLocation                                |    |

| TUESDAY PM, JUNE 19TH, 201                          | 12 |

| Session V.A. III-V MOSFETs/FETsLocation             |    |

| Session V.B. Spin/Memory Devices<br>Location        |    |

| Tours of Millenium Science Building<br>Locations    |    |

| Conference Banquet Location                         |    |

# TUESDAY PM, JUNE 19TH, 2012

| Rump Sessions  I. Wells vs. Sheets vs. Tubes Location |               |

|-------------------------------------------------------|---------------|

| II. Heterogeneous Integration Location                | Senate Suites |

| WEDNESDAY AM, JUNE 20TH                               | , 2012        |

| Check-In/Registration                                 |               |

| Joint EMC/DRC Plenary Session<br>Location             |               |

| Session VI.A. Transistor Modeling<br>Location         |               |

| Session VI.B. Thin Film DevicesLocation               |               |

| WEDNESDAY PM, JUNE 20TH                               | , 2012        |

| Session VII.A. Optoelectronic DevicesLocation         |               |

| Session VII.B. Biological Devices                     | 1:30 PM       |

# **Table of Contents**

| Session           | 1-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I1<br>8:50 AM     | Mapping a Path to the Beyond-CMOS Technology for Computation I. A. Young, Components Research, Intel Corporation, Hillsboro, Oregon, USA                                                                                                                                                                                                                                                                                                                                                                                              |

| I2<br>10:10A M    | Solid-State Electronics and Single-Molecule Biophysics K. Shepard, Department of Electrical Engineering, Columbia University, New York, New York, USA                                                                                                                                                                                                                                                                                                                                                                                 |

| I3<br>11:10 AM    | Advanced Device Technologies for Defense Systems J. C. Zolper, Raytheon Company, Waltham, Massachusetts, USA                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Session           | n II.A. MEMS, SENSORS and HARVESTORS 13-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

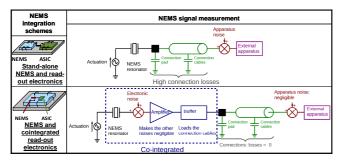

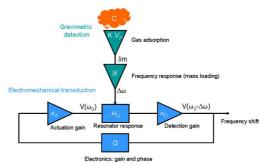

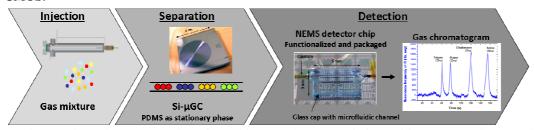

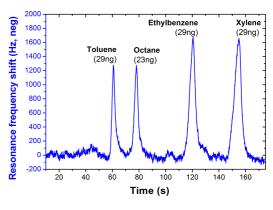

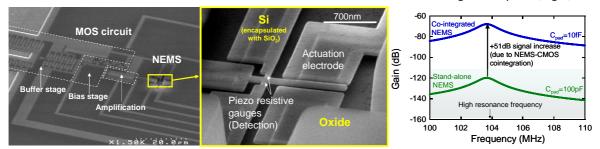

| II.A-1<br>1:30 PM | High performance miniaturized NEMS sensors Toward co-integration with CMOS?  T. Ernst, J. Arcamone, J. Philippe, O. Martin, E. Ollier, P. Batude, V. Gouttenoire, C. Marcoux, F. Ricoul, C. Dupré, E. Colinet, O. Rozeau, G. Billiot, and L. Duraffourg, CEA, LETI, MINATEC Campus, Grenoble, FRANCE                                                                                                                                                                                                                                  |

| II.A-2<br>2:10 PM | Silicon Monolithic MEMS + Photonic Systems S. A. Bhave, OxideMEMS Lab, Cornell University, Ithaca, New York, USA                                                                                                                                                                                                                                                                                                                                                                                                                      |

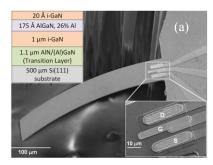

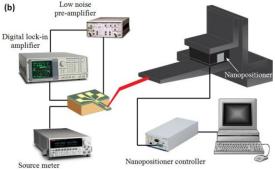

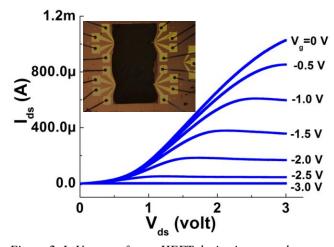

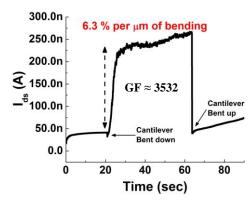

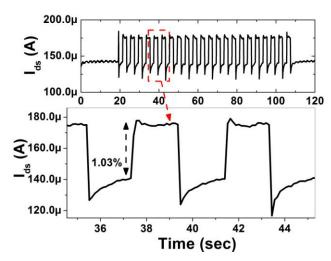

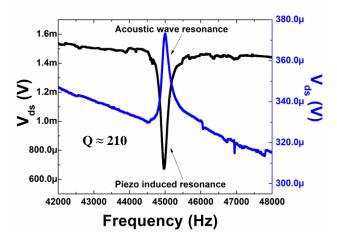

| II.A-3<br>2:50 PM | Highly Sensitive III-V Nitride Based Piezoresistive Microcantilever Using Embedded AlGaN/GaN HFET as Ultrasonic Detector  A. Talukdar <sup>1</sup> , M. Qazi <sup>2</sup> , and G. Koley <sup>1</sup> , <sup>1</sup> University of South Carolina, Columbia, South Carolina, USA and <sup>2</sup> Intel Corp., Portland, Oregon, USA                                                                                                                                                                                                  |

| II.A-4<br>3:30 PM | Nanostructured thermoelectric energy conversion and refrigeration devices  A. Shakouri, Birck Nanotechnology Center, Purdue University, West Lafayette, Indiana, USA                                                                                                                                                                                                                                                                                                                                                                  |

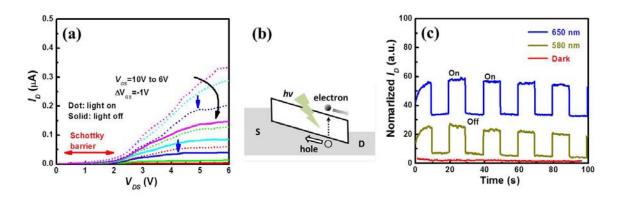

| II.A-5<br>4:10 PM | Piezotronics and Piezo-phototronics  Z. L. Wang, School of Materials Science and Engineering, Georgia Institute of Technology, Atlanta, Georgia, USA                                                                                                                                                                                                                                                                                                                                                                                  |

| II.A-6<br>4:50 PM | Late News                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Session           | 1 II.B. ALTERNATE TRANSISTOR CONCEPT 25-38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

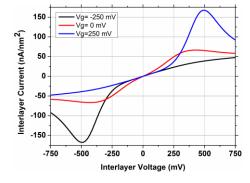

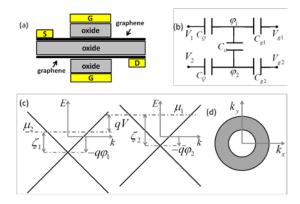

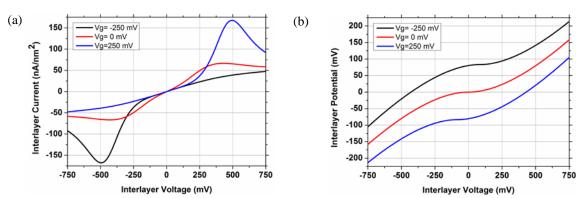

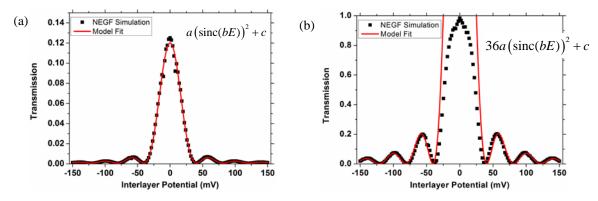

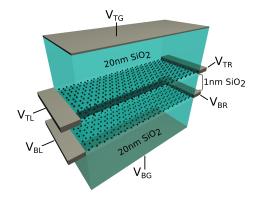

| II.B-1<br>1:30 PM | <b>Novel Double Layer Graphene Transistors-Bilayer Pseudospin FETs and 2D-2D Tunnel FETs</b> S. K. Banerjee <sup>1</sup> , L. F. Register <sup>1</sup> , E. Tutuc <sup>1</sup> , D. Reddy <sup>1</sup> , S. Kim <sup>1</sup> , D. Basu <sup>1</sup> , C. Corbet <sup>1</sup> , L. Colombo <sup>2</sup> , G. Carpenter <sup>3</sup> and A. H. MacDonald <sup>1</sup> , <sup>1</sup> University of Texas at Austin, <sup>2</sup> Texas Instruments, Incorporated, Dallas, Texas, USA, and <sup>3</sup> IBM Research, Austin, Texas, USA |

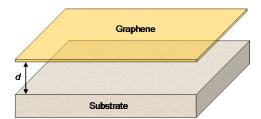

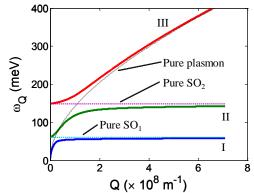

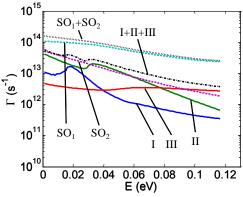

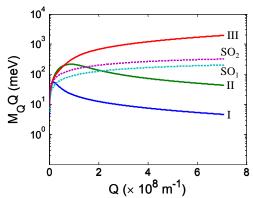

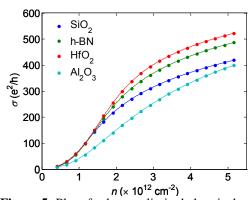

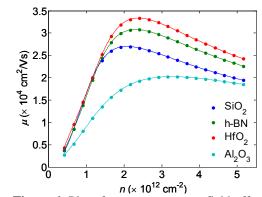

| II.B-2<br>2:10 PM | Effect of Interfacial Phonon-Plasmon Modes on Electrical Transport in Supported Graphene ZY. Ong and M. V. Fischetti, Department of Materials Science and Engineering, University of Texas at Dallas, Richardson, Texas, USA                                                                                                                                                                                                                                                                                                          |

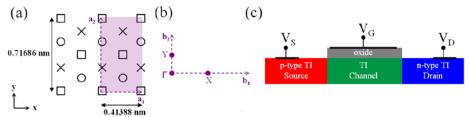

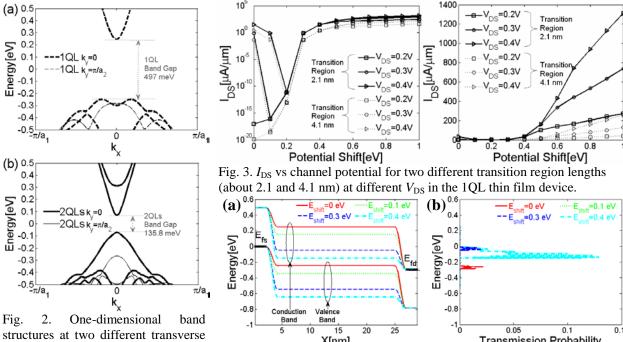

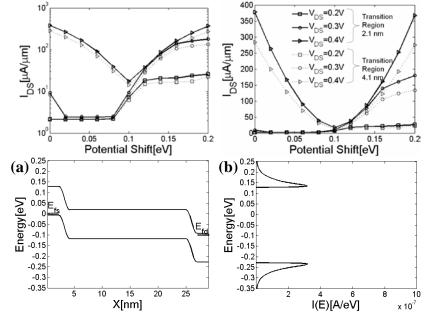

| II.B-3<br>2:30 PM | Possible Applications of Topological Insulator Thin Films for Tunnel FETs J. Chang, Leonard F. Register, and S. K. Banerjee, Microelectronics Research Center, The University of Texas at Austin, Austin, Texas, USA                                                                                                                                                                                                                                                                                                                  |

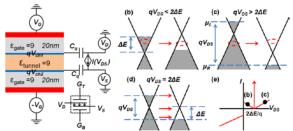

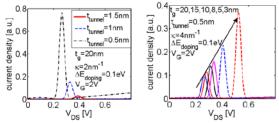

| II.B-4<br>2:50 PM | <b>SymFET: A Proposed Symmetric Graphene Tunneling Field Effect Transistor</b> P. Zhao <sup>1</sup> , R. M. Feenstra <sup>2</sup> , G. Gu <sup>3</sup> and D. Jena <sup>1</sup> , <sup>1</sup> Department of Electrical Engineering, University of Notre Dame, Notre Dame, Indiana, USA, <sup>2</sup> Dept. Physics, Carnegie Mellon University, Pittsburgh, Pennsylvania, USA and <sup>3</sup> Dept. Electrical Engineering and Computer Science, University of Tennessee, Knoxville, Tennessee, USA                                 |

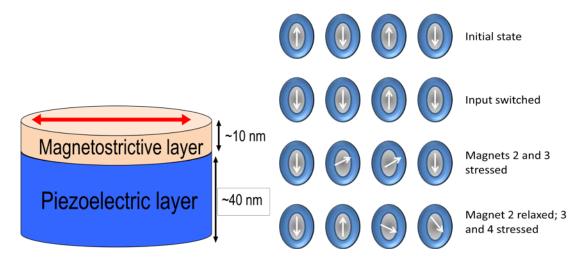

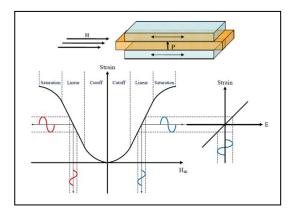

| II.B-5<br>3:30 PM | Hybrid straintronics and spintronics: An ultra energy-efficient paradigm for logic and memor S. Bandyopadhyay <sup>1</sup> and J. Atulasimha <sup>2</sup> , <sup>1</sup> Department of Electrical and Computer Engineering and of Mechanical and Nuclear Engineering, Virginia Commonwealth University, Richmond, Virginia, U | <sup>2</sup> Department |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

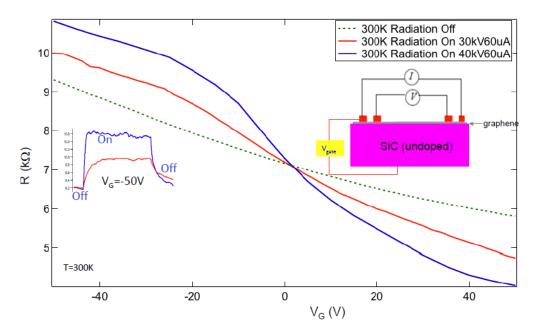

| II.B-6<br>4:10 PM | <b>Graphene and Topological Insulator Based Transistors: Beyond Computing Applications</b> Y. P. Chen, Department of Physics and Birck Nanotechnology Center and School of Electrical and Engineering, Purdue University, West Lafayette, Indiana, USA                                                                        | Computer                |

| II.B-7<br>4:50 PM | Late News                                                                                                                                                                                                                                                                                                                     |                         |

| Sassio            | n III Poster Session                                                                                                                                                                                                                                                                                                          | 30_1/18                 |

#### Session III. Poster Session

39-148

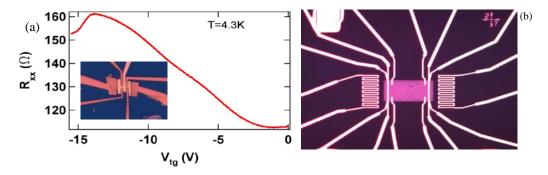

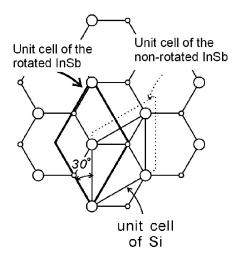

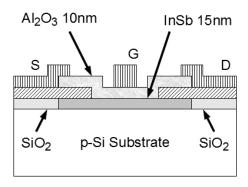

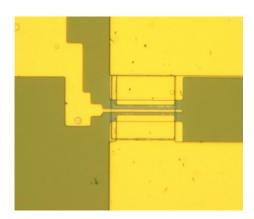

- III-1 Al<sub>2</sub>O<sub>3</sub>/InSb/Si Quantum Well MOSFETs Having an Ultra-Thin InSb Layer

K. Maezawa<sup>1</sup>, T. Ito<sup>1</sup>, A. Kadoda<sup>1</sup>, K. Nakayama<sup>1</sup>, Y. Yasui<sup>1</sup>, M. Mori<sup>1</sup>, E. Miyazaki<sup>2</sup> and T. Mizutani<sup>2</sup>,

<sup>1</sup>University of Toyama, Gofuku, Toyma, JAPAN and <sup>2</sup>Nagoya University, Furo-cho, Chikusa-ku, Nagoya, JAPAN

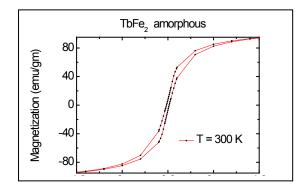

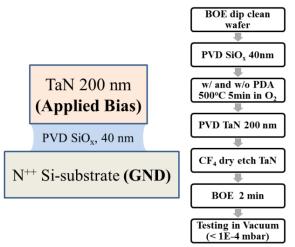

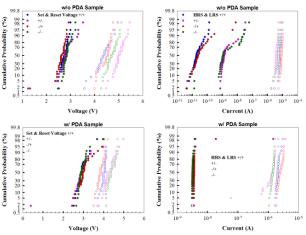

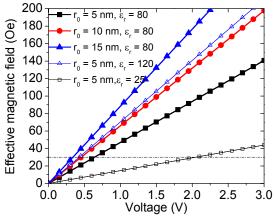

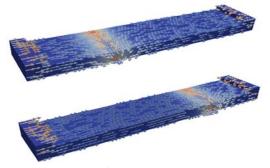

- III-2 **Ultra-Sensitive Magnetoelectric Sensor with High Saturation Field**L. Mei, Z. Fang, F. Li, S. Datta, and Q. M. Zhang, Department of Electrical Engineering, The Pennsylvania State University, University Park, Pennsylvania, USA

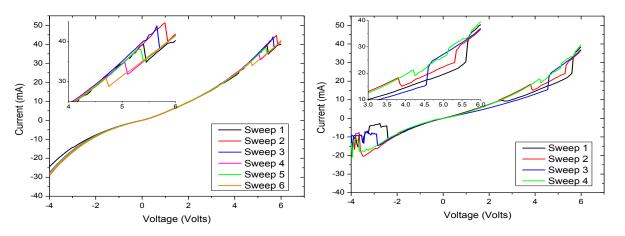

- III-3 Study of SiO<sub>x</sub>-based Complementary Resistive Switching Memristor

Y.-F. Chang<sup>1</sup>, Y.-T. Chen<sup>1</sup>, F. Xue<sup>1</sup>, Y. Wang<sup>1</sup>, F. Zhou<sup>1</sup>, B. Fowler<sup>2</sup>, and J. C. Lee<sup>1</sup>, <sup>1</sup>Microelectronics

Research Center, Department of Electrical and Computer Engineering, The University of Texas at Austin,

Austin, Texas, USA and <sup>2</sup>PrivaTran, LLC, Austin, Texas, USA

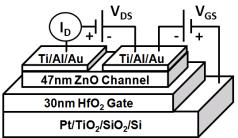

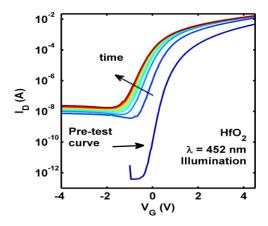

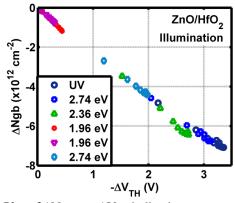

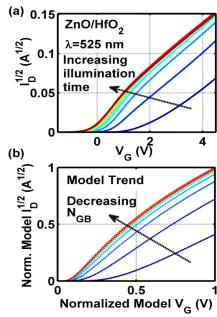

- III-4 Illumination Instability Analysis of ZnO Thin Film Transistors with HfO<sub>2</sub> Gate Dielectrics

J. J. Siddiqu<sup>1</sup>, J. D. Phillips<sup>1</sup>, K. Leedy<sup>2</sup>, and B. Bayraktaroglu<sup>2</sup>, <sup>1</sup>EECS Department, University of Michigan, Ann Arbor, Michigan, USA and <sup>2</sup>Air Force Research Laboratory, Sensors Directorate, Wright-Patterson AFB, Ohio, USA

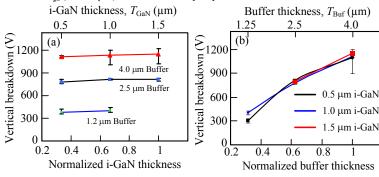

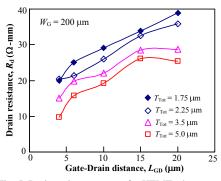

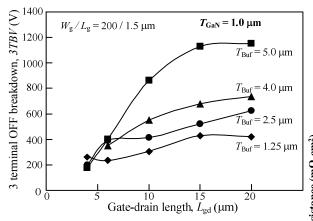

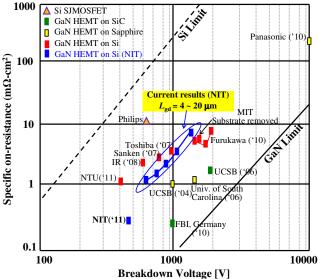

- III-5

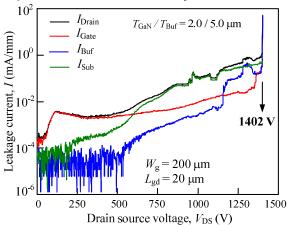

1.4 kV Breakdown Voltage for MOCVD grown AlGaN/GaN HEMTs on Si substrate

S. Selvaraj, A. Watanabe, A. Wakejima and T. Egawa, Research Center for Nano-Device and System,

Nagoya Institute of Technology, Showa-ku, Nagoya, JAPAN

- III-6

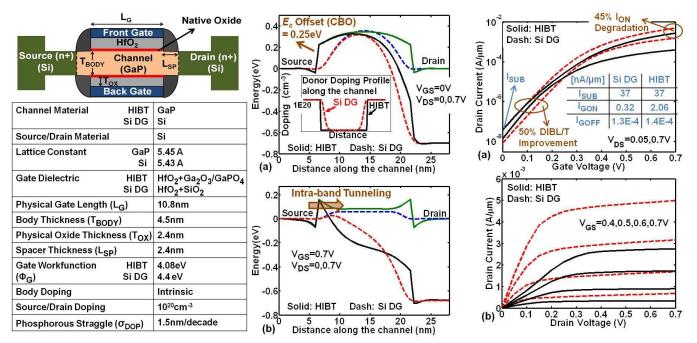

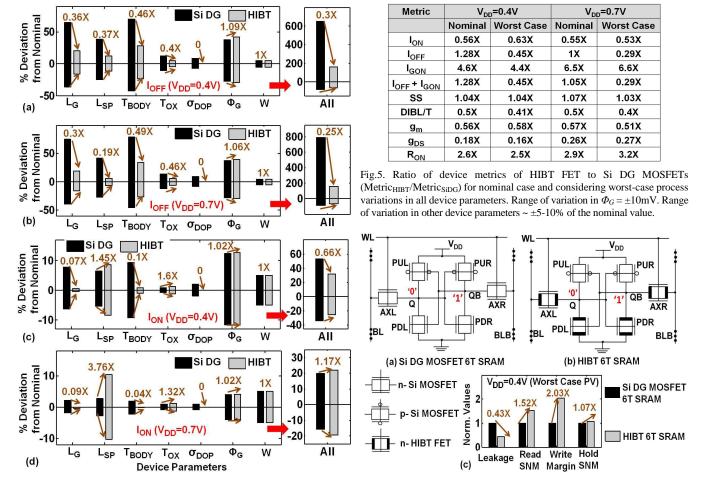

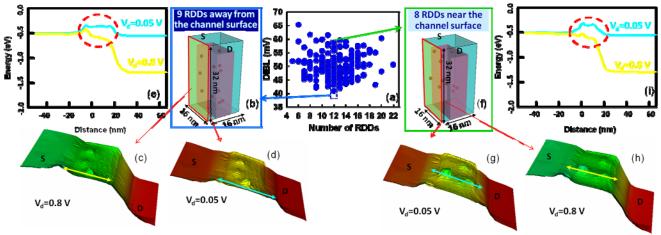

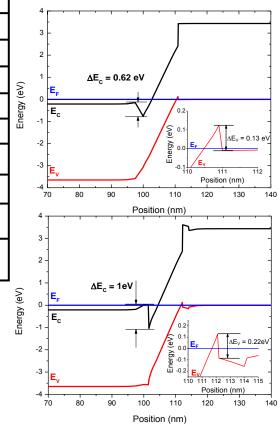

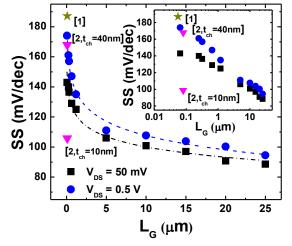

Dopant Straggle-free Heterojunction Intra-band Tunnel (HIBT) FETs with Low Drain-induced Barrier Lowering/Thinning (DIBL/T) and Reduced Variation in OFF Current

S. K. Gupta<sup>1</sup>, J. P. Kulkarni<sup>2</sup>, S. Datta<sup>3</sup> and K. Roy<sup>1</sup>, <sup>1</sup>Purdue University, West Lafayette Indiana, USA, <sup>2</sup>Intel Corporation, Hillsboro, Oregon, USA and <sup>3</sup>Penn State University, University Park, Pennsylvania, USA

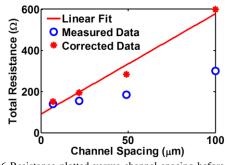

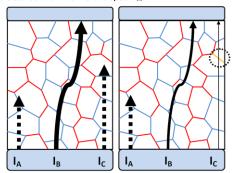

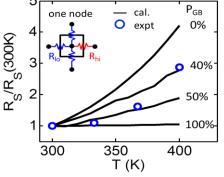

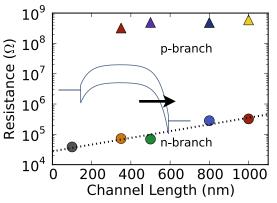

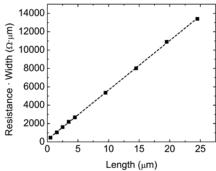

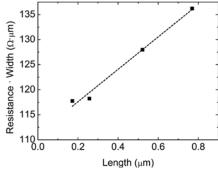

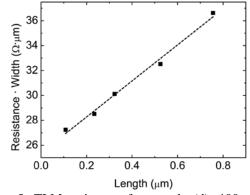

- III-7 **Exclusive Electrical Determination of High-Resistance Grain-Boundaries in poly-Graphene**R. Chen<sup>1,2</sup>, S. R. Das<sup>1</sup>, C Jeong<sup>1</sup>, D B. Janes<sup>1</sup>, M A. Alam<sup>1</sup>, <sup>1</sup>Purdue University, West Lafayette, Indiana, USA and <sup>2</sup>Zhejiang University, Zhejiang, CHINA

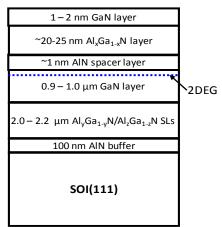

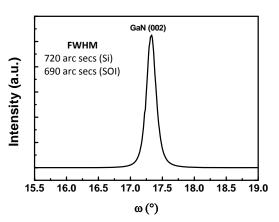

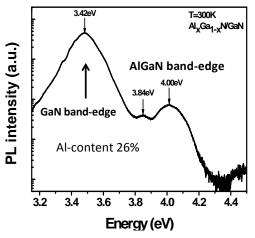

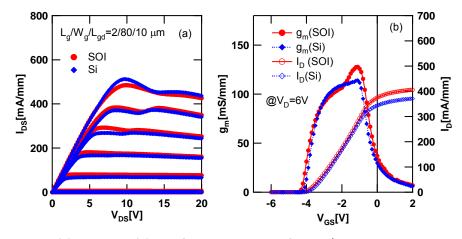

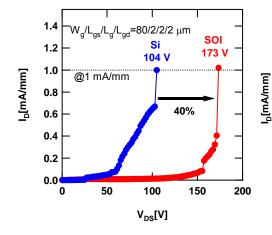

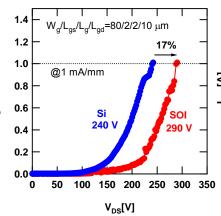

- III-8 Improved OFF-state Breakdown Voltage in AlGaN/GaN HEMTs grown on 150-mm Diameter Silicon-on-Insulator (SOI) Substrate

S. Arulkumaran<sup>1</sup>, V. K. X. Lin<sup>2</sup>, S. B. Dolmanan<sup>2</sup>, G.I. Ng<sup>3</sup>, S. Vicknesh<sup>1</sup>, J. P. Y. Tan<sup>2</sup>, S. L. Teo<sup>2</sup>, M. K Kumar<sup>2</sup> and S. Tripathy<sup>2</sup>, <sup>1</sup>Temasek Laboratories@NTU, Nanyang Technological University, SINGAPORE, <sup>2</sup>Institute of Materials Research and Engineering, A\*STAR, SINGAPORE, and <sup>3</sup>NOVITAS, Nanoelectronics Centre of Excellence, School of EEE, Nanyang Technological University, SINGAPORE

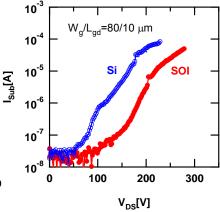

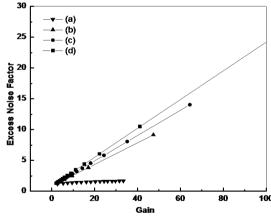

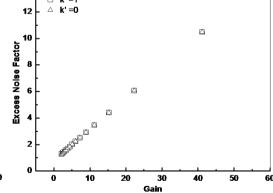

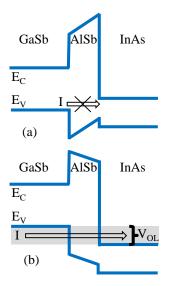

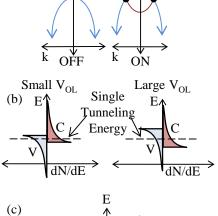

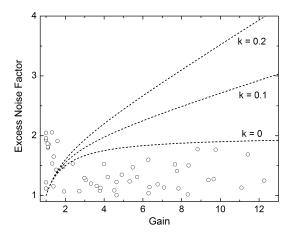

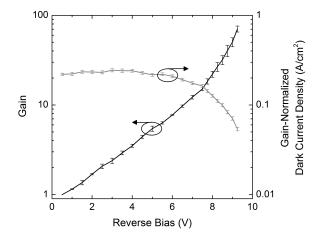

- III-9 Improved Dual-Carrier High Gain Impact Ionization Engineered Avalanche Photodiode

J. Huang<sup>1</sup>, K. Banerjee<sup>1</sup>, S. Ghosh<sup>1</sup>, and M. M. Hayat<sup>2</sup>, <sup>1</sup>Dept. of ECE, Univ. of Illinois at Chicago, Chicago,

Ilinois, USA and <sup>2</sup>Center for High Technology Materials, Univ. of New Mexico, Albuquerque, New Mexico, USA

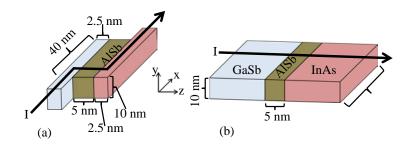

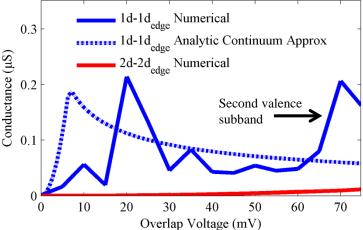

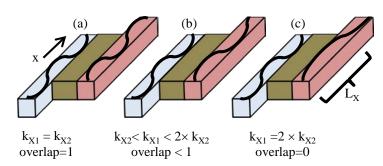

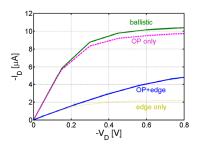

- III-10 Enhanced Tunneling Current in 1d-1d<sub>Edge</sub>Overlapped TFET's

S. Agarwal and E. Yablonovitch, University of California, Berkeley, California, USA

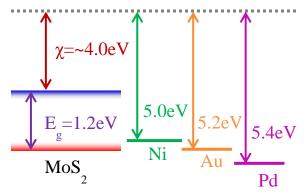

- III-11 **Metal Contacts to Mo₂: a Two-Dimensional Semiconductor**A. T. Neal, H. Liu, J. J. Gu, and P. D. Ye, School of Electrical and Computer Engineering and Birck Nanotechnology Center, Purdue University, West Lafayette, Indiana, USA

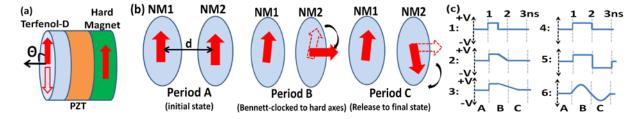

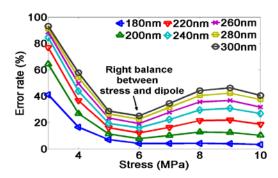

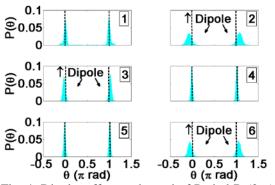

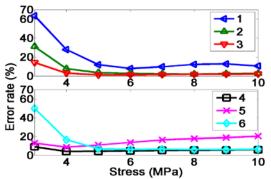

- III-12 Balancing stress & dipolar interactions for fast, low power, reliable switching in multiferroic logic K. Munira, S. Nadri, M. Forgues, and A. W. Ghosh, Department of Electrical and Computer Engineering, University of Virginia, Charlottesville, Virginia, USA

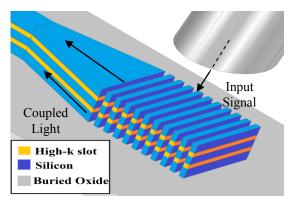

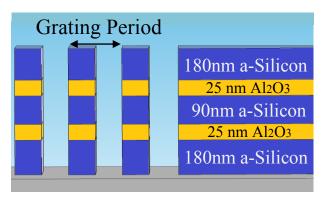

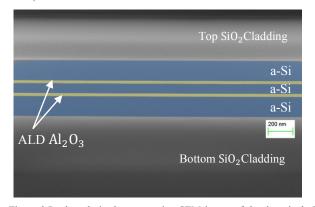

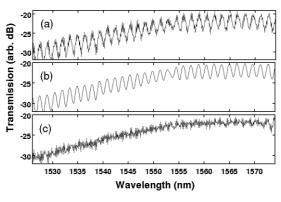

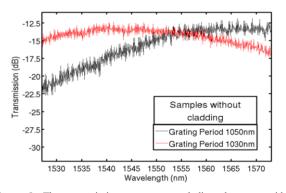

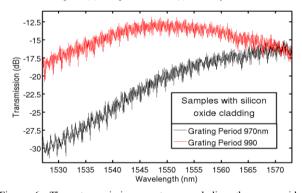

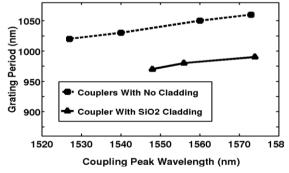

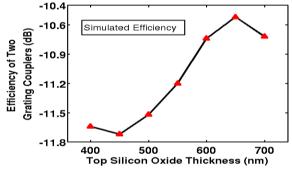

- III-13 **Double Slot High-k Waveguide Grating Couplers for Silicon Photonics**M. M. Naiini, C. Henkel, G. B. Malm and M. Östling, KTH Royal Institute of Technology, School of Information and Communication Technology, Integrated Devices and Circuits, Kista, SWEDEN

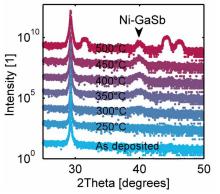

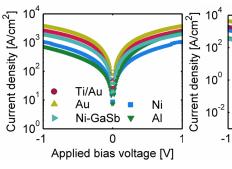

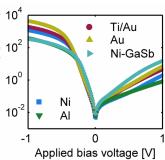

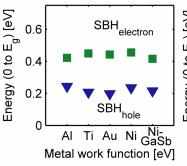

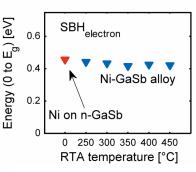

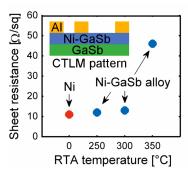

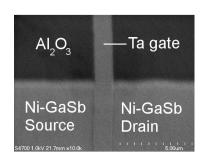

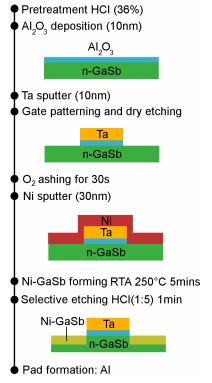

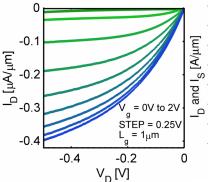

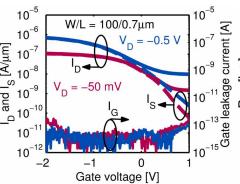

- III-14 Self-aligned metal S/D GaSb p-MOSFETs using Ni-GaSb alloys

C. B. Zota, S. H. Kim, Y. Asakura, M. Takenaka and S. Takagi, School of Engineering, The University of Tokyo, Bunkyo-ku, Tokyo, JAPAN

- III-15 **Bilayer Graphene Vertical Tunneling Field Effect Transistor**D. Reddy, L. F. Register, and S. K. Banerjee, University of Texas, Austin, Texas, USA

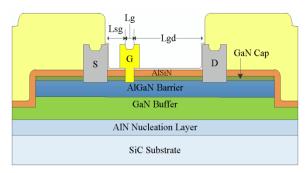

- III-16 **440 V AlSiN-Passivated AlGaN/GaN High Electron Mobility Transistor with 40 GHz Bandwidth**E. Harvard and J. R. Shealy, Cornell University, School of Electrical and Computer Engineering, Ithaca, New York, USA

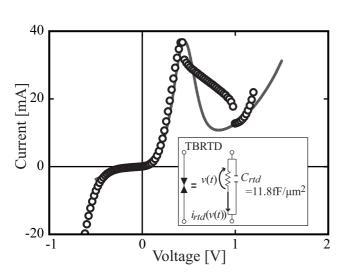

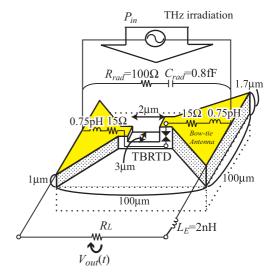

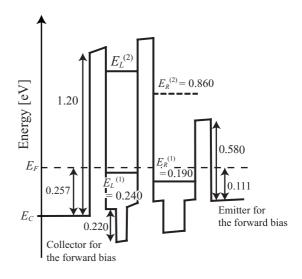

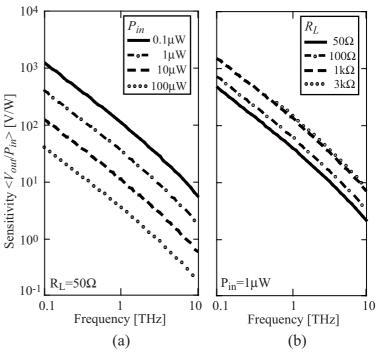

- Analysis of terahertz zero bias detectors by using a triple-barrier resonant tunneling diode integrated with a self-complementary bow-tie antenna

M. Suhara<sup>1</sup>, S. Takahagi<sup>1</sup>, K. Asakawa<sup>1</sup>, T. Okazaki<sup>1</sup>, M. Nakamura<sup>1</sup>, S. Yamashita<sup>1</sup>, Y. Itagaki<sup>1</sup>, M. Saito<sup>1</sup>, A. Tchegho<sup>2</sup>, G. Keller<sup>2</sup>, A.r Poloczek<sup>2</sup>, W. Prost<sup>2</sup>, F-J. Tegud<sup>2</sup>, <sup>1</sup>Electrical and Electronic Engineering, Graduate School of Science and Engineering, Tokyo Metropolitan University, Hachioji, Tokyo, JAPAN and <sup>2</sup>Center for Semiconductor Technology and Optoelectronics, University of Duisburg-Essen, Duisburg, GERMANY

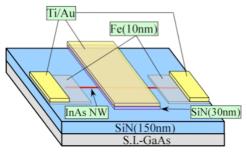

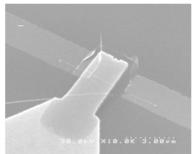

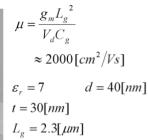

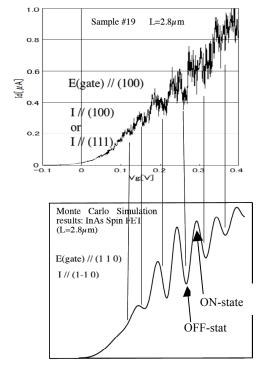

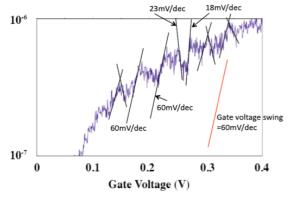

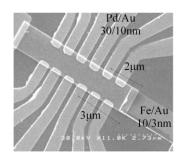

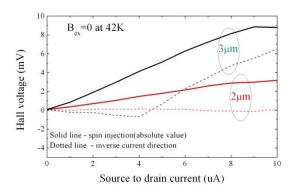

- III-18 An InAs Nanowire Spin Transistor with Subthreshold Slope of 20mV/dec

K. Yoh<sup>1</sup>, Z. Cui<sup>1</sup>, K. Konishi<sup>1</sup>, M. Ohno<sup>2</sup>, K. Blekker<sup>3</sup>, W. Prost<sup>3</sup>, F.-J. Tegude<sup>3</sup>, J.-C. Harmand<sup>4</sup>, <sup>1</sup>Research

Center for Integrated Quantum Electronics, Hokkaido University, Sapporo, JAPAN, <sup>2</sup>Graduate School of

Engineering, Hokkaido University, Sapporo, JAPAN, <sup>3</sup>Semiconductor and Information Engineering, University

of Duisburg-Essen, Duisburg, GERMANY, and <sup>4</sup>CNRS-Laboratory of Photonic and Nanostructures,

Marcoussis, FRANCE

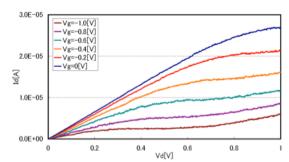

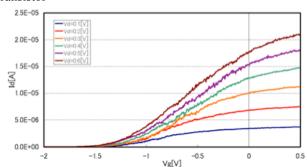

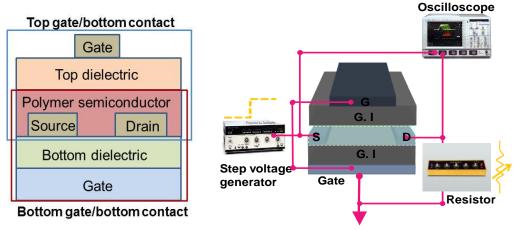

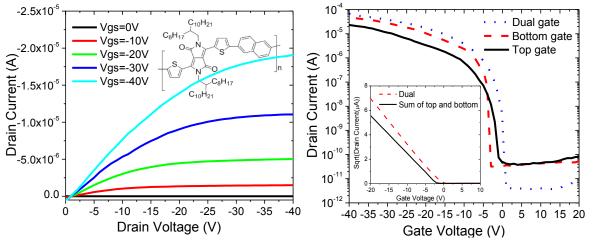

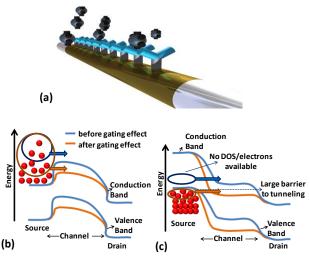

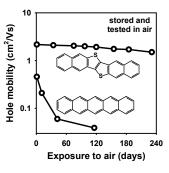

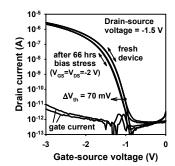

- III-19 **Understanding dual-gate polymer field-effect transistors**T.-J. Ha<sup>1</sup>, P. Sonar<sup>2</sup> and A. Dodabalapur<sup>1</sup>, <sup>1</sup>Microelectronics Research Center, The University of Texas at Austin, Austin, Texas, USA and <sup>2</sup>Institute of Materials Research and Engineering, Singapore, SINGAPORE

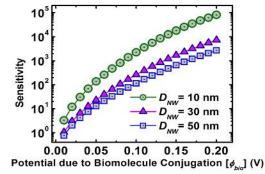

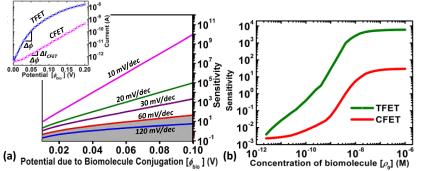

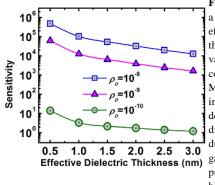

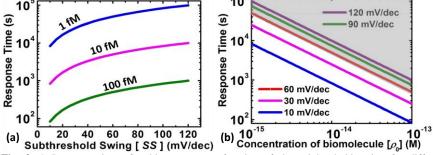

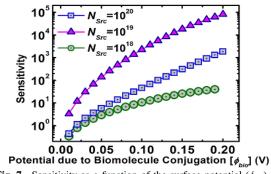

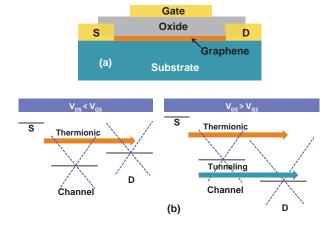

- III-20 Fundamental Limitations of Conventional-FET Biosensors: Quantum-Mechanical-Tunneling to the Rescue

D. Sarkar and K. Banerjee, Department of Electrical and Computer Engineering, University of California, Santa Barbara, California, USA

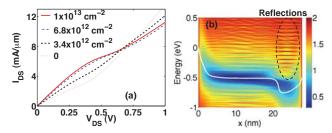

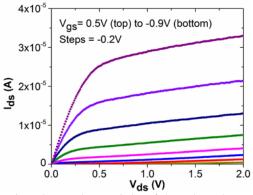

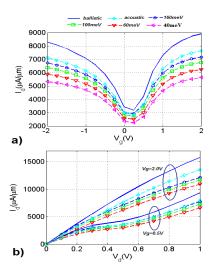

- III-21 Can Quasi-Saturation in the Output Characteristics of Short-Channel Graphene Field-Effect Transistors be Engineered?

K. Ganapathi<sup>1</sup>, M. Lundstrom<sup>2</sup> and S. Salahuddin<sup>1</sup>, <sup>1</sup>, Department of Electrical Engineering and Computer Sciences, UC Berkeley, Berkeley, California, USA and <sup>2</sup>, School of Electrical and Computer Engineering, Purdue University, West Lafayette, Indiana, USA

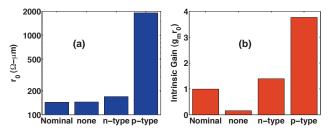

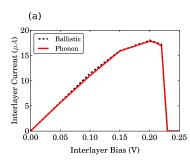

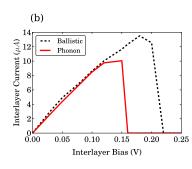

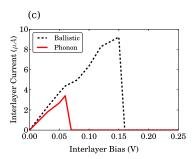

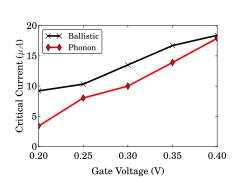

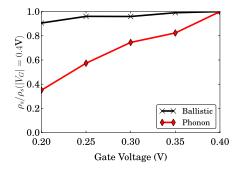

- III-22 Phonon Limited Transport in Graphene Pseudospintronic Devices

Z. J. Estrada, B. Dellabetta, U. Ravaioli, and M. J. Gilbert, University of Illinois at Urbana-Champaign, Urbana, Illinois, USA

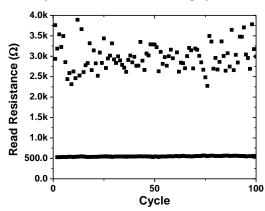

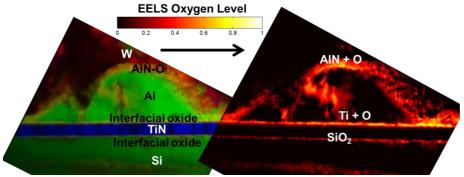

- III-23 Resistive Switching in Aluminum Nitride

M. J. Marinella, J. E. Stevens, E. M. Longoria, and P. G. Kotula, Sandia National Laboratories, Albuquerque, New Mexico, USA

- III-24 Limits of Detection for Silicon Nanowire BioFETs

N. K. Rajan, X. Duan, A. Vacic, D. A. Routenberg, M. A. Reed, Dept. of Applied Physics, Dept. of Electrical Engineering, New Haven, Connecticut, USA

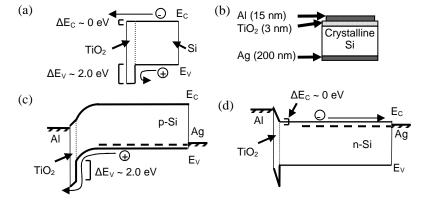

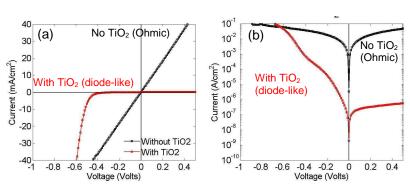

- III-25 Hole-blocking TiO<sub>2</sub>/Silicon Heterojunction for Silicon Photovoltaics

S. Avasthi<sup>1</sup>, W. McClain<sup>2</sup>, J. Schwartz<sup>2</sup>, and J. C. Sturm<sup>1</sup>, Princeton Institute for the Science and Technology of Materials, Princeton University, Princeton New Jersey, USA and <sup>1</sup>Department of Electrical Engineering and <sup>2</sup>Department of Chemistry

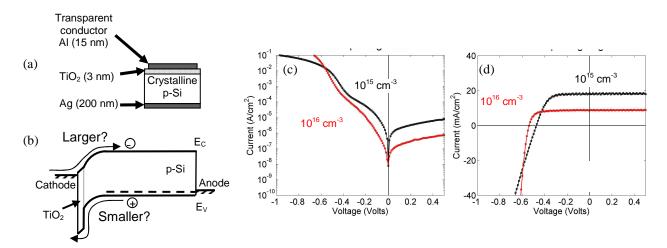

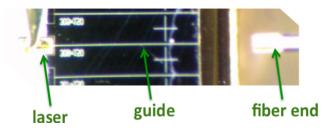

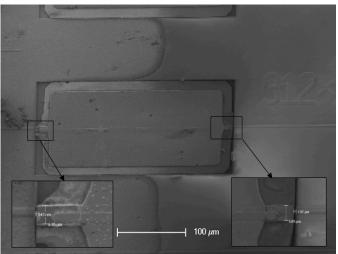

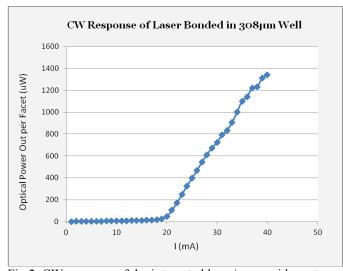

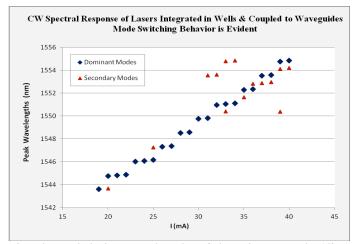

- III-26 Recess Integration of Platelet Laser Diodes with Waveguides on Silicon

S. Famenini and C. G. Fonstad, Massachusetts Institute of Technology, Cambridge, Massachusetts, USA

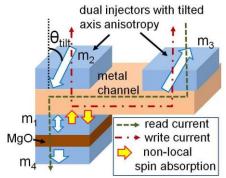

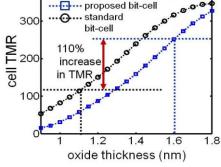

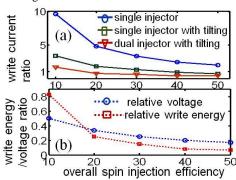

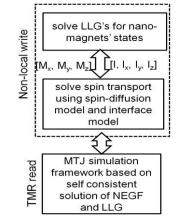

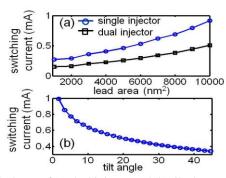

- III-27 NLSTT-MRAM: Robust Spin Transfer Torque MRAM using Non-Local Spin Injection for Write

M. Sharad<sup>1</sup>, G. Panagopoulos<sup>1</sup>, C. Augustine<sup>2</sup> and K. Roy<sup>1</sup>, <sup>1</sup>School of Electrical and Computer Engineering,

Purdue University, West Lafayette, Indiana, USA and <sup>2</sup>Circuit Research Lab, Intel labs, Intel Corporation,

Hillsboro, Oregon, USA

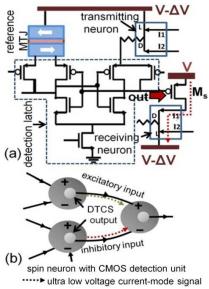

- III-28 All Spin Logic device as a compact artificial neuron

A. Sarkar<sup>1</sup>, B. Behin-Aein<sup>2</sup>, S. Srinivasan<sup>1</sup>, and S. Datta<sup>1</sup>, <sup>1</sup>School of Electrical and Computer Engineering,

Purdue University, W. Lafayette, Indiana, USA and <sup>2</sup>Technology Research Group, GLOBALFOUNDRIES USA,

Sunnyvale, Calidorna, USA

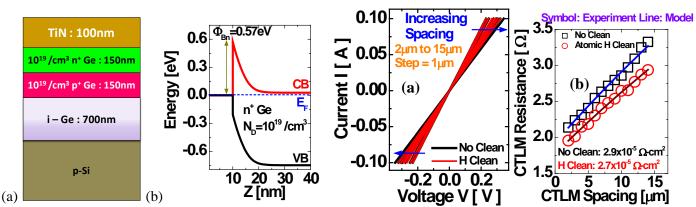

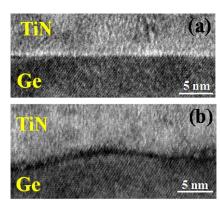

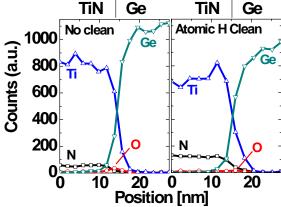

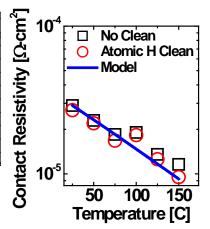

- III-29 Experimental Demonstration of "Cold" Low Contact Resistivity Ohmic Contacts on Moderately Doped n-Ge with in-situ Atomic Hydrogen Clean

A. Agrawal<sup>1</sup>, J. Park<sup>2</sup>, D. Mohata<sup>1</sup>, K. Ahmed<sup>2</sup> and S. Datta<sup>1</sup>, <sup>1</sup>Department of Electrical Engineering, The Pennsylvania State University, University Park, Pennsylvania, USA and <sup>2</sup>Applied Materials, Inc., Santa Clara, California, USA

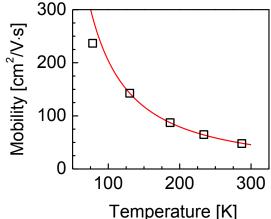

- III-30 Mobility and Scattering Mechanisms in Buried InGaSb Quantum Well Channels Integrated with in-situ MBE Grown Gate Oxide

S. Madisetti, P. Nagaiah, T. Chidambaram, V. Tokranov, M. Yakimov, and S. Oktyabrsky, College of Nanoscale Science and Engineering, University at Albany- SUNY, Albany, New York, USA

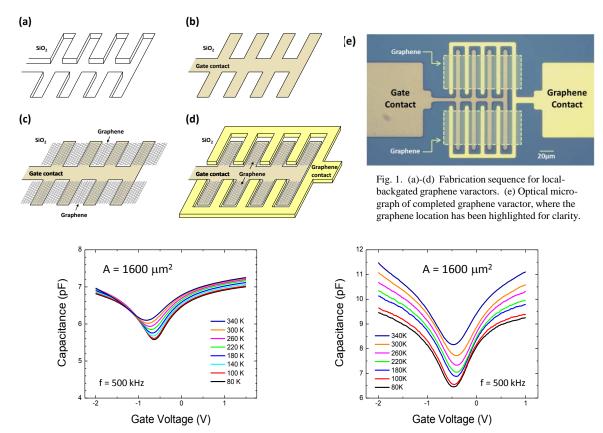

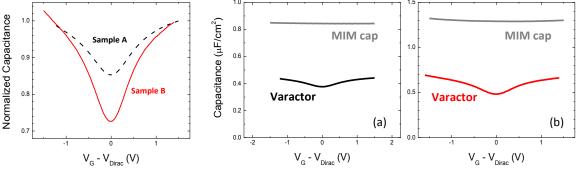

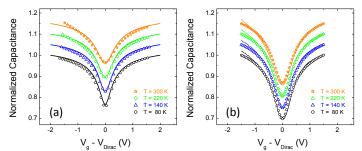

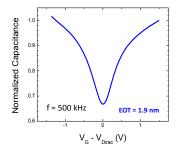

- III-31 Dielectric Thickness Dependence of Quantum Capacitance in Graphene Varactors with Local Metal Back Gates

M. A. Ebrish and S. J. Koester, University of Minnesota-Twin Cities, Minneapolis, Minnesota, USA

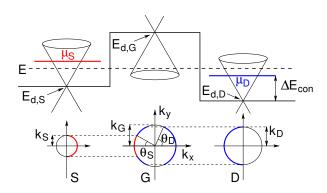

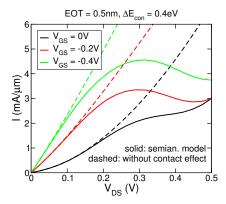

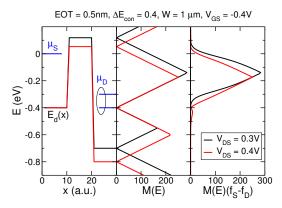

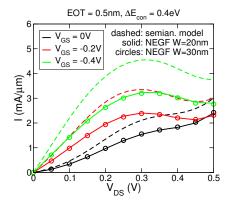

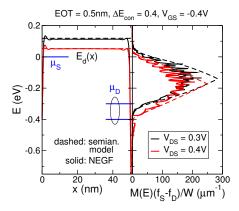

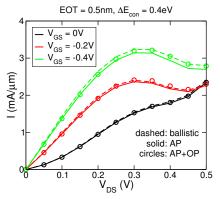

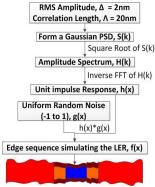

- III-32 **Negative dierential resistance in short-channel graphene FETs: semianalytical model and simulations** R. Grassi<sup>1</sup>, T. Low<sup>2</sup>, A. Gnudi<sup>1</sup> and G. Baccarani<sup>1</sup>, <sup>1</sup>ARCES, University of Bologna, Bologna, ITALY and <sup>2</sup>IBM T.J. Watson Research Center, Yorktown Heights, New York, USA

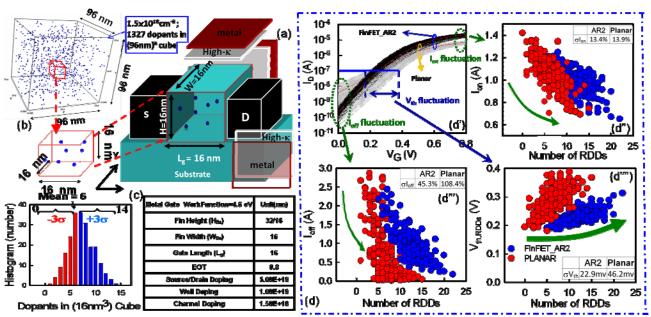

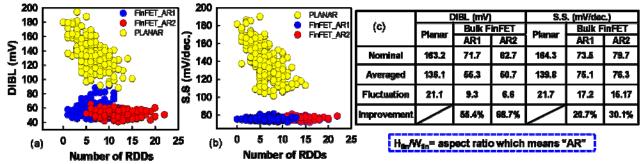

- III-33 Drain-Induced-Barrier Lowering and Subthreshold Swing Fluctuations in 16-nm-Gate Bulk FinFET Devices Induced by Random Discrete Dopants

H.-W. Su, Y. Li, Y.-Y. Chen, C.-Y. Chen, and H.-T. Chang, Parallel and Scientific Computing Laboratory, Department of Electrical Engineering, National Chiao Tung University, Hsinchu, TAIWAN

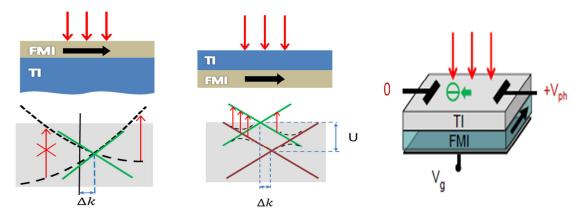

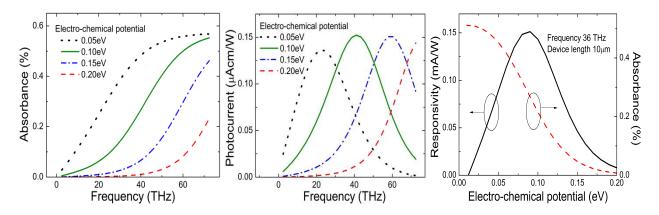

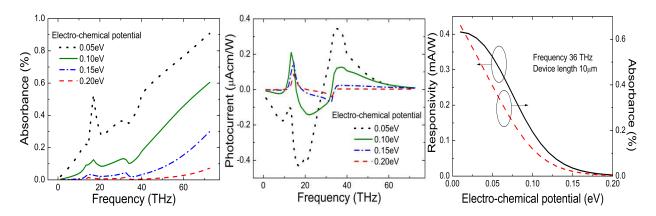

- III-34 **THz Detector Based on Proximity Effect of Topological Insulator**X. Li, Y. G. Semenov, and K. W. Kim, Dept. of Electrical and Computer Engineering, North Carolina State University, Raleigh, North Carolina, USA

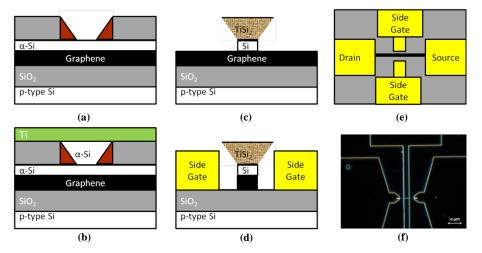

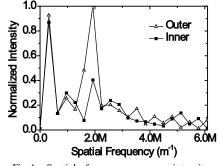

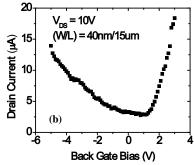

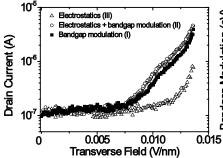

- III-35 Transverse-Field Bandgap Modulation on Graphene Nanoribbon Transistors by Double-Self-Aligned Spacers

L.-T. Tung, M. V. Mateus and E. C. Kan, School of Electrical and Computer Engineering, Cornell University, Ithaca, New York, USA

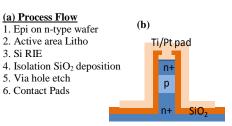

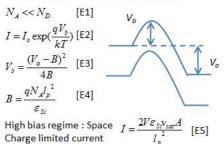

- III-36 **Epitaxial Si Punch-Through based Selector for Bipolar RRAM**P. Bafna<sup>1</sup>, P. Karkare<sup>1</sup>, S Srinivasan<sup>1</sup>, S. Chopra<sup>2</sup>, S. Lashkare<sup>1</sup>, Y. Kim<sup>2</sup>, S. Srinivasan<sup>2</sup>, S. Kuppurao<sup>2</sup>, S. Lodha<sup>1</sup>, and U. Ganguly<sup>1</sup>, <sup>1</sup>Department of Electrical Engineering, Indian Institute of Technology, Bombay, Mumbai, INDIA and <sup>2</sup>Epi-Division, Front End Products, Applied Materials Inc., Santa Clara, California, USA

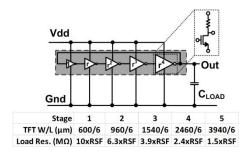

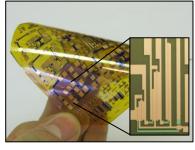

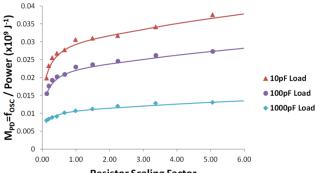

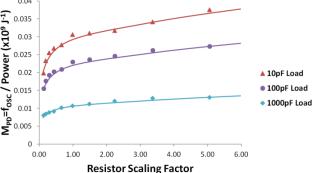

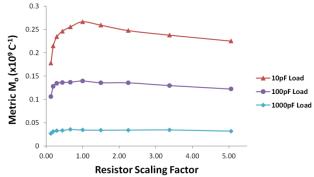

- III-37 A Figure of Merit for Oscillator-Based Thin-Film Circuits on Plastic for High-Performance Signaling, Energy Harvesting and Driving of Actuation Circuits

W. Rieutort-Louis, L. Huang, Y. Hu, J. Sanz-Robinson, S. Wagner, J. C. Sturm, N. Verma Princeton University, Department of Electrical Engineering, Princeton, New Jersey, USA

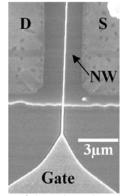

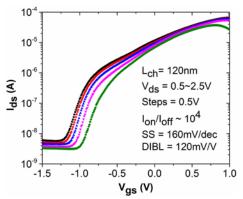

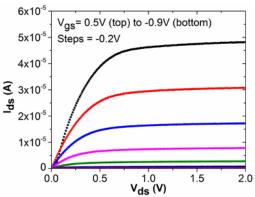

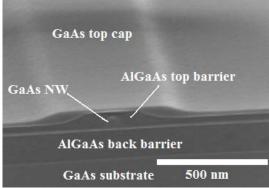

- III-38 Short-Channel Enhancement-mode Planar GaAs Nanowire HEMTs through a Bottom-up method Xin Miao, Chen Zhang and Xiuling Li, Department of Electrical and Computer Engineering, Micro and Nanotechnology Laboratory University of Illinois at Urbana-Champaign, Urbana, Illinois, USA

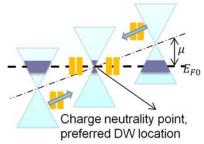

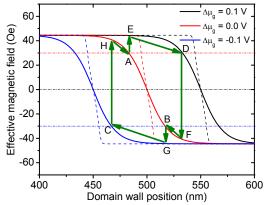

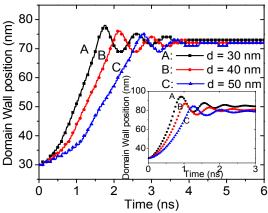

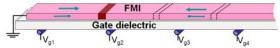

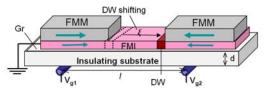

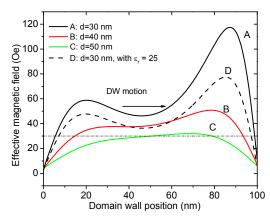

- III-39 **Electric Field Driven Domain Wall Transfer in Hybrid Structures**X. Duan<sup>1</sup>, V. Stephanovich<sup>2</sup>, Y. G. Semenov<sup>1</sup>,H. Fangohr<sup>3</sup>, M. Franchin<sup>3</sup>, and K. Wook Kim<sup>1</sup>, <sup>1</sup>Electrical and Computer Engineering, North Carolina State University, Raleigh, North Carolina, USA, <sup>2</sup>nstitute of Physics, Opole University, Oleska, POLAND and <sup>3</sup>Engineering and the Environment, University of Southampton, Southampton, UNITED KINGDOM

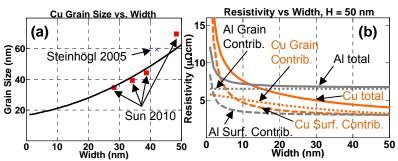

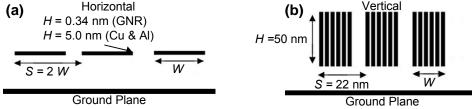

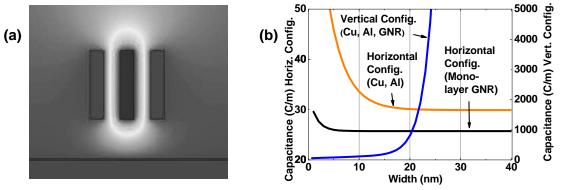

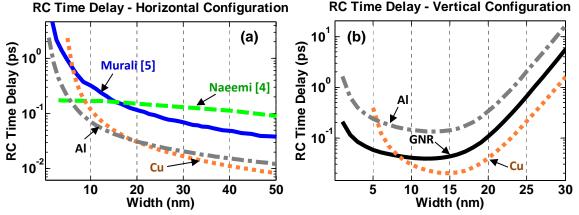

- III-40 Comparison of Graphene Nanoribbons With Cu and Al Interconnects

N. Wang<sup>1</sup>, C. D. English<sup>2</sup>, and E. Pop<sup>1</sup>, <sup>1</sup>Dept. of Electrical and Computer Engineering and <sup>2</sup>Dept. of Physics,

University of Illinois at Urbana-Champaign, Urbana Ilinois, USA

- III-41 Electrical Control of Nuclear-Spin-Induced Hall Voltage in an Inverted InAs Heterostructure

T. Ishikura, Z. Cui and K. Yoh, Research Center of Integrated Quantum Electronics, Hokkaido University,

Sapporo, JAPAN

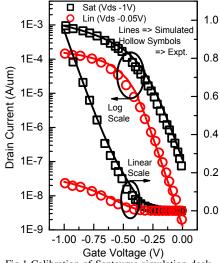

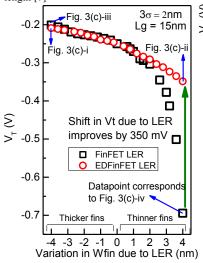

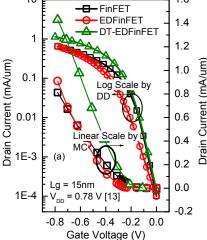

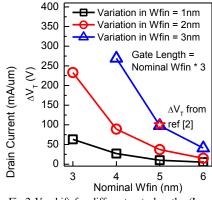

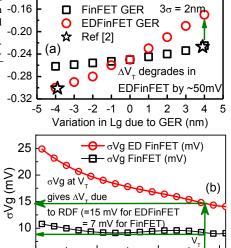

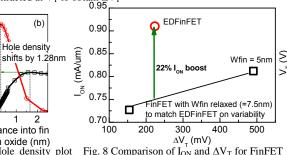

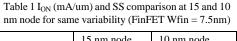

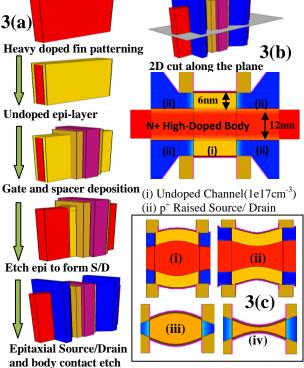

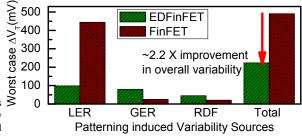

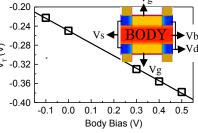

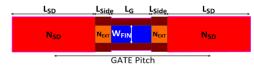

- III-42 **Epitaxialy defined (ED) FinFET: to reduce V**<sub>T</sub> variability and enable multiple V<sub>T</sub>

S. Mittal<sup>1</sup>, S. Gupta<sup>2</sup>, A. Nainani<sup>2</sup>, M.C. Abraham<sup>2</sup>, K. Schuegraf<sup>2</sup>, S. Lodha<sup>1</sup>, U. Ganguly<sup>1</sup>, <sup>1</sup>CEN, Department of EE, Indian Institute of Technology Bombay, INDIA and <sup>2</sup>Applied Materials Inc, Santa Clara, California, USA

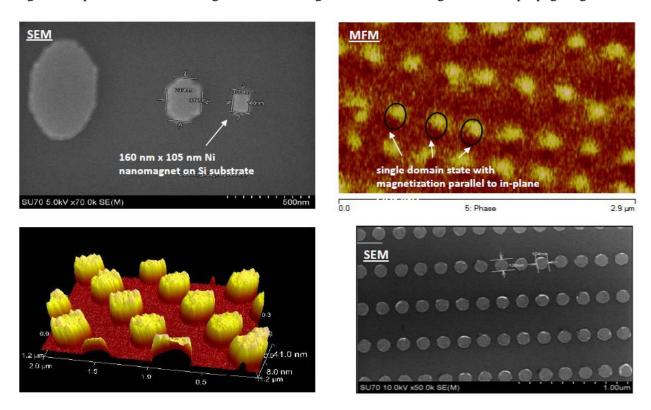

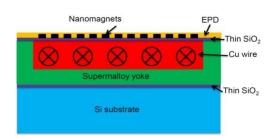

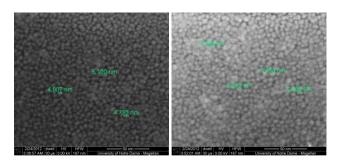

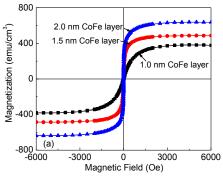

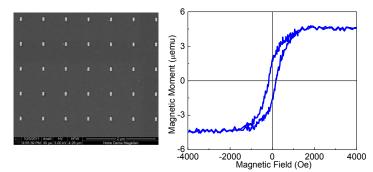

- III-43 **Power Reduction in Nanomagnetic Logic Clocking through High Permeability Dielectrics**P. Li<sup>1</sup>, G. Csaba<sup>1</sup>, V. K. Sankar<sup>1</sup>, X. S. Hu<sup>2</sup>, M. Niemier<sup>2</sup>, W. Porod<sup>1</sup>, G. H. Bernstein<sup>1</sup>, <sup>1</sup>Department of Electrical Engineering and <sup>2</sup>Department of Computer Science and Engineering, University of Notre Dame, Notre Dame, Indiana. USA

- III-44

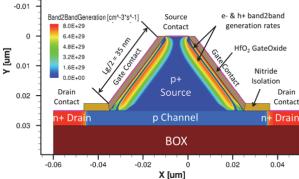

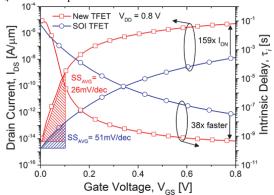

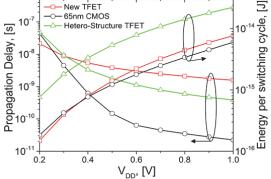

New Tunnel-FET Architecture with Enhanced I<sub>ON</sub> and Improved Miller Effect for Energy Efficient Switching

A. Biswas, C. Alper, L. De Michielis, A. M. Ionescu, Nanoelectronics Devices Laboratory (NANOLAB), Ecole Polytechnique Fédérale de Lausanne, EPFL, SWITZERLAND

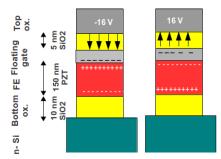

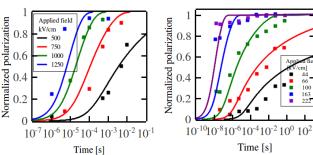

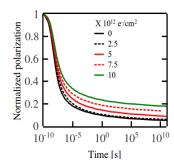

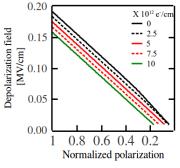

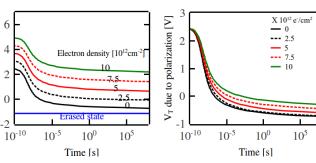

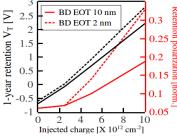

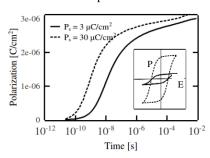

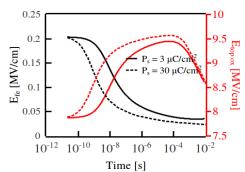

- III-45 **Switching dynamics in ferroelectric-charge hybrid nonvolatile memory**K. Auluck, S. Rajwade and E. C. Kan, School of Electrical and Computer Engineering, Cornell University, Ithaca. New York, USA

- III-46

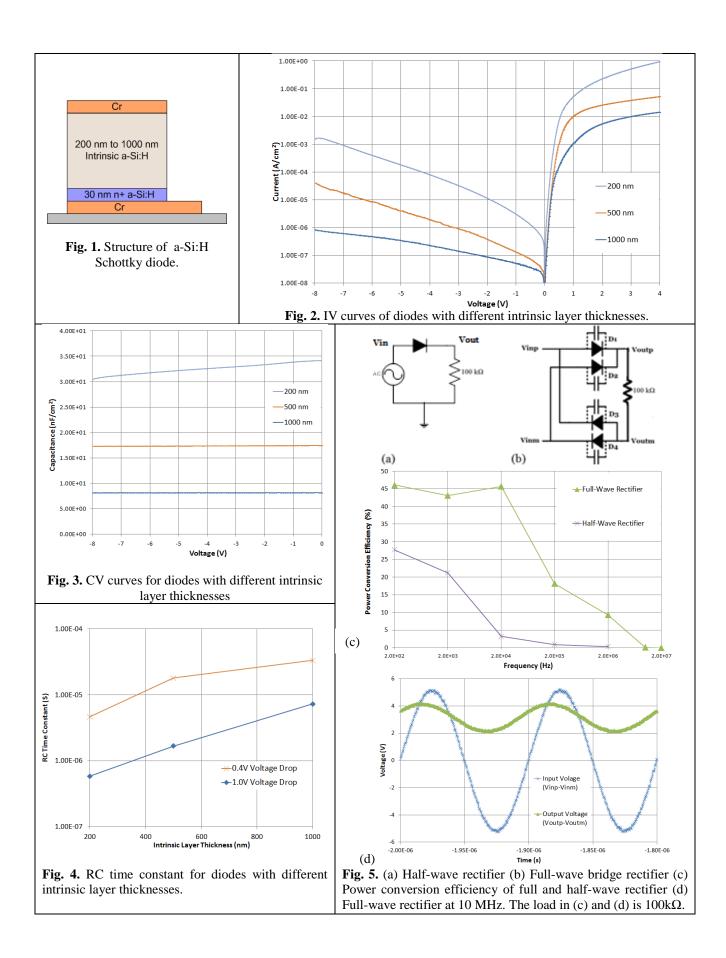

Frequency Dependence of Amorphous Silicon Schottky Diodes for Large-Area Rectification

Applications

J. Sanz-Robinson, W. Rieutort-Louis, N. Verma, S. Wagner, and J. C. Sturm, Dept. of Electrical Engineering

and the Princeton Institute for the Science and Technology of Materials, Princeton University, Princeton, New

Jersey, USA

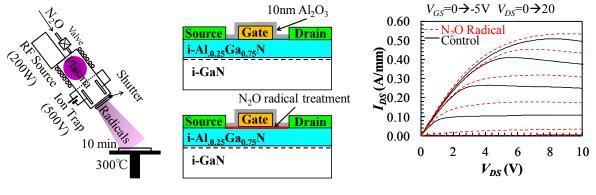

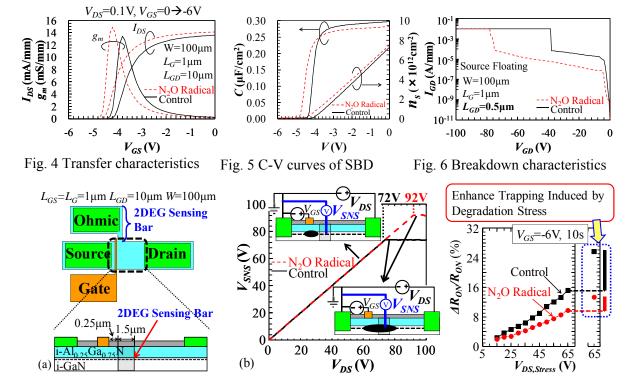

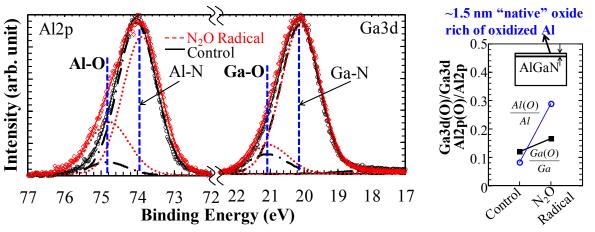

- III-47

Reliability Improvement Achieved by N₂O Radical Treatment for AlGaN/GaN Heterojunction Field-Effect Transistors

C.-Y. Hu and T. Hashizume, Research Center for Integrated Quantum Electronics (RCIQE),Hokkaido University, Sapporo, JAPAN

- III-48 **Exploring Variability and Reliability of Multi-Level STT-MRAM Cells**G. Panagopoulos<sup>1</sup>, C. Augustine<sup>2</sup>, X. Fong<sup>1</sup> and K. Roy<sup>1</sup>, <sup>1</sup>School of ECE, Purdue University, West Lafayette, Indiana, USA and <sup>2</sup>Circuit Research Lab, Intel labs, Hillsboro, Oregon, USA

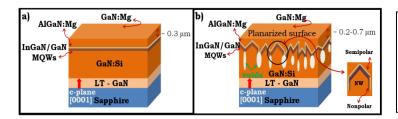

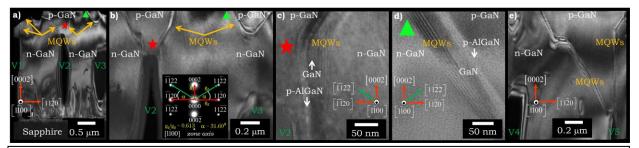

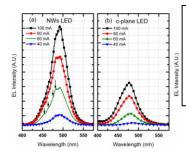

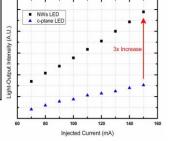

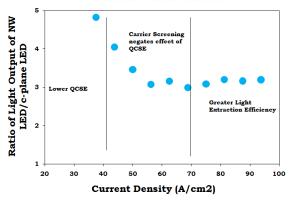

- III-49 Comparative Study of LEDs conformally overgrown on multi-facet GaN NWs vs. conventional c-plane LEDs

A..M. Hosalli<sup>1</sup>, P. Frajtag<sup>2</sup>, D. M. Van Den Broeck<sup>1</sup>, T. Paskova1<sup>2</sup>, N..A. El-Masry<sup>2</sup>, and S..M. Bedair<sup>1</sup>, <sup>1</sup>Department of Electrical and Computer Engineering, North Carolina State University, Raleigh, North Carolina, USA and <sup>2</sup>Department of Materials Science and Engineering, North Carolina State University, Raleigh, North Carolina, USA

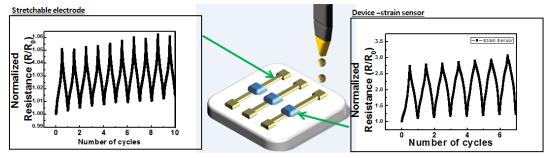

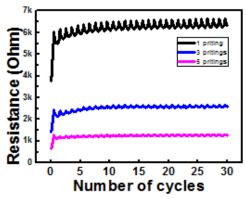

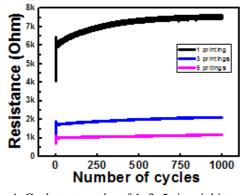

- III-50 Inkjet-printed SWCNT films for stretchable electrode and strain sensor applications

T. Kim, J. Byun, H. Song and Y. Hong, Department of Electrical Engineering and Computer Science, Seoul National University, Gwanak-gu, Seoul, KOREA

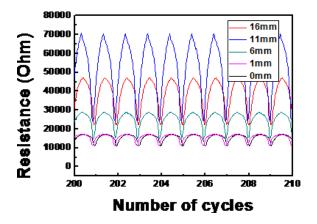

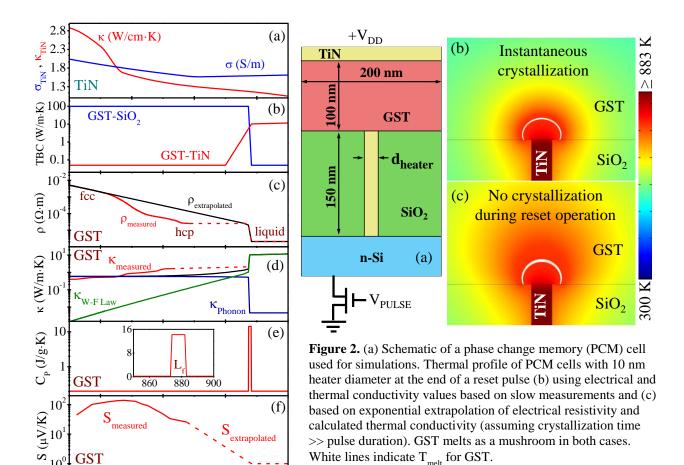

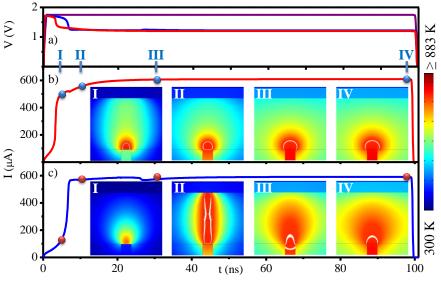

- III-51 Comparison of Instantaneous Crystallization and Metastable Models in Phase Change Memory Cells A. Faraclas, N. Williams, G.n Bakan, A. Gokirmak, and H. Silva, Electrical and Computer Engineering, University of Connecticut, Storrs, Connecticut, USA

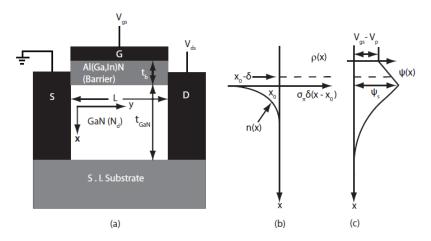

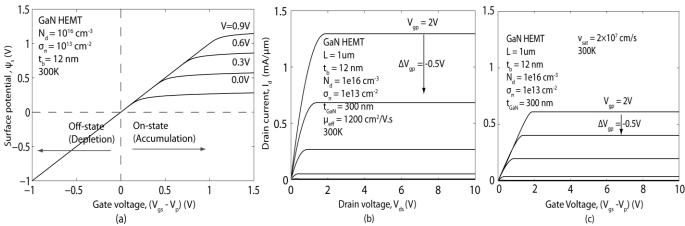

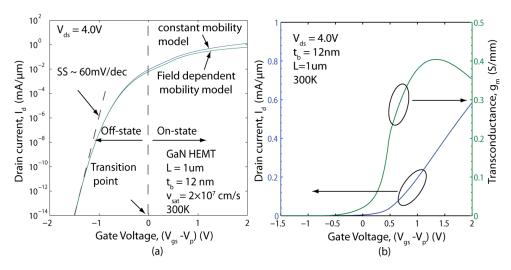

- III-52 A Surface-Potential Based Compact Model for GaN HEMTs Incorporating Polarization Charges R. Jana and D. Jena, Electrical Engineering, University of Notre Dame, Notre Dame, Indiana, USA

# Session IV.A. Wide Bandgap/High Speed Devices 149-170

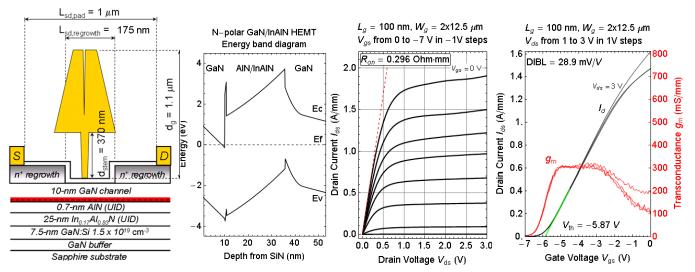

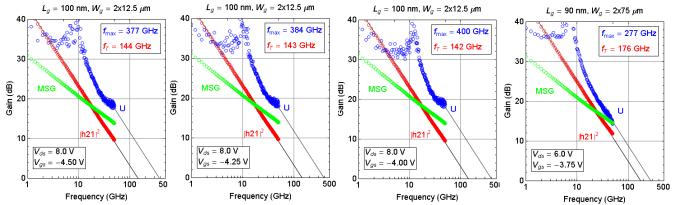

IV.A-1 N-polar GaN/InAIN MIS-HEMT with 400-GHz fmax

District of Columbia, USA

- 8:20 D. Denninghoff, J. Lu, M. Laurent, E. Ahmadi, S. Keller and U. K. Mishra

Department of Electrical and Computer Engineering, University of California, Santa Barbara, California, USA

- IV.A-2

8:40

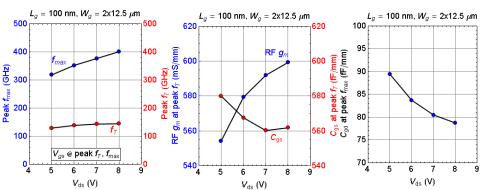

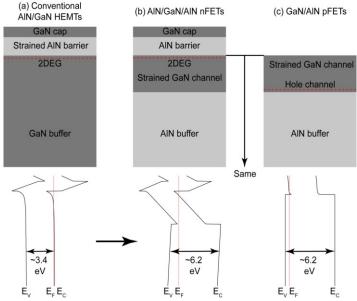

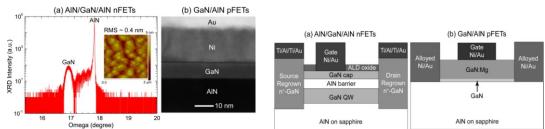

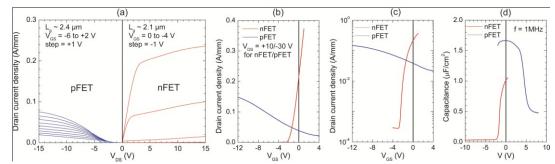

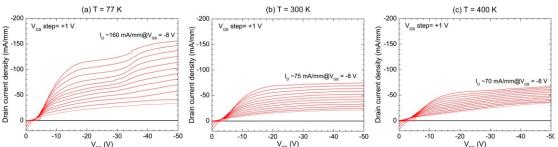

Ultra-thin Body GaN-on-Insulator nFETs and pFETs: Towards III-Nitride Complementary Logic

G. Li, R. Wang, J. Verma, H. Xing, D. Jena, Department of Electrical Engineering, University of Notre Dame, Notre Dame, Indiana, USA

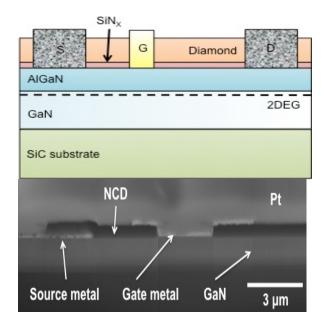

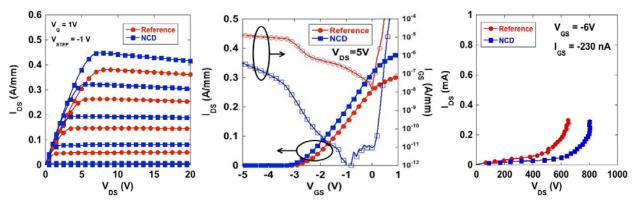

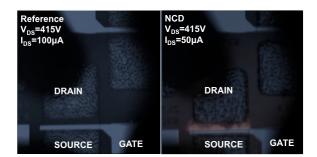

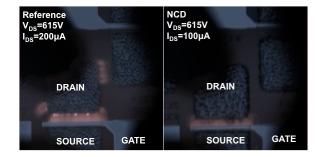

- Improved GaN-based HEMT Performance by Nanocrystalline Diamond Capping

9:00 AM

T. J. Anderson<sup>1</sup>, K. D. Hobart<sup>1</sup>, M. J. Tadjer<sup>2</sup>, T. I. Feygelson<sup>3</sup>, E. A. Imhoff<sup>1</sup>, D. J. Meyer<sup>1</sup>, D. S. Katzer<sup>1</sup>, J. K. Hite<sup>1</sup>, F. J. Kub<sup>1</sup>, B. B. Pate<sup>1</sup>, S. C. Binari<sup>1</sup>, and C. R. Eddy, Jr<sup>1</sup>, Naval Research Laboratory, Washington District of Columbia, USA, Universidad Politécnica de Madrid, Madrid, SPAIN and SAIC, Inc., Washington,

- IV.A-4

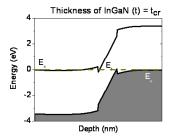

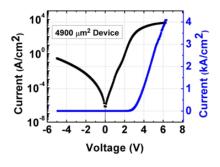

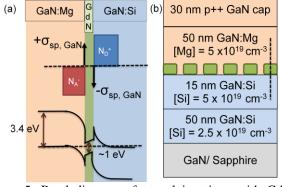

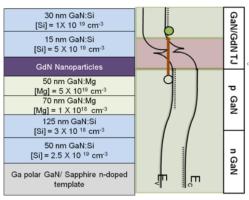

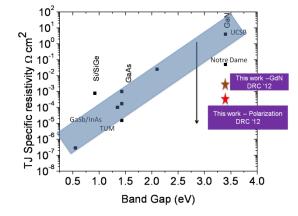

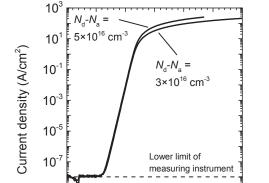

Record low tunnel junction specific resistivity (< 3X10-4 Ocm2) in GaN inter-band tunnel junctions

9:20 AM

S. Krishnamoorthy<sup>1</sup>, F. Akyol<sup>1</sup>, J. Yang<sup>2</sup>, P. S. Park<sup>1</sup>, R. C. Myers<sup>2,1</sup>, S. Rajan<sup>1,2</sup>, <sup>1</sup>Department of Electrical & Computer Engineering, The Ohio State University, Columbus, Ohio, USA and <sup>2</sup>Department of Material Science & Engineering, The Ohio State University, Columbus, Ohio, USA

- IV.A-5

9:40 AM

Saitama, JAPAN, National Institute of Information and Communications Technology, Koganei, Tokyo, JAPAN,

Saitama, JAPAN, <sup>2</sup>National Institute of Information and Communications Technology, Koganei, Tokyo, JAPAN <sup>3</sup>PRESTO, Japan Science and Technology Agency, Chiyoda, Tokyo, JAPAN, and <sup>4</sup>Koha Co., Ltd., Nerima, Tokyo, JAPAN

- IV.A-6 Quaternary nitride enhancement mode HFET with 260 mS/mm and a threshold voltage of +0.5 V

10:20 AM N. Ketteniss<sup>1</sup>, B. Reuters<sup>1</sup>, B. Holländer<sup>2</sup>, H. Hahn<sup>1</sup>, H. Kalisch<sup>1</sup>, and A. Vescan<sup>1</sup>, <sup>1</sup>GaN Device Technology, RWTH Aachen University, Aachen, GERMANY and <sup>2</sup>Forschungszentrum Juelich GmbH, Juelich, GERMANY

- IV.A-7

Methods for Attaining High Interband Tunneling Current in III-Nitrides

T. A. Growden, S. Krishnamoorthy, D. N. Nath, A. Ramesh, S. Rajan, and P. R. Berger

Department of Electrical and Computer Engineering, The Ohio State University, Columbus, Ohio, USA

- IV.A-8

11:00 AM

11:00 AM

S. Lal<sup>1</sup>, J. Lu<sup>1</sup>, B. Thibeault<sup>1</sup>, S. P. Denbaars<sup>2</sup>, and U. K. Mishra<sup>1</sup>, Department of Electrical and Computer Engineering and Materials Department, University of California, Santa Barbara, California, USA

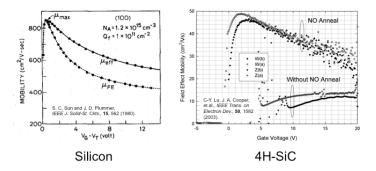

- IV.A-9 Electrical Evidence of Disorder at the SiO2/4H-SiC MOS Interface and its Effect on Electron Transport

11:20 AM S. Swandono, A. Penumatcha, and J. A. Cooper, School of Electrical and Computer Engineering and Birck

Nanotechnology Center, Purdue University, West Lafayette, Indiana, USA

- IV.A-10

11:40 AM

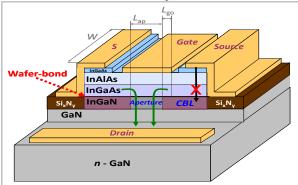

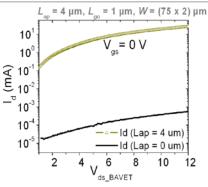

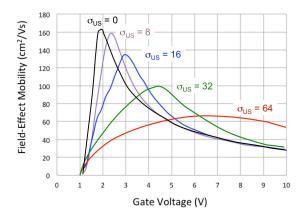

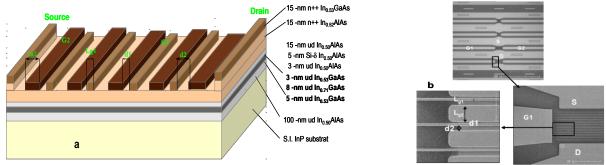

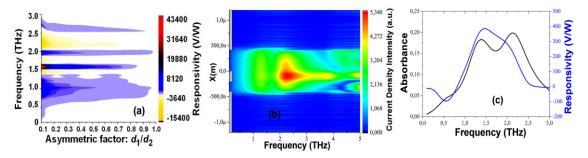

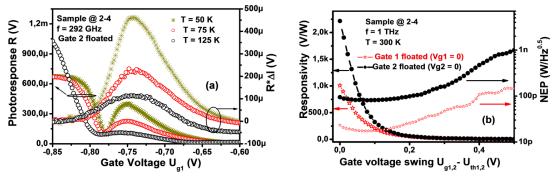

Asymmetric Dual-Grating Gate InGaAs/InAIAs/InP HEMTs for Ultrafast and Ultrahigh Sensitive

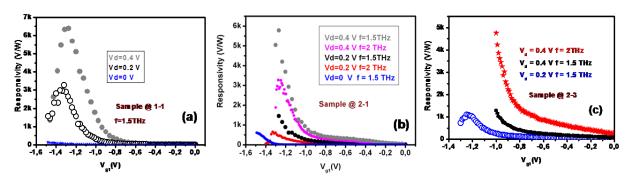

Terahertz Detection

S. Boubanga-Tombet<sup>1</sup>, Y. Tanimoto<sup>1</sup>, T. Watanabe<sup>1</sup>, T. Suemitsu<sup>1</sup>, W. Yuye<sup>2</sup>, H. Minamidev<sup>2</sup>, H. Ito<sup>2</sup>, V. Popov<sup>3</sup>, and T. Otsujj<sup>1</sup>, <sup>1</sup>Research Institute of Electrical Communication, Tohoku University, Aoba-Ku, Sendai, JAPAN, <sup>2</sup>RIKEN Sendai, Aoba-ku, Sendai, JAPAN, and <sup>3</sup>Institute of Radio Engineering and Electronics (Saratov Branch), Saratov, RUSSIA

## Session IV.B. 1/2-Dimensional FETs

171-190

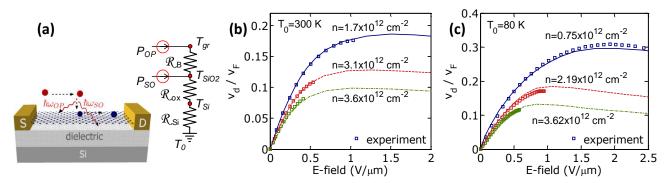

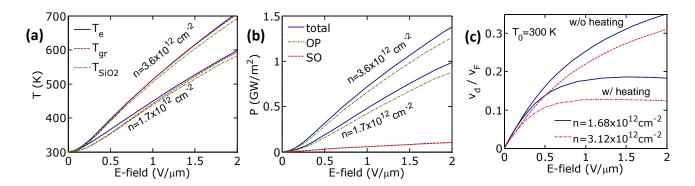

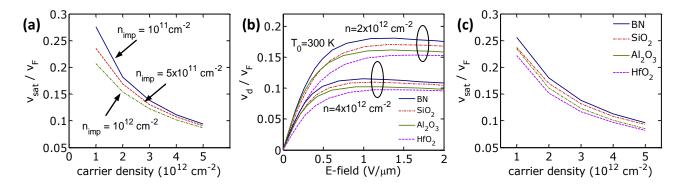

- IV.B-1 Role of Screening, Heating, and Dielectrics on High-Field Transport in Graphene

- 8:20 AM A. Y. Serov, Z.-Y. Ong, V. E. Dorgan and E. Pop, Dept. of Electrical and Computer Engineering, University of Illinois, Urbana-Champaign, Illinois, USA and Micro and Nanotechnology Lab, Urbana Illinois, USA

- IV.B-2 Graphene field-effect transistors with self-aligned spin-on-doping of source/drain access regions

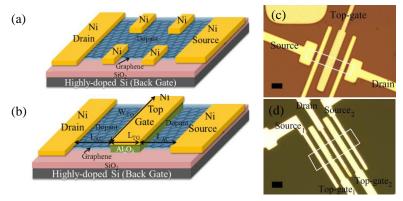

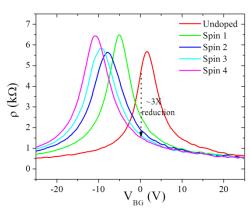

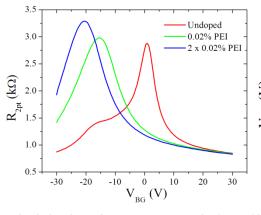

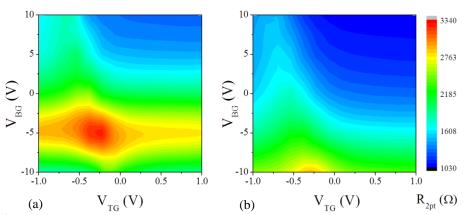

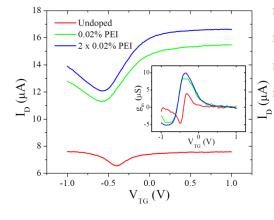

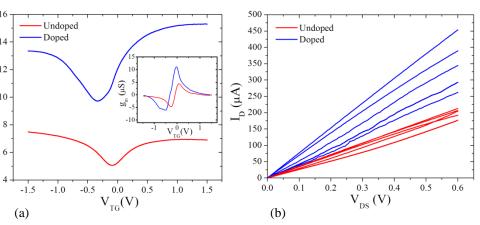

- 8:40 AM H. C. P. Movva<sup>1</sup>, M. E. Ramón<sup>1</sup>, C. M. Corbet<sup>1</sup>, F. S. Chowdhury<sup>1</sup>, G. Carpenter<sup>2</sup>, E. Tutuc<sup>1</sup>, and S. K. Banerjee<sup>1</sup>, <sup>1</sup>Microelectronics Research Center, The University of Texas at Austin, Texas, USA and <sup>2</sup>IBM Research, Austin, Texas, USA

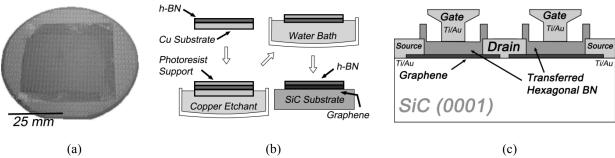

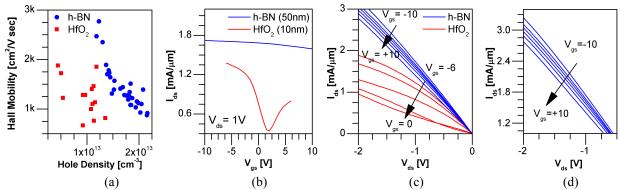

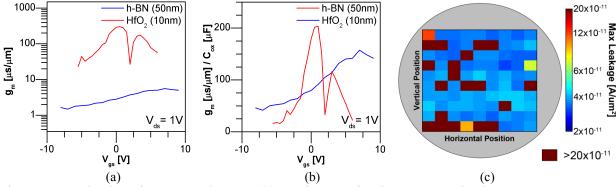

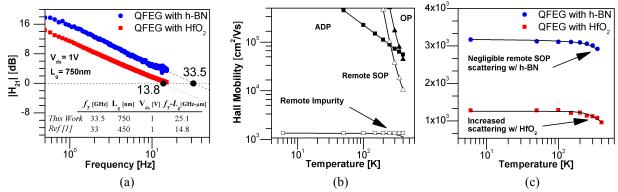

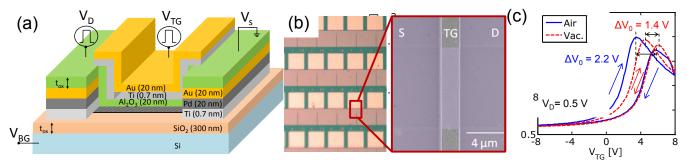

- IV.B-3 High Performance, Large Area Graphene Transistors on Quasi-Free-Standing Graphene Using 9:00 AM Synthetic Hexagonal Boron Nitride Gate Dielectrics

M. J. Hollander, A. Agrawal, M. S. Bresnehan, M. LaBella, K. A. Trumbull, R. Cavalero, S. Datta, and J. A. Robinson. The Pennsylvania State University. University Park. Pennsylvania . USA

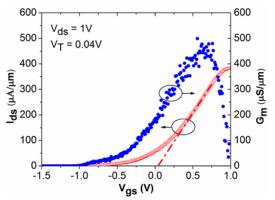

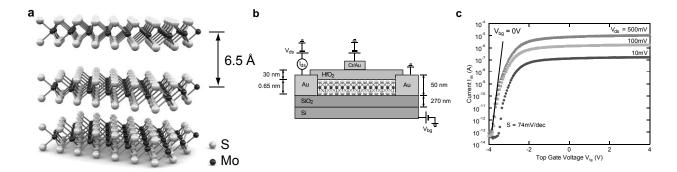

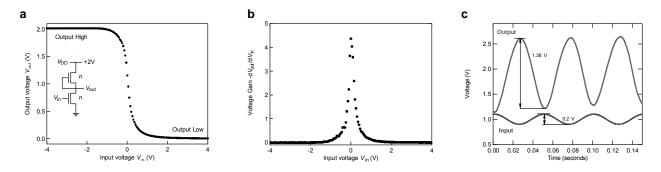

- IV.B-4 MoS<sub>2</sub>-based devices and circuits

- 9:20 AM B. Radisavljevic, D. Krasnozhon, M.B. Whitwick, A. Kis, Electrical Engineering Institute, School of Engineering, EPFL, Lausanne, SWITZERLAND

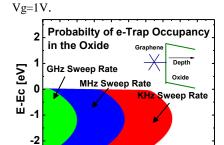

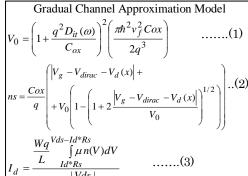

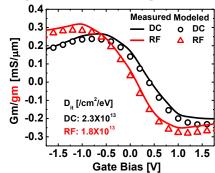

- IV.B-5 Extraction of Near Interface Trap Density in Top Gated Graphene Transistor Using High Frequency Current Voltage Characteristics

H. Madan<sup>1</sup>, M. J. Hollander<sup>1</sup>, J. A. Robinson<sup>2</sup>, and S. Datta<sup>1</sup>, <sup>1</sup>Elec4ical Engineering, The Pennsylvania State University, University Park, Pennsylvania, USA and <sup>2</sup>Material Science and Engineering. The Pennsylvania State University, University Park, Pennsylvania, USA

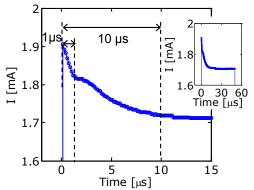

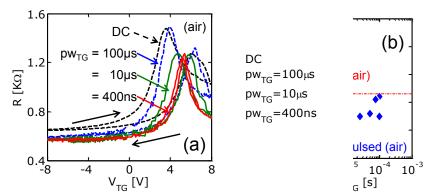

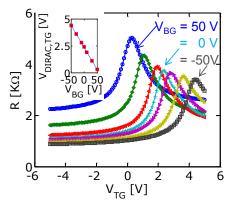

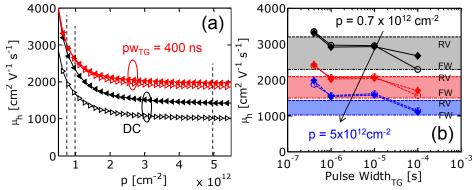

- IV.B-6 Pulsed Nanosecond Characterization of Graphene Transistors

- 10:40 AM E. Carrion, A. Malik, A. Behnam, S. Islam, F. Xiong and E. Pop, Dept. of Electrical and Computer Engineering, University of Illinois, Urbana-Champaign, Illinois, USA and Micro and Nanotechnology Lab, Urbana Illinois, USA

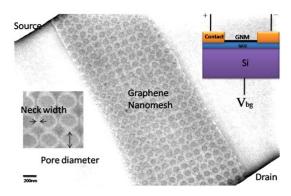

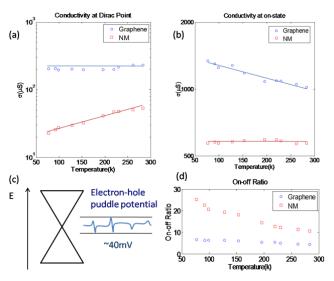

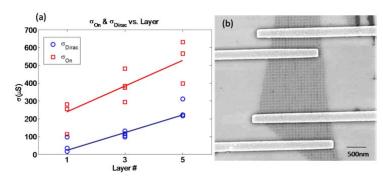

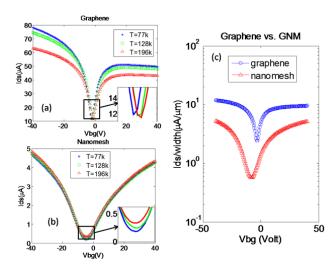

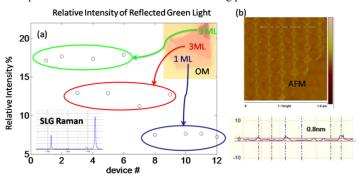

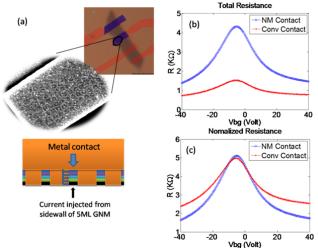

- IV.B-7 Graphene Nanomesh Contacts and Its Transport Properties

- 11:00 AM T. Chu and Z. Chen, ECE Department and Birck Nanotechnology Center, Purdue University, West Lafayette, Indiana, USA

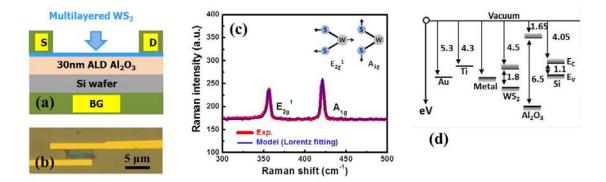

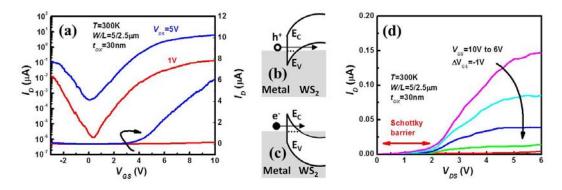

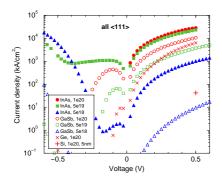

- IV.B-8 First Demonstration of Two-Dimensional WS2 Transistors Exhibiting 105 Room Temperature

11:20 AM Modulation and Ambipolar Behavior

W. S. Hwang<sup>1</sup>, M. Remskar<sup>2</sup>, R. Yan<sup>1</sup>, V. Protasenko<sup>1</sup>, K. Tahy<sup>1</sup>, S. D. Chae<sup>1</sup>, H. Xing<sup>1</sup>, A. Seabaugh<sup>1</sup>, and D. Jena<sup>1</sup>, <sup>1</sup>Department of Electrical Engineering, University of Notre Dame, Notre Dame, Indiana, USA and <sup>2</sup>Solid State Physics Department, Jozef Stefan Institute, Ljubljana, SLOVENIA

IV.B-9

11:40 AM

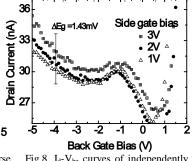

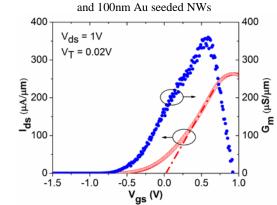

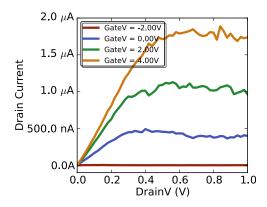

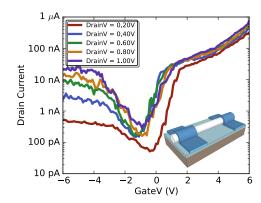

Co. J. Delker<sup>1</sup>, Y. Zi<sup>2</sup>, C. Yang<sup>2,3</sup>, D. B. Janes<sup>1</sup>, <sup>1</sup>School of Electrical and Computer Engineering and Birck

Nanotechnology Center, Purdue University, West Lafayette, Indiana, USA, <sup>2</sup>Department of Physics, Purdue

University, West Lafayette, Indiana, USA, and <sup>3</sup>Department of Chemistry, Purdue University, West Lafayette, Indiana, USA

### Session V.A III-V MOSFETs/FETs

191-208

- V.A-1 High Performance III-V FETs for Low Power CMOS Applications

- 1:30 PM M. Radosavljevic, Intel Corporation, Technology and Manufacturing Group, Hillsboro, Oregon, USA

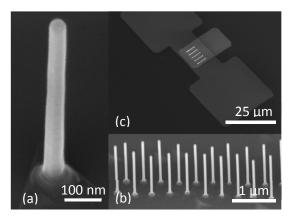

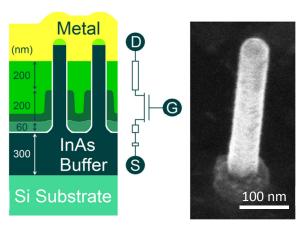

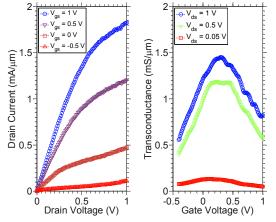

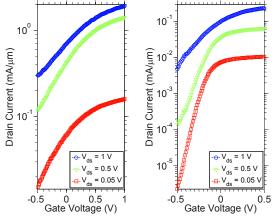

- V.A-2 Vertical InAs Nanowire MOSFETs with  $I_{DS} = 1.34$  mA/ $\mu$ m and gm = 1.19 mS/ $\mu$ m at  $V_{DS} = 0.5$  V

- 2:10 PM K.-M. Persson, M. Berg, M. Borg, J. Wu, H. Sjöland, E. Lind and L.-E. Wernersson, Department of Electricaland Information Technology, Lund University, Lund, SWEDEN

- V.A-3 Possible Observation of Ballistic Contact Resistance in Wide Si MOSFETs

- 2:30 PM A. Majumdar<sup>1</sup> and D. A. Antoniadis<sup>2</sup>, <sup>1</sup>IBM Research Division, T. J. Watson Research Center, Yorktown Heights, New York, USA and <sup>2</sup>Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology, Cambridge, Massachusetts, USA

- V.A-4 Regrown Ohmic Contacts to InxGa1-xAs Approaching the Quantum Conductivity Limit

- 2:50 PM J. J. M. Law, A. D. Carter, S. Lee, A. C. Gossard, M. J. W. Rodwell, ECE and Materials Departments, University of California, Santa Barbara, California, USA

- V.A-5 **Simulation Study of Nanowire Tunnel FETs**

- A. Schenk<sup>1</sup>, R. Rhyner<sup>1</sup>, M. Luisier<sup>1</sup>, and C. Bessir<sup>2</sup>, <sup>1</sup>Integrated Systems Laboratory, ETH Zürich, Zürich, 3:30 PM SWITZERLAND and <sup>2</sup>IBM Research-Zürich, Rüschlikon, SWITZERLAND

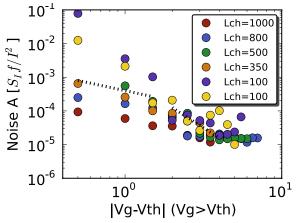

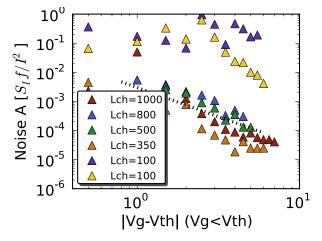

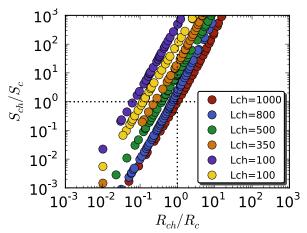

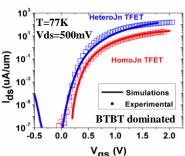

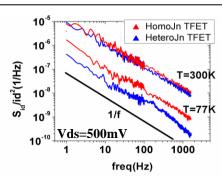

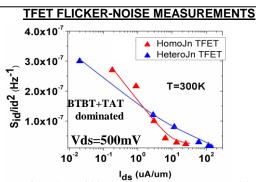

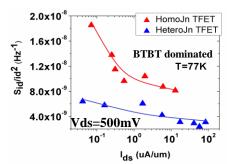

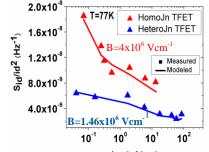

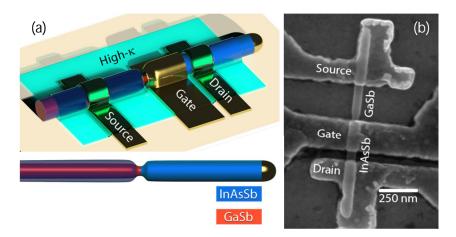

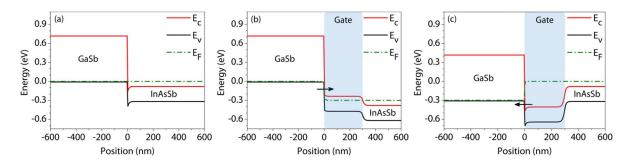

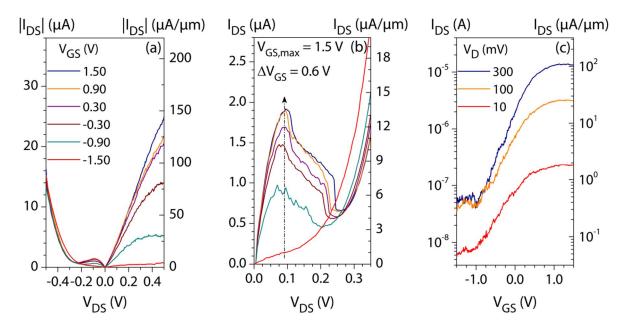

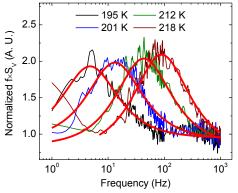

- Flicker Noise Characterization and Analytical Modeling of Homo and Hetero-Junction III-V Tunnel FETs V.A-6 4:10 PM R. Bijesh, D. K. Mohata, H. Liu and S. Datta, Pennsylvania State University, University Park, Pennsylvania,

- V.A-7 High Current Density InAsSb/GaSb Tunnel Field Effect Transistors

- A. W. Dey<sup>1</sup>, B. M. Borg<sup>2</sup>, B. Ganjipour<sup>2</sup>, M. Ek<sup>3</sup>, K. A. Dick<sup>2,3</sup>, E. Lind<sup>1</sup>, P. Nilsson<sup>1</sup>, C. Thelander<sup>2</sup> and L.-E. Wernersson<sup>1</sup>, <sup>1</sup>Dept. of Electrical and Information Technology, <sup>2</sup>Dept. of Solid State Physics and <sup>3</sup>, Division of 4:30 PM Polymer and Materials Chemistry, Lund University, Lund, SWEDEN

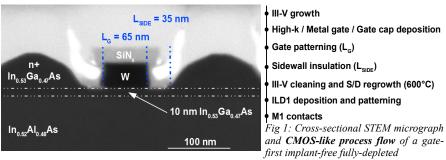

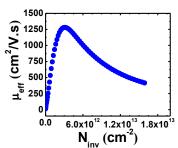

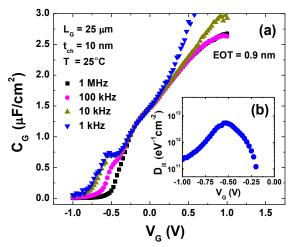

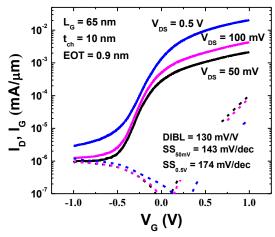

- V.A-8 Gate-first implant-free InGaAs n-MOSFETs with sub-nm EOT and CMOS-compatible process suitable 4:50 PM for VLSI

L. Czornomaz, M. El Kazzi, D. Caimi, C. Rossel, E. Uccelli, M. Sousa, C. Marchiori, M. Richter, H. Siegwart and J. Fompeyrine, IBM Zurich Research Laboratory, Rüschlikon, SWITZERLAND

## Session V.B Spin/Memory Devices

209-222

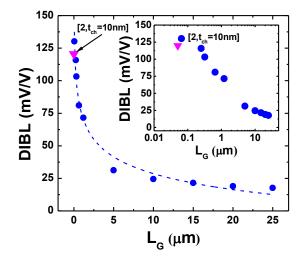

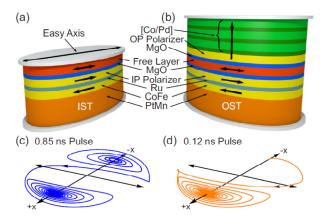

V.B-1 Ultrafast Spin Torque Memory Based on Magnetic Tunnel Junctions with Combined In-plane and Perpendicular Polarizers 1:30 PM

I. N. Krivorotov<sup>1</sup>, G. E. Rowlands<sup>1</sup>, T. Rahman<sup>2</sup>, J. A. Katine<sup>1</sup>, J. Langer<sup>4</sup>, A. Lyle<sup>4</sup>, H. Zhao<sup>2</sup>, J. G. Alzate<sup>5</sup>, A. A. Kovalev<sup>6</sup>, Y. Tserkovnyak<sup>6</sup>, Z. M. Zeng<sup>6</sup>, H. W. Jiang<sup>6</sup>, K. Galatsis<sup>5</sup>, Y. M. Huai<sup>7</sup>, P. Khalili Amiri<sup>5</sup>, K. L. Wang<sup>5</sup> and J.-P. Wang<sup>2</sup>, <sup>1</sup>Physics and Astronomy, University of California, Irvine, California, USA, <sup>2</sup>Electrical and Computer Engineering, University of Minnesota, Minneapolis, Minnesota, USA, 3Hitachi Global Storage Technologies, San Jose, California, USA, <sup>4</sup>Singulus Technologies, Kahl am Main, GERMANY, <sup>5</sup>Electrical Engineering, University of California, Los Angeles, California, USA, <sup>6</sup>Physics and Astronomy, University of California, Los Angeles, California, USA, and <sup>7</sup>Avalanche Technology, Fremont, California, USA

- V.B-2 NanoMagnet Logic

- 2:10 PM W. Porod, P. Li, F. Shah, M. Siddiq, E. Varga, G. Csaba, V. Sankar, G. H. Bernstein, X. S. Hu, M. Niemier, J. Nahas, and A. Orlov, Center for Nano Science and Technology, University of Notre Dame, Notre Dame, Indiana, USA

- V.B-3 **Late News** 2:50 PM

- V.B-4

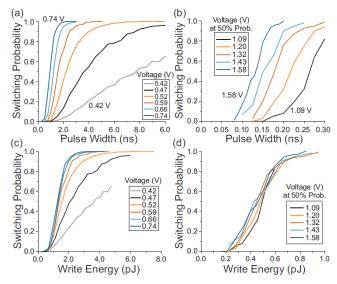

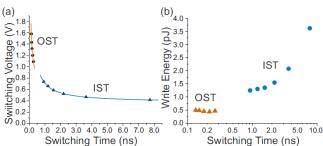

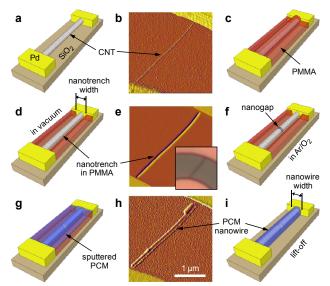

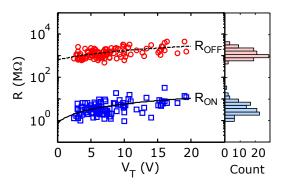

- Nanowire Phase Change Memory with Carbon Nanotube Electrodes

F. Xiong; 1,2,3, M.g-H. Bae 1,2, Y. Dai 1,2, A. D. Liao; A. Behnam 1,2, E. Carrion 1,2, S. Hong; D. Ielmini and E. Pop 1,2,3, Micro & Nanotechnology Lab, Univ. Illinois, Urbana-Champaign, Illinois, USA, Dept. of Electrical & 3:30 PM Computer Engineering, Univ. Illinois, Urbana-Champaign, Illinois, USA, <sup>3</sup>Beckman Institute, Univ. Illinois, Urbana-Champaign, Illinois, USA, and <sup>4</sup>Dipartimento di Elettronica e Informazione, Politecnico di Milano, Milano, ITALY

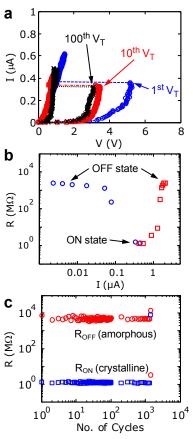

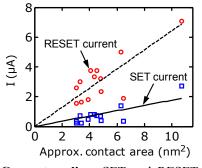

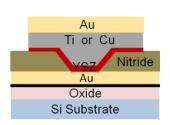

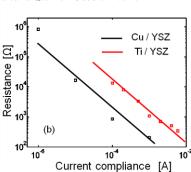

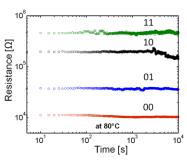

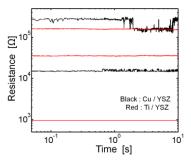

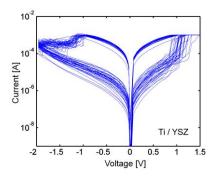

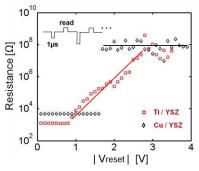

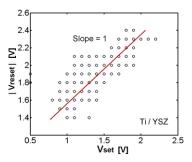

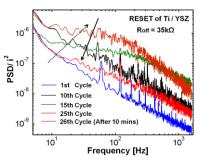

- V.B-5 A very reliable multilevel YSZ resistive switching memory

- Feng Pan, Jaewon Jang, Vivek Subramanian, Department of Electrical Engineering and Computer Sciences. 3:50 PM University of California, Berkeley, California, USA

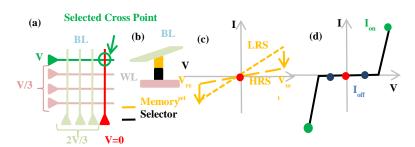

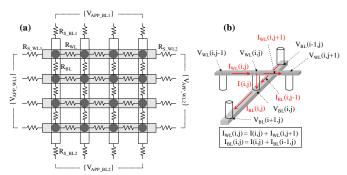

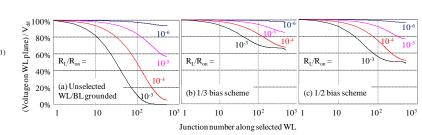

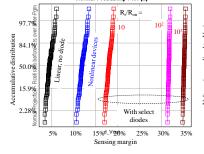

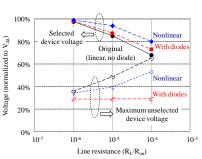

| V.B-6<br>4:10 PM   | A Comprehensive Model for Crossbar Memory Arrays  A. Chen, Z. Krivokapic, and MR. Lin, TD Research, GLOBALFOUNDRIES, Sunnyvale, California, USA                                                                                                                                                                                                                                                |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

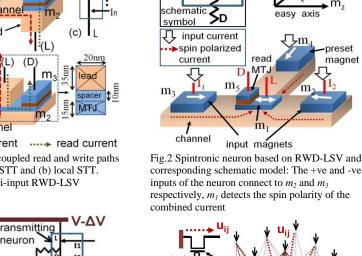

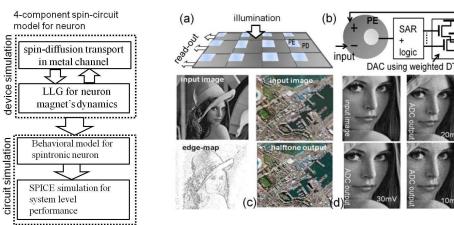

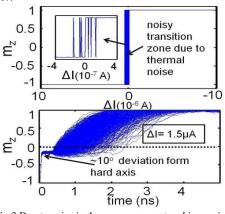

| V.B-7<br>4:30 PM   | Spin Neuron for Ultra Low Power Computational Hardware M. Sharad, G. Panagopoulos and K. Roy, School of Electrical and Computer Engineering, Purdue University, West Lafayette, Indiana , USA                                                                                                                                                                                                  |

| Rump 9             | Sessions 223-224                                                                                                                                                                                                                                                                                                                                                                               |

| R.1<br>8:30 PM     | Wells vs. Sheets vs. Tubes Session Organizers: Joshua Robinson, Penn State and Debdeep Jena, University of Notre Dame                                                                                                                                                                                                                                                                          |

| R.2<br>8:30 PM     | Compound semiconductors on Si: "A Happy Marriage" or "Keep Your Filthy Materials Out Of My Fab"? Session Organizers: Seth Bank, The University of Texas at Austin and Yanning Sun, IBM                                                                                                                                                                                                         |

| Joint D            | RC/EMC Plenary Session 225-226                                                                                                                                                                                                                                                                                                                                                                 |

| 8:30 AM            | Nonpolar and Semipolar GaN Materials and Devices: The Journey So Far James S. Speck, University of California, Santa Barbara                                                                                                                                                                                                                                                                   |

| Session            | NI.A Transistor Modeling 227-234                                                                                                                                                                                                                                                                                                                                                               |

| VI.A-1<br>10:00 AM | Dissipative Quantum Transport in Nanoscale Transistors Jing Guo, Department of ECE, University of Florida, Gainesville, Florida, USA                                                                                                                                                                                                                                                           |

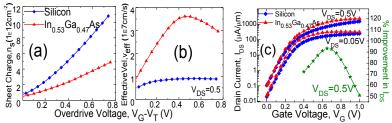

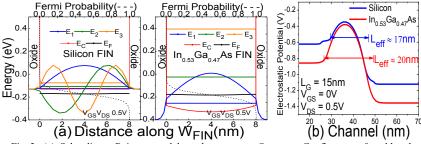

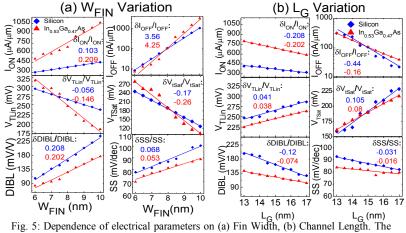

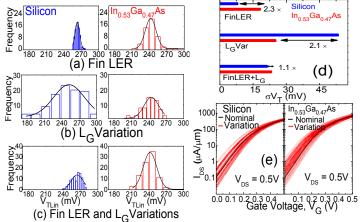

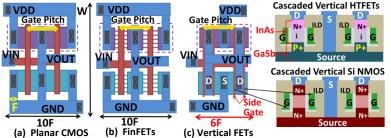

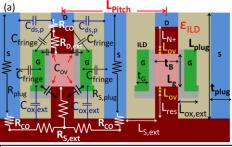

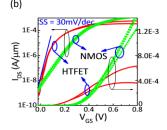

| VI.A-2<br>10:40 AM | <b>Will Strong Quantum Confinement Effect Limit Low VCC Logic Application of III-V FINFETs?</b> A.Nidhi <sup>1</sup> , V.Saripalli <sup>1</sup> , V. Narayanan <sup>1</sup> , Y. Kimura <sup>2</sup> , R. Arghavani <sup>2</sup> and S. Datta <sup>1</sup> , <sup>1</sup> The Pennsylvania State University, University Park, Pennsylvania, USA and <sup>2</sup> Lam Research, California, USA |

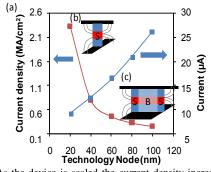

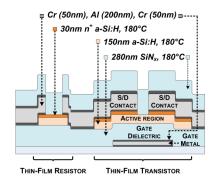

| VI.A-3<br>11:00 AM | <b>Exploration of Vertical MOSFET and Tunnel FET Device Architecture for Sub 10nm Node Applications</b> H. Liu, D. K. Mohata, A. Nidhi, V. Saripalli, V. Narayanan and S. Datta, The Pennsylvania State University, University Park, Pennsylvania, USA                                                                                                                                         |

| VI.A-4<br>11:20 AM | Late News                                                                                                                                                                                                                                                                                                                                                                                      |

| VI.A-5<br>11:40 AM | Late News                                                                                                                                                                                                                                                                                                                                                                                      |

| Session            | NVI.B Thin- Film Devices 235-246                                                                                                                                                                                                                                                                                                                                                               |

| VI.B-1<br>10:00 AM | Organic Thin-Film Transistors for Flexible Displays and Circuits H. Klauk, Max Planck Institute for Solid State Research, Stuttgart, GERMANY                                                                                                                                                                                                                                                   |

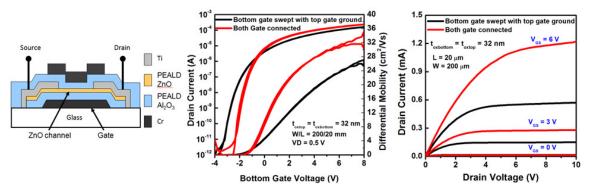

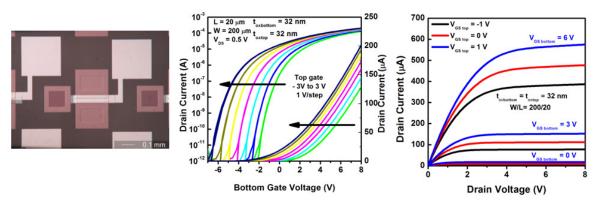

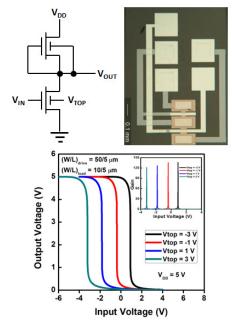

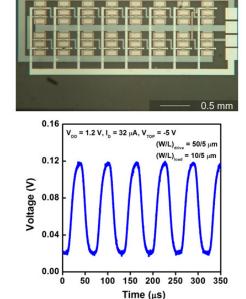

| VI.B-2<br>10:40 AM | <b>Low-Voltage ZnO Double-Gate Thin Film Transistor Circuits</b> Y. V. Li <sup>1,2</sup> , J. I. Ramirez <sup>1,2</sup> , K. G. Sun <sup>1,2</sup> and T. N. Jackson <sup>1,2</sup> , <sup>1</sup> Center for Thin Film Devices and Materials Research Institute and <sup>2</sup> Department of Electrical Engineering, Penn State University, University Park, Pennsylvania, USA              |

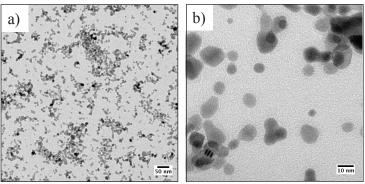

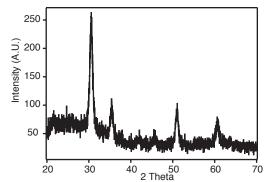

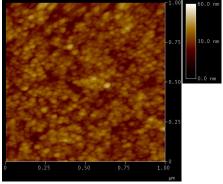

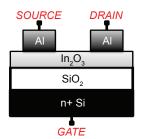

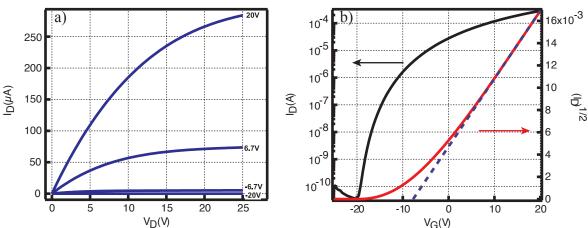

| VI.B-3<br>11:00 AM | <b>High Performance Solution-Processed Thin-Film Transistors Based on In₂O₃ Nanocrystals</b> S. L. Swisher, S. Volkman, K. Braam, J. Jang, and V. Subramanian, Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, California USA                                                                                                                  |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                |

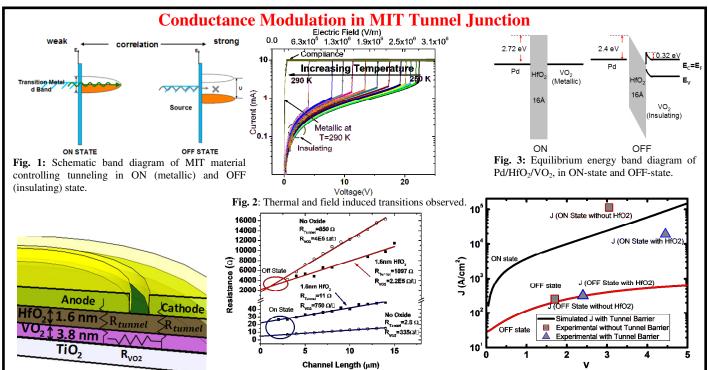

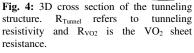

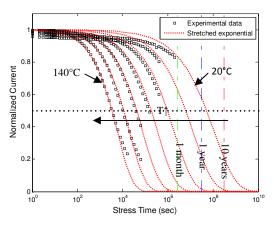

| VI.B-4    | Characterization and Modeling of Metal-Insulator Transition (MIT) Based Tunnel Junctions                                                                                |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.20 414 | E Francisco A Kar <sup>1</sup> N Shukla <sup>1</sup> D Migra <sup>1</sup> D Frank Harbort <sup>1</sup> D Schlam <sup>2</sup> V Canalan <sup>1</sup> K Baha <sup>2</sup> |

E. Freeman<sup>1</sup>, A. Kar<sup>1</sup>, N. Shukla<sup>1</sup>, R. Misra<sup>1</sup>, R. Engel-Herbert<sup>1</sup>, D. Schlom<sup>2</sup>, V. Gopalan<sup>1</sup>, K. Rabe<sup>3</sup>, and S.Datta<sup>1</sup>, <sup>1</sup>Pennsylvania State University, Pennsylvania, USA, <sup>2</sup>Cornell University, Ithaca, New York, USA, and

<sup>3</sup>Rutgers University, New Brunswick, New Jersey, USA

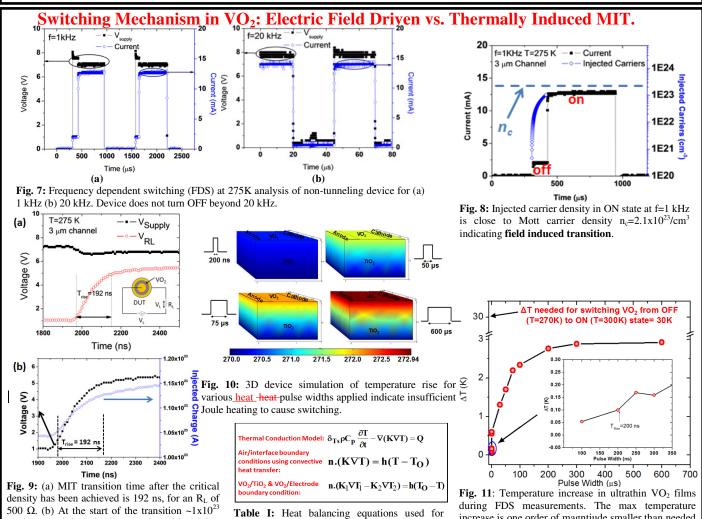

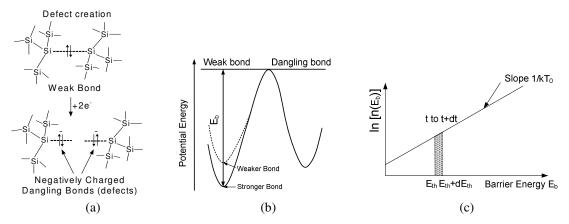

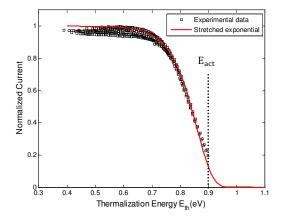

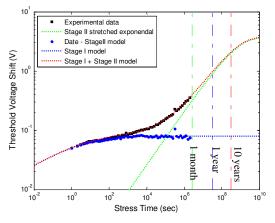

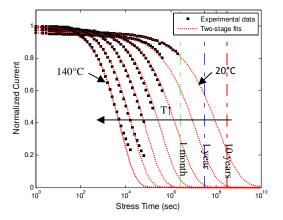

#### VI.B-5 Two-stage Model for Lifetime Prediction of Highly Stable Amorphous-Silicon Thin-Film Transistors 11:40 AM under Low-Gate Field

T. Liu, S. Wagner and J. C. Sturm, Princeton Institute for the Science and Technology of Materials (PRISM), and Department of Electrical Engineering, Princeton University, Princeton, New Jersey, USA

#### Session VII.A **Optoelectronic Devices**

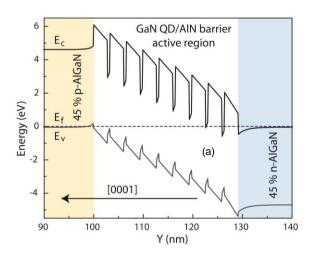

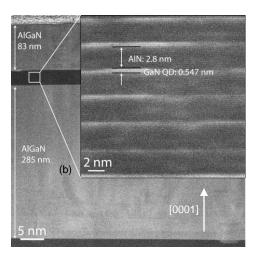

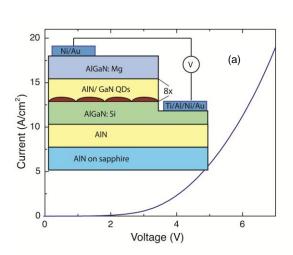

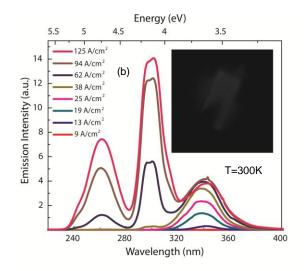

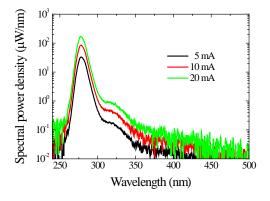

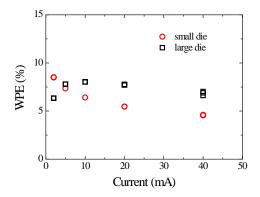

#### VII.A-1 **Tunnel Injection GaN/AIN Quantum Dot UV LED**

1:30 PM J. Verma, P. K. Kandaswamy, V. Protasenko, A. Verma, H. Xing and D. Jena, Department of Electrical Engineering, University of Notre Dame, Notre Dame, Indiana, USA

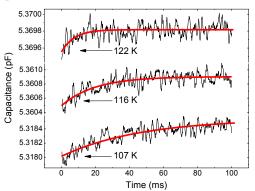

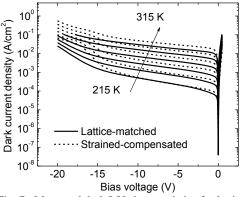

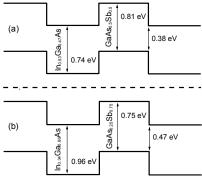

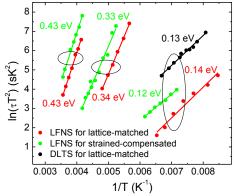

#### VII.A-2 Characterization and Impact of Traps in Lattice-Matched and Strain-Compensated In1-xGaxAs/GaAs1-1:50 PM vSbv Multiple Quantum Well Photodiodes

W. Chen<sup>1</sup>, B. Chen<sup>2</sup>, J. Yuan<sup>2</sup>, A. Holmes<sup>2</sup>, and P. Fav<sup>1</sup>, <sup>1</sup>University of Notre Dame, Notre Dame, Indiana, USA and <sup>2</sup>University of Virginia, Charlottesville, Virginia, USA

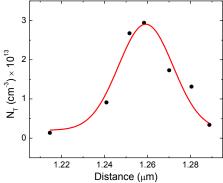

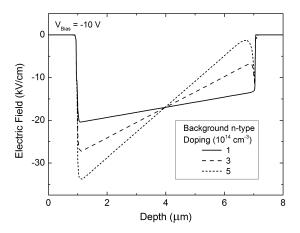

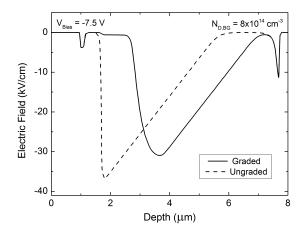

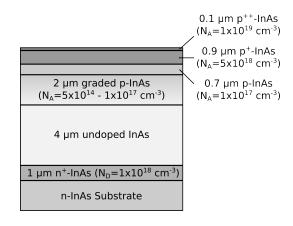

#### InAs Avalanche Photodiode with Improved Electric Field Uniformity VII.A-3

S. J. Maddox<sup>1</sup>, W. Sun<sup>2</sup>, Z. Lu<sup>2</sup>, H. P. Nair<sup>1</sup>, J. C. Campbell<sup>2</sup>, S. R. Bank<sup>2</sup>, <sup>1</sup>Department of Electrical and Computer Engineering, The University of Texas at Austin, Austin, Texas, USA and <sup>2</sup>Department of Electrical 2:10 PM and Computer Engineering, University of Virginia, Charlottesville, Virginia, USA

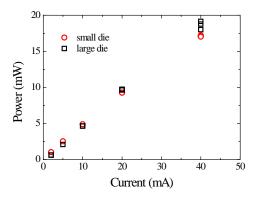

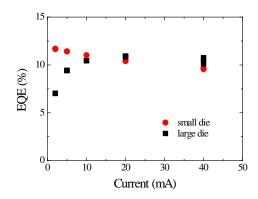

#### <278 nm Deep Ultraviolet LEDs with 11% External Quantum Efficiency VII.A-4

M. Shatalov<sup>1</sup>, W. Sun<sup>1</sup>, A. Lunev<sup>1</sup>, X.g Hu<sup>1</sup>, A. Dobrinsky<sup>1</sup>, Y. Bilenko<sup>1</sup>, J. Yang<sup>1</sup>, M. Shur<sup>2</sup>, R. Gaska<sup>1</sup>, C. Moe<sup>3</sup>, 2:30 PM G. Garrett<sup>3</sup>, and M. Wraback<sup>3</sup>, <sup>1</sup>Sensor Electronic Technology, Inc., Columbia, South Carolina, USA, <sup>2</sup>Department of Electrical, Computer, and Systems Engineering and Center of Integrated Electronics, Rensselaer Polytechnic Institute, New York, USA, and 3U.S. Army Research Laboratory, Adelphi, Maryland, USA

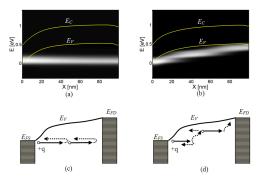

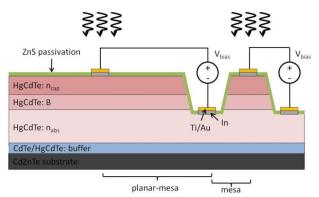

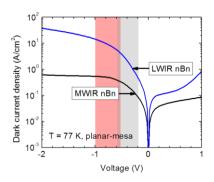

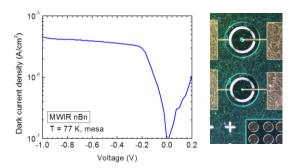

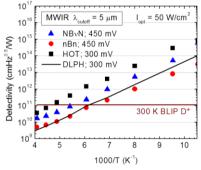

#### Unipolar Barrier-Integrated HgCdTe Infrared Detectors VII.A-5

A. M. Itsuno<sup>1,3</sup>, J. D. Phillips<sup>1</sup>, and S. Velicu<sup>2</sup>, <sup>1</sup>Department of Electrical Engineering, University of Michigan-Ann 2:50 PM Arbor, Ann Arbor, Michigan, USA and EPIR Technologies, Inc., Bolingbrook, Illinois, USA

VII.A-6 **Late News** 3:10 PM

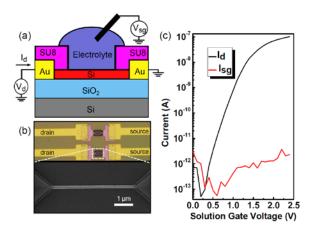

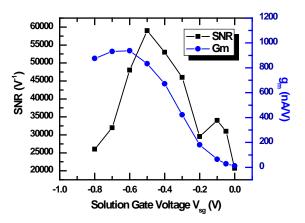

## Session VII.B Biological Devices

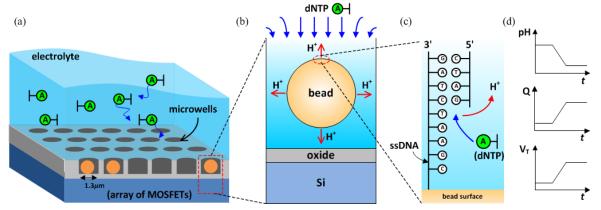

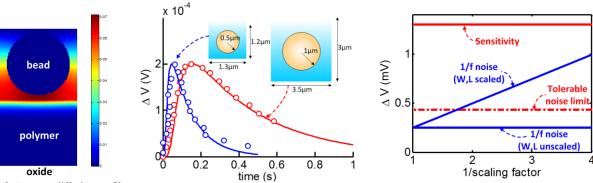

#### VII.B-1 Physics and Scaling Prospects of pH-Based Genome Sequencers

1:30 PM J. Go and M. A. Alam, School of Electrical and Computer Engineering, Purdue University, West Lafayette, Indiana, USA

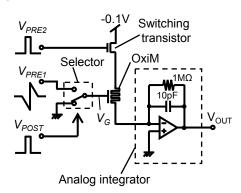

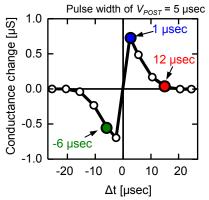

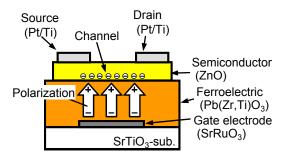

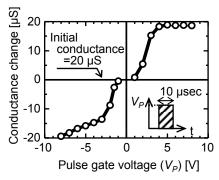

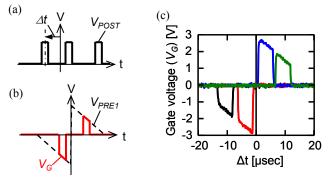

#### Biologically-inspired Learning Device using Three-terminal Ferroelectric Memristor VII.B-2

M. Ueda<sup>1</sup>, Y. Kaneko<sup>1</sup>, Y. Nishitani<sup>1</sup>, T. Morie<sup>2</sup> and E. Fujii<sup>1</sup>, <sup>1</sup>Advanced Technology Research Laboratory, 1:50 PM Panasonic Corporation, Seika-cho, Soraku-gun, Kyoto, JAPAN and <sup>2</sup>Graduate School of Life Science and Systems Engineering, Kyushu Institute of Technology, Wakamatsu-ku, Kitakyushu, JAPAN

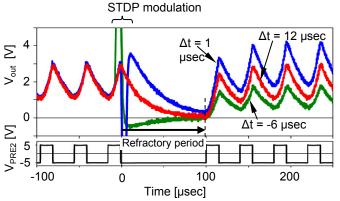

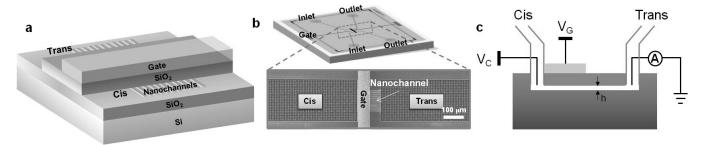

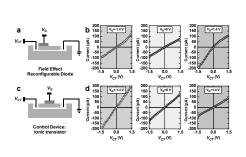

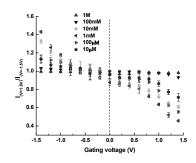

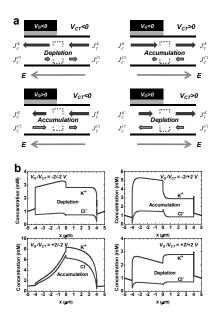

#### VII.B-3 Fabrication and Characterization of Field Effect Reconfigurable Nanofluidic Ionic Diodes: Towards **Digitally-Programmed Manipulation of Biomolecules** 2:10 PM

W. Guan<sup>1</sup>, R. Fan<sup>2</sup>, and M. A. Reed<sup>1,3</sup>, <sup>1</sup>Department of Electrical Engineering, <sup>2</sup> Biomedical Engineering, and <sup>3</sup>Applied Physics, Yale University, New Haven, Connecticut, USA

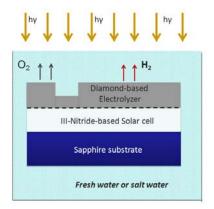

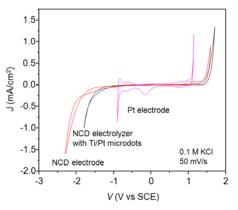

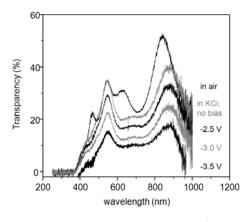

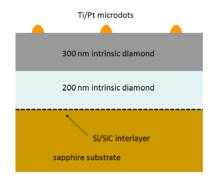

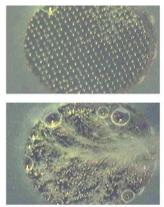

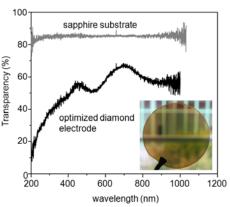

| VII.B-4<br>2:30 PM | Transparent Diamond-based Electrolyzer for Integration with Solar Cell C. Pietzka, Z. Gao, Y. Xu, and E. Kohn, Inst. of Electron Devices and Circuits, Ulm University, Ulm, GERMANY |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VII.B-5<br>2:50 PM | Late News                                                                                                                                                                           |

| VII.B-6<br>3:10 PM | Late News                                                                                                                                                                           |

(Dean's Hall I & II)

# **Plenary Session**

# Monday AM, June 18<sup>th</sup>, 2012

Session Chairs: Miguel Urteaga, Teledyne Scientific and Suman Datta, Penn State

#### 8:20 AM Welcoming Remarks

Presentations: IEEE Fellows, Best Student Paper Awards, and IEEE EDS

#### 8:50 AM I.-1 Plenary Paper

#### Mapping a Path to the Beyond-CMOS Technology for Computation

I. A. Young, Components Research, Intel Corporation, Hillsboro, Oregon, USA

#### 9:50 AM Break

#### 10:10 AM I.-2 Plenary Paper

#### Solid-State Electronics and Single-Molecule Biophysics

K. Shepard, Department of Electrical Engineering, Columbia University, New York, New York, USA

#### 11:10 AM I.-3 Plenary Paper

#### **Advanced Device Technologies for Defense Systems**

J. C. Zolper, Raytheon Company, Waltham, Massachusetts, USA

## Mapping a Path to the Beyond-CMOS Technology for Computation.

Ian A. Young

Components Research, Intel Corporation, Hillsboro, Oregon, USA.

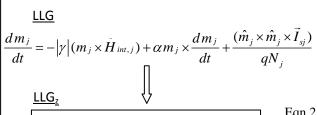

The CMOS device technology used for computation is at an inflexion point. Although this is the technology which enabled the Semiconductor industry to make vast progress for the past 30-plus years, it is likely to see challenges going beyond the ten year horizon, particularly with regard to device scaling and energy efficiency. Thus it is extremely important for the semiconductor industry to search for a new device which can carry us to the beyond CMOS era as soon as possible. Currently, researchers are exploring novel device concepts and new information tokens as an alternative for CMOS technology. Examples of areas being actively researched are; quantum electronic devices, such as the tunneling FET, and devices based on spintronics and nano-magnetics. It is clear that choices will need to be made in the next few years to identify viable alternatives for CMOS by 2020. In order to achieve such a goal, benchmarking methodology and metrics need to be defined urgently to guide the research.

This paper describes a methodology for benchmarking beyond CMOS exploratory devices for computation using metrics that can provide insights about the device fundamental operation. A more detailed investigation of circuits based upon two beyond-CMOS devices is given in the paper. First tunneling FET (TFET) circuits are compared to low power CMOS circuits. Then the All-Spin Logic device (ASLD) is described and a spin circuit theory based simulator is used to show the functional transient operation of an all spin logic circuit.

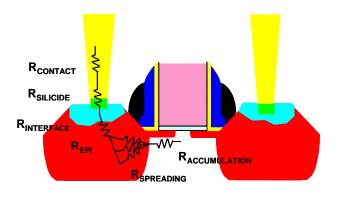

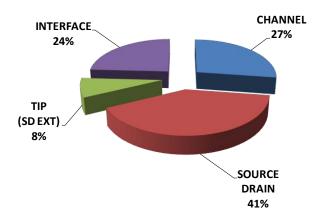

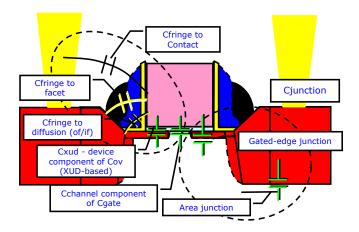

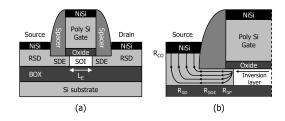

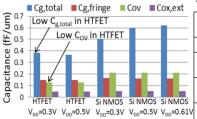

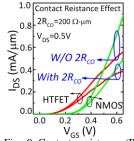

#### I. BENCHMARKING BEYOND-CMOS DEVICES

The challenges of CMOS logic scaling, operating with ever lower power supply voltage to enable more energy efficient logic/computation, are more than the intrinsic transport delay of the signal propagation through the source and drain of the device and it's "on" drive current to off-state leakage ratio. There are extrinsic resistance and capacitance of the device (figure 1 (a) and (b)) together with the circuit interconnect for connecting MOSFETs to form logic gates and connecting the gates to implement the logic. These are increasing and will become a major contributor to circuit delay and energy [1]. Addressing these resistances and capacitances as dimensions scale is going to be critically important to ensure continued improvements in CMOS delay and energy.

The extrinsic resistance and capacitance is not only a challenge for CMOS, it is also a challenge for any electronic charge based switch since it also requires electron transport to charge the interconnect between devices. Even if the new device is extremely small, which is good for reducing the length of the interconnect between devices, the requirement of charging the interconnect above the switching threshold voltage can limit the benefits of a new switch device. Power delivery is also an issue that is often ignored when researching new switch device alternatives to CMOS, especially for low voltage devices. This can lead to misleading results.

Benchmark circuits for the beyond-CMOS devices that have been proposed are the inverter and the combinatorial logic such as 2-input NAND, 1 bit Adder and the 32 bit Adder [2]. In addition to combinatorial logic, a state element is required for the MUX and DEMUX circuits. The MUX/DEMUX and state element functions are needed in order to implement the fundamental logic unit in computing, a finite state machine such as an Arithmetic Logic Unit (ALU). Computational performance, power (efficiency), area and scaling can be compared with these benchmark circuits. Also the interconnect solution (means of signal propagation, speed and power) must be investigated when the signal token is not charge.

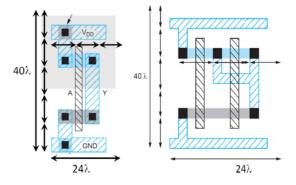

To estimate the extrinsic parasitics (and the device density) for a charge-based device you need to do the device and circuit layout (figure 2). The semiconductor process generations are labeled by the critical lithography size described by the DRAM's half-pitch F. Scalable design rules are formulated in units of maximum mask misalignment  $\lambda$ , where typically  $\lambda = F/2$ . The pitch of metal 1 in a contacted transistor for example is  $p_m = 8\lambda$ . Since the metal 1 contacted transistor pitch scales with the process generation, we approximately obtain that the metal 1 device pitch is  $p_m = 4F$ . Since all the logic circuits (even spintronic circuits) need metal contacts at the terminals of their logic gates, their size will be determined by the metallization pitch much more than by their intrinsic device sizes. The layout area of the circuits can be estimated by drawing layouts for the most important

lines (diffusion, transistor gate ("poly"), metal 1). In most cases the contacted pitch for all these lines proves to be  $8\lambda$  =4F. From these layout principles, sizes of the inverter with fanout of 4, 2-input NAND fanout-1, and 1b and 32b adder can be calculated for the beyond-CMOS switches [2] and are summarized in Table I.

Switching time and energy must be calculated for a device, taking into account whether charge, magnetization, electron spin, or any other quantity serves as the signal token. In some cases when the beyond-CMOS device does not use charge as the signal token, a charge-based clocking control might be required to enable the signal to propagate through the logic or to cut off the current supply when no logic operation is occurring, and therefore the power consumed by the clocking must be accounted for in the correct calculation.

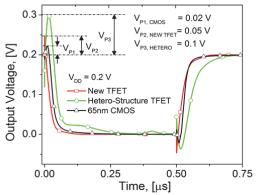

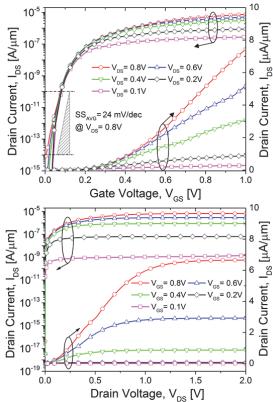

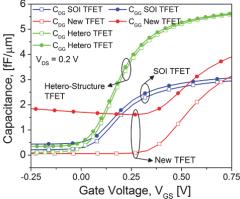

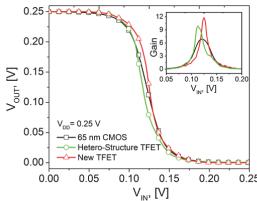

#### II. TFET CIRCUITS

TFET and CMOS circuits were compared under low supply voltage operation (0.25-0.50V) using TFET and MOSFET transistor models that were extracted from atomistic and device simulations respectively, together with an interconnect model to predict the parasitic capacitive output loading from the interconnect [3]. Circuit simulations were performed for the inverter, NAND, and NOR basic logic building blocks and the simulation results were combined to predict a typical microprocessor logic path delay, its switching energy and standby power. For the CMOS analysis, high performance (low-Vt), low operating power / low standby power (high-Vt) devices were used to generate different standby power curves by sweeping supply voltage, while TFET results were achieved by varying Vt (gate work-function) and supply voltage. As the switching energy target is decreased by lowering power supply, CMOS performance degrades rapidly since it moves into the sub-threshold region of operation. In this operating region (Vdd ~ 0.35V), the TFET provides >8x performance advantage over CMOS at the same standby power and switching energy as summarized in Table II. The use of III-V broken gap heterojunctions in the TFET will improve its performance [4]; however the implications of scaling to technology nodes beyond 2020 needs to be explored.

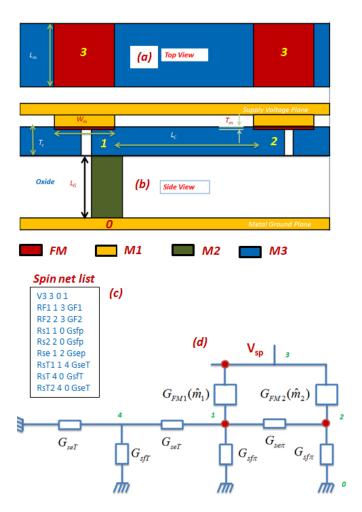

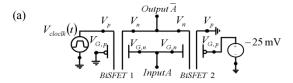

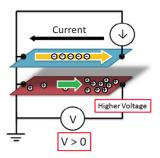

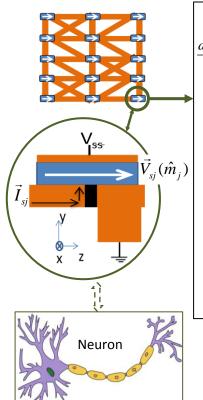

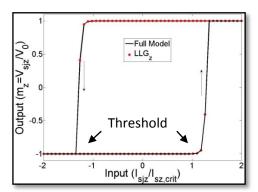

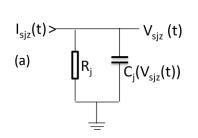

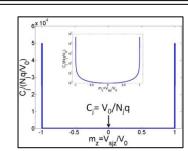

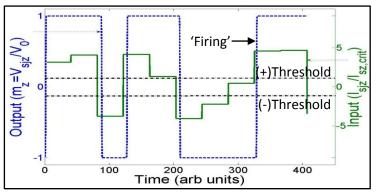

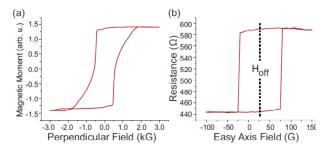

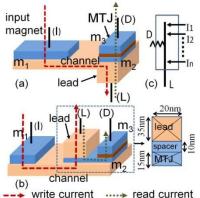

#### III. ALL SPIN LOGIC CIRCUITS

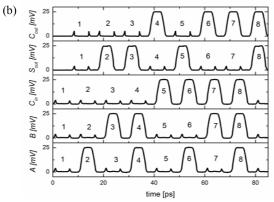

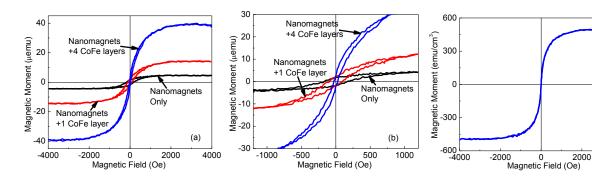

A lateral spin injection-detection device proposed recently is the all spin logic device (ASLD). The device consists of two nanomagnets communicating via a non-magnetic channel [5] as shown in figure 3 (a) and (b). Currents through the magnets create populations of spin polarized carriers underneath them and setup spin diffusion (or drift) currents through the channel. The direction of this spin current is determined by the densities of spin polarized carriers under the two magnets. If a ground terminal is set near the first input magnet, it can be shown that it acts as a fixed magnetic terminal, while the second magnet responds to the spin diffusion current, depending on the applied voltages. For a positive voltage applied to both the magnets, the device acts like an inverting gate, where the output becomes a logical opposite of the input magnetization. For negative applied voltages, the output becomes a copy of the input magnetization. The sectioned structure of the spin diffusion channel is required to isolate spin logic gates, where the interconnection between gates (concatenation) is achieved by connecting them with a spin diffusion channel. The non-reciprocity of (input to output signal transport) ASLD comes from an asymmetry in the device due to the asymmetric location of the ground terminal. This can also be achieved via other structural techniques.

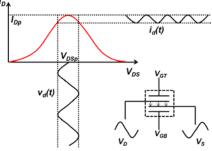

Spin circuit simulation modeling with thermal effects [6] (figure 3 (c) and (d) and figure 4), predicts the variable and asymmetric transient delay of an ASLD based all spin logic circuit. The ASLD has an energy-delay metric of approximately 30 fJ/bit and can operate with up to 2 GHz clocking rate while having zero leakage power (ignoring overheads) with existing nominal material parameters [6]. Compared to a CMOS technology with 60 nW of idle power per transistor, non-volatile spin logic has 0W idle power in the hold state with a 7 year retention time. This will outperform CMOS logic in idle power by several orders of magnitude. However the energy-delay metric of the ASLD will need to be improved with enhanced spin-electrical transduction methods, materials and anisotropy engineering, so that it could achieve the performance (computational efficiency) needed for a beyond-CMOS device.

### **References:**

- [1] I. Young, "MOSFET Extrinsic Parasitic Elements", Short Course, IEDM, December 2011.

- [2] K. Bernstein, et al., "Device and Architecture Outlook for Beyond-CMOS Switches", Proceedings IEEE v. 98, pp. 2169-84 (2010).

- [3] U. Avci, et al., "Comparison of Performance, Switching Energy and Process Variations for TFET and MOSFET Logic", Symposium on VLSI Technology, June 14-16<sup>th</sup>, 2011, Page(s): 124 125.

- [4] U. Avci, et al, "Understanding the Feasibility of Scaled III-V TFET for Logic By Bridging Atomistic Simulations and Experimental Results" Symposium on VLSI Technology, June 12-15<sup>th</sup>, 2012.

- [5] S. Srinivasan, et al., "All Spin Logic Device with Inbuilt Non-reciprocity, "IEEE T-MAG, vol.47, no.10, pp.4026-4032, Oct. 2011

- [6] S. Manipatruni, et al, "Circuit Theory for Analysis and Design of Spintronic Integrated Circuits", accepted for publication in IEEE T-CAS.

Figure 1(a). Sources of MOSFET Extrinsic Resistance and its breakdown relative to the channel resistance.

Figure 1(b). MOSFET Extrinsic Capacitance

Figure 2. Layout and area estimation for an inverter and a 2-input NAND gate.

|          | Device | INVFO4 | NAND2 | Adder1 | Adder32 |

|----------|--------|--------|-------|--------|---------|

| CMOS HP  | 30     | 792    | 360   | 3780   | 181440  |

| CMOS LP  | 30     | 792    | 360   | 3780   | 181440  |

| IIIvTFET | 30     | 792    | 360   | 3780   | 181440  |

| HJTFET   | 30     | 792    | 360   | 3780   | 181440  |

| gnrTFET  | 30     | 792    | 360   | 3780   | 181440  |

| GpnJ     | 108    | 390    | 162   | 2430   | 116640  |

| BisFET   | 30     | 792    | 360   | 3780   | 181440  |

| SpinFET  | 30     | 792    | 360   | 3780   | 181440  |

| STT/DW   | 20     | 120    | 30    | 630    | 30240   |

| STMG     | 81     | 121    | 121   | 547    | 26244   |

| STTtriad | 81     | 486    | 121   | 1640   | 78732   |

| STOlogic | 81     | 121    | 121   | 547    | 26244   |

| ASLD     | 81     | 121    | 121   | 364    | 17496   |

| SWD      | 81     | 121    | 121   | 182    | 8748    |

| NML      | 162    | 243    | 243   | 1093   | 52488   |

Table I. Estimate of size of logic circuits in units of  $F^2$  for the beyond-CMOS switches described in [2].

| TFET @0.35V  | Stage      | Switching   | Leakage    |

|--------------|------------|-------------|------------|

| 11-E1 @0.55V | Delay (ps) | Energy (fJ) | Power (nW) |

| INV (FO=3)   | 105        | 0.26        | 0.37       |

| NAND (FO=3)  | 149        | 0.32        | 0.57       |

| NOR (FO=3)   | 158        | 0.34        | 0.54       |

| Combined     | 129        | 0.29        | 0.46       |

|              |            |             |            |

| CMOS @0.3V   | Stage      | Switching   | Leakage    |

| CIVIOS @0.3V | Delay (ps) | Energy (fJ) | Power (nW) |

| INV (FO=3)   | 830        | 0.25        | 0.37       |

| NAND (FO=3)  | 1364       | 0.32        | 0.56       |

|              | 4000       | 0.22        | 0.53       |

| NOR (FO=3)   | 1389       | 0.33        | 0.55       |

Table II. Comparison of TFET and CMOS results at low voltage, where they have same standby power (0.5nW) and switching energy (0.3fJ). At this point, TFET has 8x higher performance.

Figure 4. a) Transient self-consistent simulation of a spin circuit device b) Trajectory of the magnetic moment of the nanomagnets

Figure 3.

A lateral spin logic device comprised of two nanomagents and non-magnetic channels. Channel connecting node 1 to node 2 acts as an interconnect between the two nano-magnets transporting spin polarized current.

- (a) Top view of an all spin logic device.

- (b) Side view of a lateral all spin logic device.

- (c) Netlist of the circuit model that can be parsed by a spin Modified Nodal Analysis algorithm to simulate.

- (d) Circuit model of spin logic device.

## **Solid-State Electronics and Single-Molecule Biophysics**

#### **Ken Shepard**

Department of Electrical Engineering, Columbia University, New York, NY 10027 USA Phone: +1-646-205-0438; Fax: +1-212-932-9421; E-mail: shepard@ee.columbia.edu

Biomolecular systems are traditionally studied using ensemble measurements and fluorescence-based detection. Among the most common *in vitro* applications are DNA microarrays to identify target gene expression profiles [1] and enzyme-linked immunosorbent assays (ELISA) to identify proteins [2]. While much can be determined with ensemble measurements, scientific and technological interest is rapidly moving to single-molecule techniques. When probing at the single-molecule level, observations can be made about the inter- and intramolecular dynamics that are usually hidden in ensemble measurements. In molecular diagnostic, single-molecule techniques often do not require amplification and simplify sample preparation. The most popular single-molecule techniques based on fluorescence [3, 4] are fundamentally limited in resolution and bandwidth by the countable number of photons emitted by a single fluorophore (typically on the order of 2500 photons/sec). Instrumentation is complex, expensive, and large-form-factor. Furthermore, most optical probes photobleach, limiting observation times and pump powers. Single-molecule measurements of the kinetics of fast biomolecular processes are often unavailable through fluorescent techniques, as they lack the required temporal resolution.

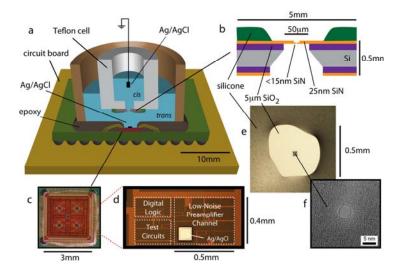

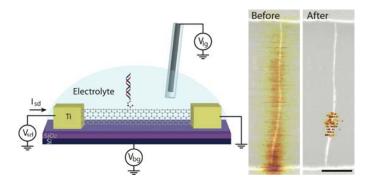

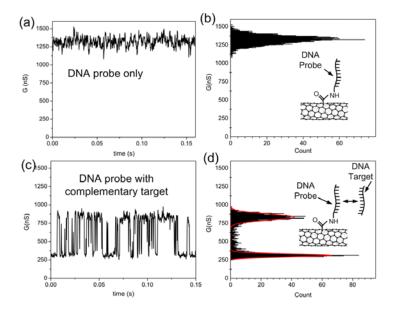

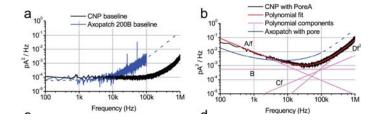

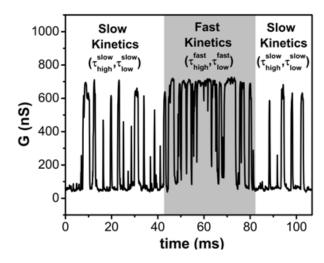

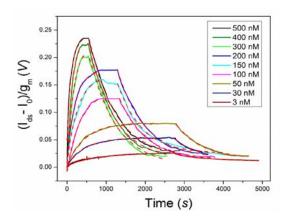

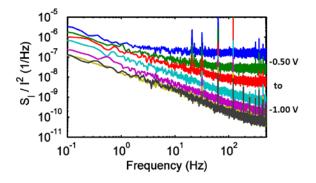

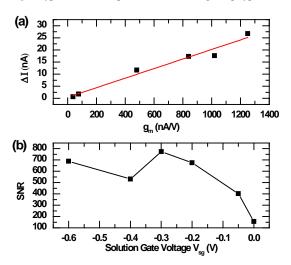

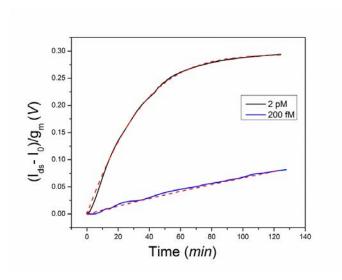

Solid-state nanoscale devices, which are now on the scale of individual molecules, now provide a unique opportunity to transduce the behavior of single molecules to electrons without photons as an intermediary. Solid-state nanopores represent one such technique, which can monitor when a single molecule translocates through a nanoscale pore in a thin dielectric membrane [5]. In our own recent work, we have shown how these solid-state nanopores can be integrated with CMOS electronics to significantly improve the fidelity of nanopore measurements[6]. Fig. 1 shows this integrated configuration. Measured noise spectra are shown in Fig. 2 and compared with started rack-mounted electrophysiological amplifiers. Fig. 3 shows typical time domain waveshapes of DNA molecules translocating through these pores. Another recent technique is based on attaching biomolecules directly to a defect in a carbon nanotube field-effect transistor, which is sensitive to local charge density down to the single molecule level[7]. Fig. 4 shows this configuration. Fig. 5 shows typical time-domain waveshapes for the tube conductance in the presence of DNA-DNA binding. Fig. 6 shows the typical dynamic disorder observed in these studies in which there are periods of time characterized by different microscopic kinetics. Both nanopore and fieldeffect sensors have two essential attributes for single-molecule detection, transistor action in the sensing platform and a very localized region of charge sensitivity in the detector. By providing direct interfaces to the solid-state, much higher bandwidth of detection can be achieved than in fluorescence-based approaches. In addition to improving the fidelity of the electronic interfaces, integrating these sensors with CMOS electronics allows for highly multiplexed arrays and parallelism at least comparable with what is achieved with fluorescence-based approaches but with dramatically smaller and less expensive instrumentation.

- [1] M. Schena, et al., Science, vol. 270, pp. 467-470, Oct 1995.

- [2] E. Engvall and P. Perlmann, *The Journal of Immunology*, vol. 109, pp. 129-135, July 1, 1972 1972.

- [3] E. A. Jares-Erijman and T. M. Jovin, Nat Biotech, vol. 21, pp. 1387-1395, 2003.

- [4] J. Eid, Science, vol. 323, pp. 133-138, 2009.

- [5] C. Dekker, Nat Nano, vol. 2, pp. 209-215, 2007.

- [6] J. K. Rosenstein, et al., Nat Meth, vol. 9, pp. 487-492, 2012.

- [7] S. Sorgenfrei, et al., Nature Nanotechnology, vol. 6, pp. 125-131, Feb 2011.

**Figure 1.** (a) Graphical representation of the compact nanopore measurement platform. (b) an illustrated cross-section of the low-capacitance thin membrane chip (c) optical micrograph of the 8-channel CMOS voltage-clamp current preamplifier (d) a magnified image of one preamplifier channel (e) an optical image of a solid-state silicon nitride membrane chip mounted in the fluid cell (f) a TEM image of a 4nm-diameter nanopore

**Figure 4.** Carbon nanotube FET system illustration and (b) scanning gate microscopy images before and after oxidation

**Figure 5.** Carbon nanotube FET time-domain measurements showing the two-level response to single-molecule hybridizations

978-1-4673-1164-9/12/\$31.00 ©2012 IEEE

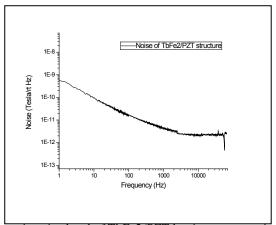

**Figure 1.** Current noise spectra for nanopores. (a) Input-referred open headstage current noise spectrum for integrated nanopore. Also shown is the measured open-headstage of an Axopatch 200B. (b) Measured noise floor of the integrated amplifier together with a solid-state nanopore.

**Figure 3.** A presentation of intra-event structure observed with short oligomers and small nanopores. (a) An illustration of the sequential processes of nanopore translocation. First a molecule diffuses near the pore, where it is captured by the electric field. The molecule is trapped at the mouth of the pore until it finds a conformation which allows one of its ends to thread through the pore. (b) Typical signals observed for 50bp dsDNA fragments. The events have a characteristic shallow level followed by a deeper tail.

Figure 6. Dynamic disorder observed with carbon nanotube transducers.

### Advanced Device Technologies for Defense Systems

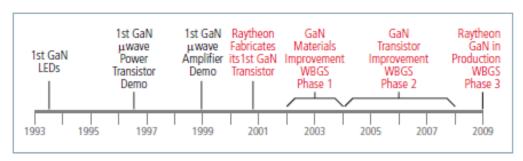

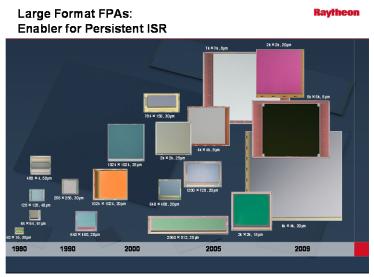

## John C. Zolper Vice President, Research and Development Raytheon Company