# Fabrication and Characterization of a Hierarchical Manifold Microchannel Heat Sink Array for Evaporative Intrachip Cooling

K. P. Drummond, J. A. Weibel, S. V. Garimella, D. Back, D. B. Janes, M. D. Sinanis, and D. Peroulis

#### **OBJECTIVE**

Design, fabricate, and characterize a hierarchical manifold microchannel heat sink to dissipate high heat fluxes at low pressure drops using evaporative cooling.

### **APPROACH**

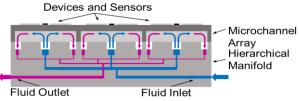

- Deliver HFE-7100 to a 9 × 9 array of silicon microchannel heat sinks via a hierarchical manifold distributor.

- Parallel flow paths allow for shorter flow lengths and decreased pressure drop.

- Scalable design allows for further flow discretization.

## SCHEMATIC DIAGRAM OF HEAT SINK CONCEPT

(ICECool) Fundamentals program.

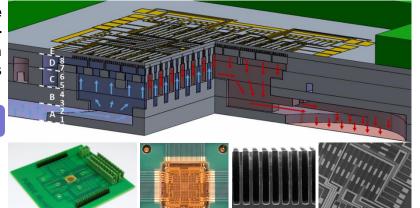

#### TEST VEHICLE, WIRE-BONDED CHIP, CHANNEL CROSS-SECTIONS, AND HEATERS/RTDs

#### RESULTS

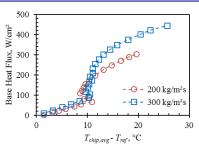

- Dissipated high heat fluxes (~ 450 W/cm²) at reasonable pressure drops (< 75 kPa) and low chip temperature rise (< 30 ° C).</li>

- Low mass flux needed for high performance.

- Increasing fluid mass flux increases maximum heat flux.

- Maximum heat transfer coefficient occurs at intermediate heat flux.

#### **SELECTED PUBLICATIONS**

- K. P. Drummond, J. A. Weibel, S. V. Garimella, D. Back, D. B. Janes, M. D. Sinanis, and D. Peroulis, 40th GOMACTech Conference, 2015.

- K. P. Drummond, J. A. Weibel, S. V. Garimella, D. Back, D. B. Janes, M. D. Sinanis, and D. Peroulis, ITHERM Conference, 2016.

#### **FABRICATION**

- Etch high aspect-ratio microchannels into silicon (DRIE).

- Pattern heaters and an array of RTDs on backside of microchannels to apply heat flux and measure chip temperatures, respectively.

- Fabricate hierarchical manifold to facilitate fluid delivery to microchannel array.

- Bond manifold to microchannels

#### **HEAT FLUX VS. CHIP TEMP**

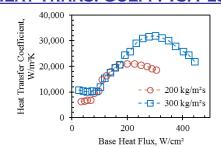

#### **HEAT TRANS. COEFF. VS. FLUX**