# **Seth Journal**

### Week 15

WE DONE (almost)

#### Entry 6

10:15am-7pm 4/25 Friday 8.75 hours

Ok, was unable to solve with Brian last night what caused the pio machine not to work

For the first part of today without Brian, i decided to reimplement in a new RAM module the original code instead of trying to integrate the original bus code with the RAM file. I ran that however it still failed due to borrowing issues. Chatgpt kept using take() and unwrap() to pass the references to the RAM object without dropping them:

```

let mut sm0 = pio1.sm0.take().unwrap();

let mut sm1 = pio0.sm1.take().unwrap();

let mut sm2 = pio0.sm2.take().unwrap();

let mut irq2 = pio0.irq2.take().unwrap();

```

However, the state machines do not allow them to be taken or unwrapped so this did not work.

I then tried another approach that was close to the original implementation where I used closures inside the main loop instead of making a struct cause I anticipated references were getting dropped. That worked.

I then tried calling the closures from inside of a RAM class like this in order to be able to have methods that could be called by the CPU class to do read and write operations on

```

let write: impl FnMut(u32, u8) -> impl Future<Output... = async |address: u32, data: u8| {

// set address to output and data to output pindirs

sm2.tx().wait_push(0xFFFFFFF).await;

info!("Initiating write of 0x{:02X} to address 0x{:08X}", data, address);

let value: u32 = (address << 8) | (data as u32); //| if en {0x800000000} else {0x0000000000};

sm2.tx().wait_push(value as u32).await;

irq2.wait().await;

// set address to output and data to input pindirs

sm2.tx().wait_push(0xFFFF00).await;

info!("Write complete to address 0x{:08X}", address);

};

can't capture dynamic environment in a fn item

use the `|| { ... }` closure form instead rustc(click for full compiler diagnostic)

struct R

defmt_macros

proc_macro write

fn w View Problem (Alt+F8) Quick Fix...(Ctrl+.) Fix using Copilot (Ctrl+!)

write()

}</pre>

```

As you can see though, I get an error that the dynamic environment can't be captured. So I don't think closures are the answer.

I then tried looking up other ways embassy can handle dynamically changing peripherals in other parts (functions) of the code.

I saw that <u>embassy-executor</u> provided functions for notating the main and task functions. I could store things in task functions, however that wouldn't really help as task functions are supposed to be run 24/7 and not listen exactly for requests.

I also found Mutexes, Channels, and interrupts. I found this in the <a href="mailto:embassy book">embassy book</a>. I gave had chatgpt the examples and my code and had it try rewriting my code to use them to pass messages between the main thread and other running tasks that would handle reading and writing. It tried, however, it kept running into using .take() and unwrap() and didn't fully know how to use mutexes, so I didn't bother.

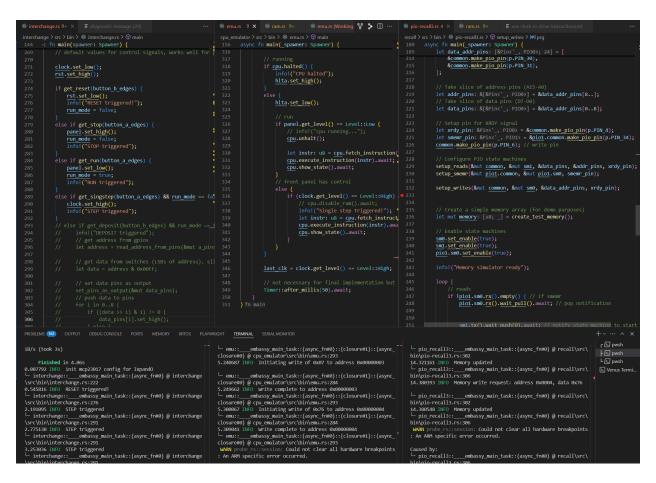

Brian then came around this time and I asked him to look into the problem because he is more experienced with Rust borrowing than I am. Over the next 2 hours and while we did our first demo he figured out how to use closuers and keep them alive using the nightly Rust development channel so that we could have the reads and writes work. That approach worked.

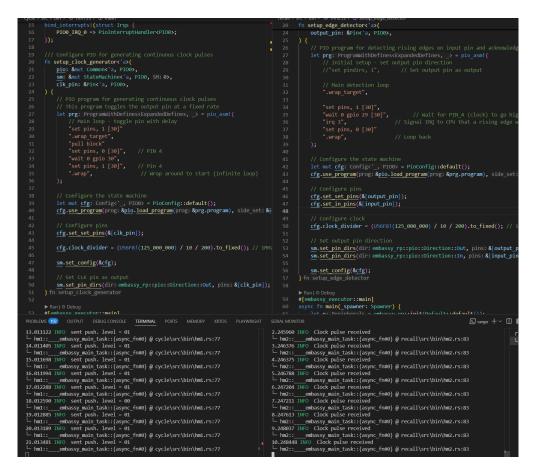

We reconfigured all the old code to make the initialization of the RAM in the main function and then passed the closuer-enclosed read and write functions to the CPU struct to be able to be called. we programmed the memory card with our original memory reading code and cpu card with the new RAM-using transaction code. This worked! We saw the correct instructions written to memory during the mem\_init() phase and then the CPU using its program counter to do reads from memory, pull the correct instructions, and execute them!

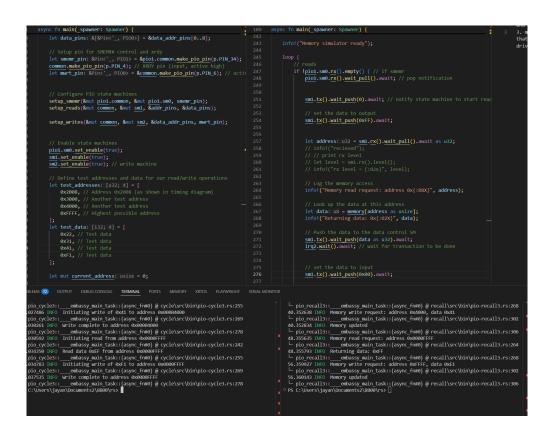

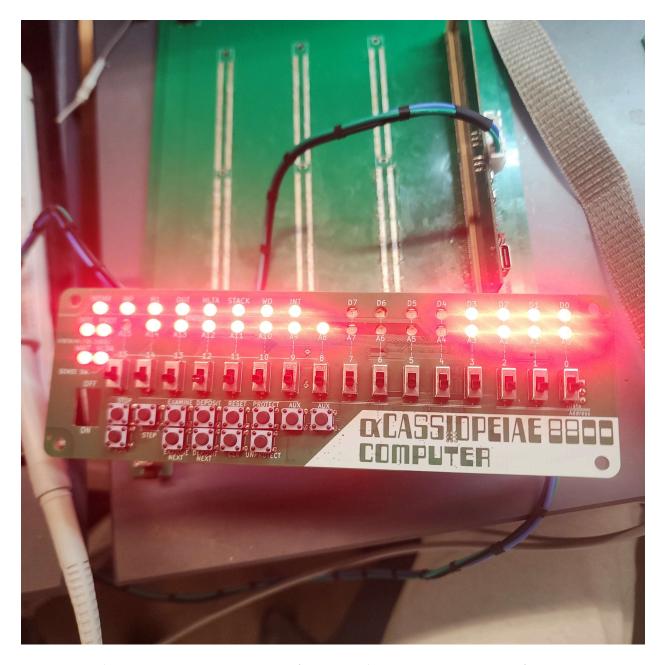

While this was done/after our demo Caleb who was working on the front panel and got the single step/run working ish had to leave, so I took over from him on this. We needed to get signle step and stuff working before our chance at a second demo so I needed to fix his code.

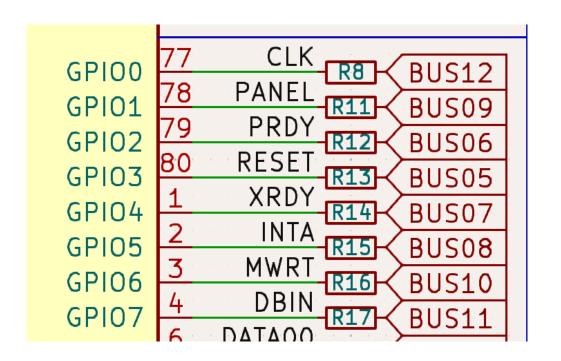

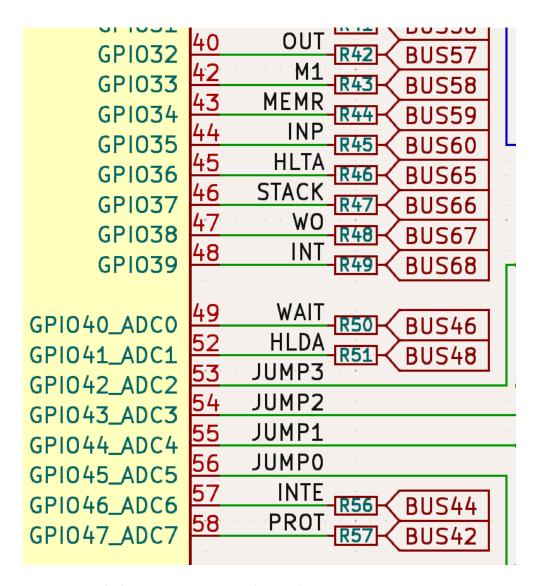

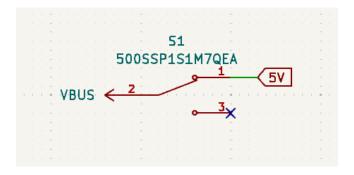

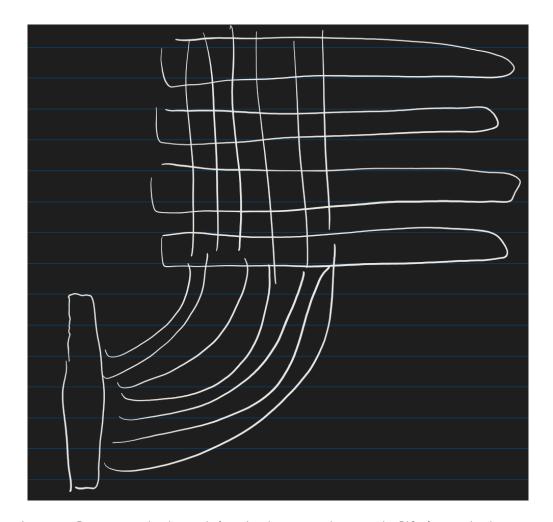

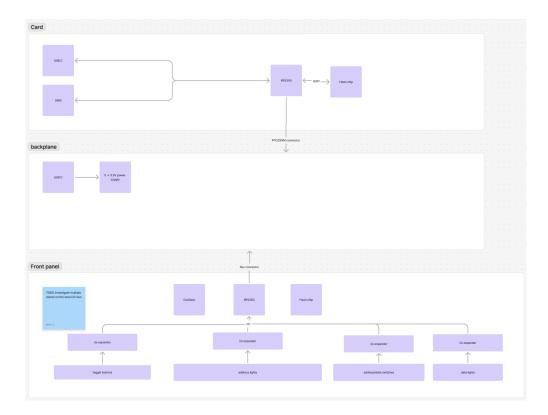

I decided to change around the signals a bit and how they were used. I discarded PRDY and just used CLK, PRESET, and PANEL to control RUN, STOP, RESET, and single step. If the STOP button was pressed on the front panel, PANEL would be set high and the front panel would be in control of the data bus and the computer would be in stop mode. You could use the SINGLE STEP button to step through the program. This would trigger a positive edge on the CLK line every time it was pressed and the CPU would watch for it to advance an instruction. If RUN was pressed, PANEL would be set low, and the CPU would know to resume running its normal execution loop on its own. If RESET is

pressed on the front panel, this would tell the CPU to stop execution and reset its program counter, nomatter whether it's in run or stop mode. This operating logic was written out on the front panel and interchange side like this:

I tested this and the operations worked! I was likewise able to see in the terminal below when each buttons were pressed on the front card side and then the operation occurring on the CPU side.

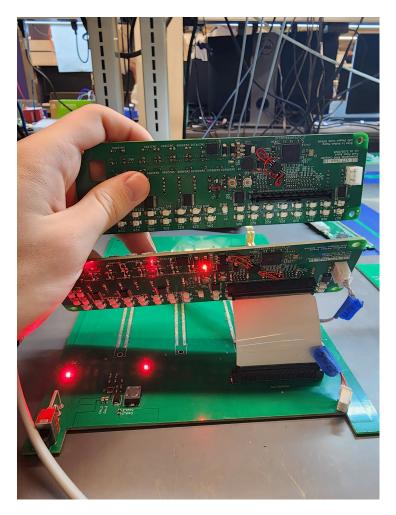

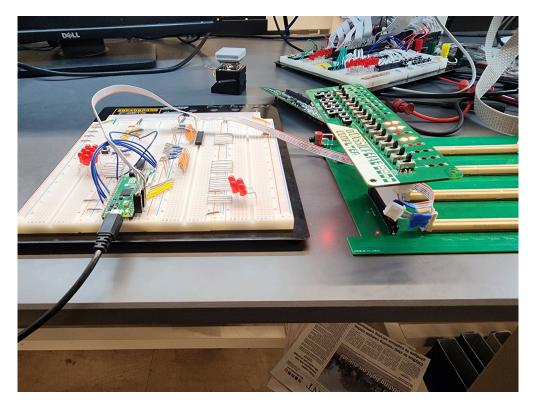

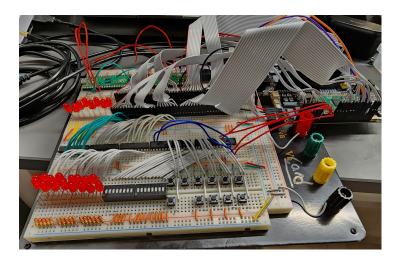

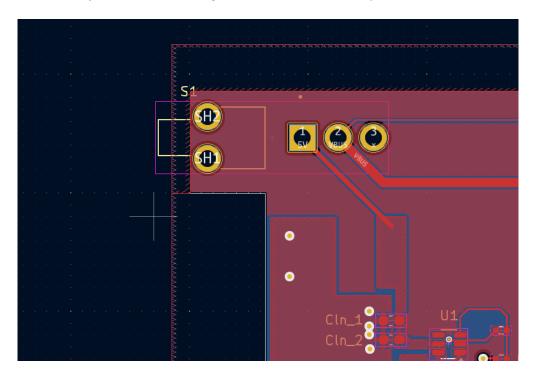

Finally once brian finished his part, we integrated the RAM as well We pulled up the code and terminals for all 3 programs to be able to program and see their outputs a the same time:

We then tested it, saw the memory get programmed the computer go into stop mode, and then we were able to hit single step, run, stop, and reset to work through the program and memory reads and writes worked to the memory computer! This was our functioning computer!

We still had time before our demo so I got to work creating the deposit function while Brian fixed some of the LEDs on the front panel. The deposit function would let you enter in the switches on the front panel a data value you want to write to your current location in memory. It is one of the other front panel functions along with examine and protect that we had not implemented yet.

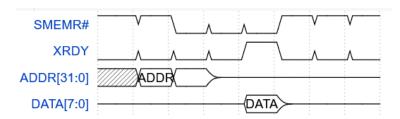

With deposit I needed draft out what signals would trigger on the bus and what data inputs to use to implement it. I came up with this draft plan:

get addr from bus

get data from switches

output data on bus

mwr bring low

assert panel

cpu should release ouptut pins

wait for xrdy to go high

deassert mwr and output data

So the front panel needed to take over the mem write signal from the cpu. Since both can't be driven at the same time, I decided that the CPU would release control of the mem write line when it was in stop mode (PANEL high), but not single-stepping. However, the mem write line is a active-low line so it always needs to be driven high when not used. I couldn't just release control and have a gap when it's not high, so I set the mwrt pin to pull up on the cpu side with

```

Flex::new(p.PIN_6.reborrow()).set_pull(Pull::Up); // set mwrt as pull up

```

I then needed a way to release and regain output of the mwrt pin on the CPU side from inside the main loop. I tried adding

```

sm.set_pin_dirs(embassy_rp::pio::Direction::In, &[mwrt_pin]);

```

which suggestively would have told the state machine running the mwrt pin to stop it from outputting. However, this line faced a borrowing issue where you can't borrow sm a second time in the main loop. I needed to fix this or find another method. I decided another method. Brian helped me find that OUT\_EN\_SEL adn INLINE\_OUT\_EN PIO configuration registers

| 23:19 | OUT_EN_SEL: Which data bit to use for inline OUT enable                                                                                                                                                                                                                                                   |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18    | INLINE_OUT_EN: If 1, use a bit of OUT data as an auxiliary write enable When used in conjunction with OUT_STICKY, writes with an enable of 0 will deassert the latest pin write. This can create useful masking/override behaviour due to the priority ordering of state machine pin writes (SM0 < SM1 <) |

| 17    | OUT_STICKY: Continuously assert the most recent OUT/SET to the pins                                                                                                                                                                                                                                       |

These would allow us to control the output of the mwrt pin wich was made a set pin and couldn't be controlled by pindirs like normal. It was also simpler than making a second state machine for the mwrt signal.

We changed the state machine to use these:

```

cfg.out_en_sel = 0x1F;

cfg.inline_out_en = true;

cfg.out_sticky = true;

```

And then added a disable function in our front panel control to set a bit in the output to trigger the mwrt signal to turn off

```

else {

if (clock.get_level() == Level::High) && (last_clk == false) {

cpu.disable_ram().await;

info!("Single step Triggered!");

let instr: u8 = cpu.fetch_instruction().await;

cpu.execute_instruction(instr).await;

cpu.show_state().await;

}

}

```

Next I needed to write the logic for gaining control and using the mwrt signal on the front panel side along with the other data inputs and bus control logic. Based on the psuedologic I wrote above, I came up with this code implementation:

```

else if get_deposit(button_b_edges) && run_mode == false {

info!("DEPOSIT triggered");

// get address from gpios

let address = read_address_from_pins(&mut a_pins);

// get data from switches (LSBs of address). slice address

let data = address & 0x00FF;

// set data pins as output

set_pins_as_output(&mut data_pins);

// push data to pins

for i in 0..8 {

if ((data >> i) & 1) != 0 {

data_pins[i].set_high();

} else {

data_pins[i].set_low();

}

mwrt.set_as_output();

mwrt.set_low();

xrdy.wait_for_high().await; // wait for ready

mwrt.set_high(); // turn off write

mwrt.set_as_input(); // set back to input

// turn off data pins

set_pins_as_input(&mut data_pins);

Timer::after_millis(10).await;

```

I then programmed the front panel and cpu micros with the new code.

We tested the deposit button on a memor location with the switches all down. It wrote a zero, however, we were unable to step afterwards so something was either a bit broken with the logic or the bus lines like mwrt. Our final demo time came, so we excluded this functionality.

For our final demo, we realized the memory writes when the machine powered up on init were not all being written cause the memory card takes awhile to boot. Even after adding a delay in the cpu to get it to write to memory later the first instructions, this didn't help. So part of our powering on sequence is taking out and reinserting the cpu card while the computer is powered so that the init instructions are correctly written. We will need to fix this later. Otherwise, our demo showing us running, stepping though, stopping, and reseting the machine's porgram with the buttons and then the address and data leds showing the operations on the front panel worked!

Next steps for spark challege would be to fix that error, implement deposit, examine and protect, and have a test program ready to show the full functionality of our cpu emulator. Also we need to finish the PCBs or our other 3 computers and make sure those work too.

Thank you!

## Entry 5

10pm-3 am

4/24 Thurs

5 hours

I come back from dinner and brian has the debug cables done. i hook up the front panel to our backplane with 2 cards in and monitor if the bus reads and writes address and data are showing up correctly on the LEDs. They are

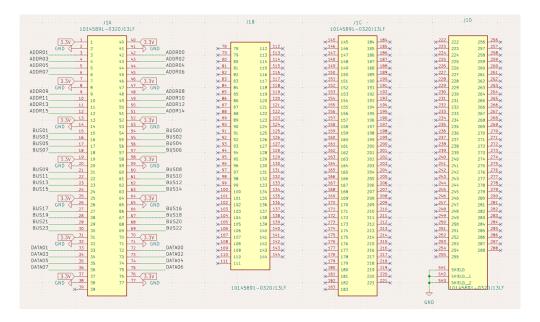

then i combine the bus tables together

| Function | Туре      | Front (12) | Description                        | Ownershi<br>p         | Panel<br>GPIO | Card<br>GPIO |  |

|----------|-----------|------------|------------------------------------|-----------------------|---------------|--------------|--|

| CLK      | Control   |            | Bus clock                          | Panel                 | 24            | 0            |  |

| ~PRESET  | Control   |            | Reset                              | Panel                 | 29            | 3            |  |

| PANEL    | UI        |            | Front panel data control           | Panel                 | 27            | 1            |  |

| PROT     | UI        | Front      | Memory protection                  | Panel                 | 15            | 47           |  |

| M1       | Status    | Front      | First machine cycle of instruction |                       |               |              |  |

| HLTA     | Status    | Front      | Halt                               | CPU                   | 0             | 36           |  |

| STACK    | Status    | Front      | Stack operation                    | CPU                   | 1             | 37           |  |

| ~PHOLD   | DMA       |            | Hold bus control                   |                       |               |              |  |

| DBIN     | R/W       |            | Data bus in                        | CPU                   | 25            | 7            |  |

| WO       | R/W       | Front      | Write-out                          | CPU                   | 2             | 38           |  |

| WAIT     | R/W       | Front      | Memory/IO wait                     | CPU                   | 13            | 40           |  |

| PRDY     | I/O       |            | IO ready                           |                       | 46            | 2            |  |

| OUT      | I/O       | Front      | Output IO cycle                    | CPU                   | 9             | 32           |  |

| INP      | I/O       | Front      | Input IO cycle                     | CPU                   | 5             | 35           |  |

| XRDY     | Memory    |            | Memory ready                       | RAM                   | 47            | 4            |  |

| MWRT     | Memory    |            | Memory write strobe                | CPU,<br>Panel         | 26            | 6            |  |

| MEMR     | Memory    | Front      | Memory read strobe                 | CPU,<br>Panel         | 6             | 34           |  |

| INT      | Interrupt | Front      | Interrupt request                  |                       | 44            | 39           |  |

| INTA     | Interrupt |            | Interrupt acknowledge              | CPU                   | 28            | 5            |  |

| INTE     | Interrupt | Front      | Interrupt enable                   | CPU                   | 14            | 46           |  |

| HLDA     | Status    | Front      | Hold acknowledge                   |                       | 11            | 41           |  |

| M1       | Status    |            | First machine cycle                |                       | 8             | 33           |  |

| A0       | Address   |            | Address line                       |                       | 31            | 16           |  |

| A1       | Address   |            | Address line                       |                       | 41            | 17           |  |

| A2       | Address   |            | Address line                       |                       | 33            | 18           |  |

| A3       | Address   |            | Address line                       |                       | 35            | 19           |  |

| A4       | Address   |            | Address line                       |                       | 16            | 20           |  |

| A5       | Address   |            | Address line                       |                       | 18            | 21           |  |

| A6       | Address   |            | Address line                       |                       | 22            | 22           |  |

| A7       | Address   |            | Address line                       |                       | 20            | 23           |  |

| 8A       | Address   |            | Address line                       |                       | 42            | 24           |  |

| A9       | Address   |            | Address line                       |                       | 43            | 25           |  |

| A10      | Address   |            | Address line                       |                       | 45            | 26           |  |

| A11      | Address   |            | Address line                       |                       | 3             | 27           |  |

| A12      | Address   |            | Address line                       |                       | 12            | 28           |  |

| A13      | Address   |            | Address line                       |                       | 10            | 29           |  |

| A14      | Address   |            | Address line                       |                       | 7             | 30           |  |

| A15      | Address   |            | Address line                       |                       | 4             | 31           |  |

| D0       | Data      |            | Tri-state data                     | CPU,<br>RAM,<br>Panel | 40            | 8            |  |

| D1       | Data      |            | Tri-state data                     | CPU,<br>RAM.          | 30            | 9            |  |

Then i work on figuring out how the front panel will interact with the bus and how start and stop will work. I determine that stop will stop the clock and use the halt signal in some way.

caleb gets back and he takes over implementing the front panel.

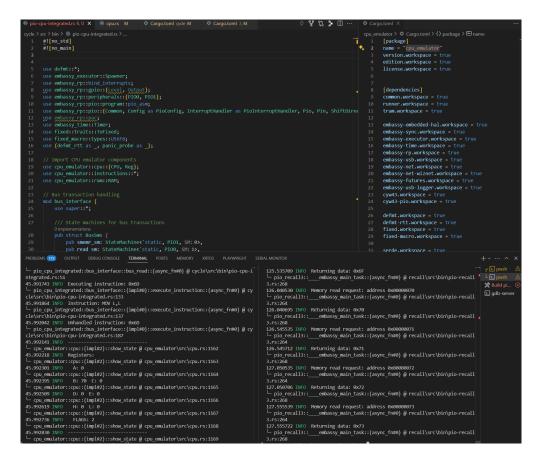

I then switch to integrating the bus read and write from cpu into the cpu emulator, we're not going with making a new file as i did earlier or making 2 separate packages. Instead, the emulator package right now I will just copy the cpu embassy read write code into for reading and writing.

I did this, however, if I want singular read and write functions, I'm going to have to pass in the interaction to the pio state machines and that involves borrowing and lifetimes. I don't know how to do that really yet so I'm waiting for brian to do his bus signal checking program, and then finish fixing the bus

#### Entry 4

2pm - 9 pm 4/25 Thursday

7 hours

ok figured out issue pin 34 not being able to be read as that's part of the read/write sequence.

it's that there's a 16 pin offset and the gpiobase must be selected. so you do pin 18 instaed of 34 and it works.

ok now that I knew it works, i fixed the read code in pio-recall to respond to smemr changes and it worked.

now that that worked i'm going to try integrating writes again. i made a new set of files called pio-cycle3 and pio-recall3 that will be the newest version to test reads and writes running at the same time

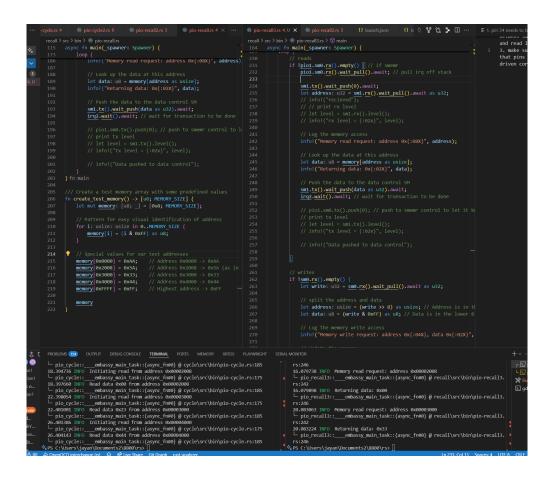

I copied pio-cycle and pio-recall to them and then added changes from pio-recall2 to the memory. I tested with the write state machine operating at the same time and reads worked. shown below

ok i now know how setting pinsdirs works.

got writes to work and read addr is setting good.

now just need to fix data returned on reads.

i'm setting up the oscilloscope to read all the data lines

ok oscilloscope didn't help that much but commenting out the cpu to see that the recall was still driving the lines made it clear recall was the issue

after changing the pindirs for the recall to only turn on when needed, i fixed it.

here are final reads and writes working:

now that it was good i needed to integrate the cpu emulator

i gave the code to claude and the emulator code and toolkit to make a new file that used both it came up with one

ran it first time and here are cpu working alongside memory requests card to card. You'll see however, it's reading and writing the wrong values, so I need to fix this as a next step.

### Entry 3

11:30pm-2 am

Tuesday 4/22

2.5 hours

$\ensuremath{\mathsf{ok}}$  so now need to fix the outputs happening at the same time. either

- 1. Disable the state machine (likely not possible for the ram

- 2. turn off outputs using pindirs or turning off state machine. maybe sticky?

Okay thought of doing a different state machine block. that worked! i just needed to debug a lot changing individual things. realized pindirs matters.

then i got it to show up on oslocope.

then i programmed the mem card. the mem card was spamming returns.

the i switched to helping caleb setup dev board board as a deug probe and the other as a micro

he programmed his cpu code on it successfully. so now we can show that a cpu works

we tried the code but all the pins were showing zero

then I remembered that the pull up resistors exist. we needed to turn them on in order for the signals to be read.

ok the reason the original bus reads wrked even when each pio block can only read from 32 pins is that the pin it was writing and reading from "34" was the same, just not actually 34.

they really can only read from 32 pins at once

i'm stuck

a square wave on pin 34 is not being picked up.

#### Entry 2

3:45pm-5pm

Tuesday 4/22

1.25 hours

Okay need to fix writes

Tested reads but they didn't work

looks like i forgot to initialize the pin as a pio pin on the cpu card

tied the oscilloscope up to the breakout pins brian made and it worked

now needed to get writes and reads working at the same time

tested reads individually and those worked, tested writes individually and those worked, but together they didn't.

ok i actually found the problem. on the ram side, if

setup\_mem\_write\_control(&mut common, &mut sm1, &data\_addr\_pins, xrdy\_pin);

is enabled, then the cpu doesn't get the correct data returned to it on reads, but when it's disabled, it does. why is this so?

Chatgpt response:

This happens because **both state machines (sm0 and sm1) on the RAM side are configured to control the same pins** (the data pins and address pins), but with different directions and purposes:

• sm0 (read SM) sets the data pins as outputs (to drive data to the CPU during a read).

• sm1 (write SM) sets the data pins as inputs (to receive data from the CPU during a write).

#### When both are enabled at the same time:

- According to the RP2040 PIO docs, for each pin, the highest-numbered enabled state machine (here, sm1) controls the output level and direction.

- So, even during a read, sm1 is setting the data pins as inputs, overriding sm0's attempt to drive them as outputs.

- As a result, the RAM cannot drive the data bus during a read, and the CPU sees zeros

or floating values.

#### Entry 1

7:15pm-3am

4/21 Mon

7.75 hours

Ok pio time.

going to rerun hi to show brian the not detecting high pin problem. then we'll look at the gpio registers

Ok i thought that you would need to set a pin you're using in a wait statement as a "input" pin and an "in" pin however I think you just need to select it for pio usage using &common.make\_pio\_pin(p.PIN\_30)

ok my bus reads weren't working and things were getting stuck

but i realized my feed in and out direction waswrong so i fixed those

#### So it works!

Next i changed the pins to the actual ones that will be used by the bus so we can see the correct address and data pins lighting up.

When I compiled and ran it, the cycle half didn't work cause smemr is pin 34 which is outside of 0-31 so it can't set gpiobase at the same time. this didn't happen with the ram side since the control pin that ram need to drive (xrdy) is pin 4 and that is within the range.

I just used chatgpt to split up the state machine into 2 with 1 just dedicated to driving smemr and it worked.

## Week 14

OK FINALLY THE FINAL PUSH

## Entry 5

9:45-10:15

Weds 4/16

9.5 hours

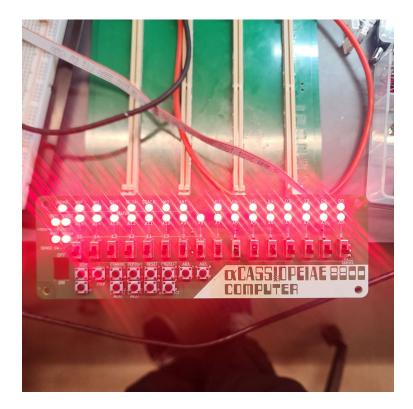

Brian had completed a new front panel in the afternoon and i needed to test if it worked i programmed it with a ligtup all progrma to lightup all the leds none of the leds lit up

i then tried reprogramming the original back panel just to make sure the program works that i flashed. it worked i then plugged in the new one again and reflashed but it still did not work

i noticed that some of the flash chip reworked connections brian made on the original front panel were not present on the new one. you can see below where the new one is the bottom one.

I think some of the connections have to deal with sending data over. I ran

probe-rs verify target\thumbv8m.main-none-eabihf\debug\lightup

Verification failed

The verification failed because it can't actually read from the flash chip. it thinks it wrote but the read/write lines are not fully connected. Brian will need to come in and add these.

okay so i don't have a good final pcb to work with so going to switch back to working with the dev board I need to figure out why waiting is not working.

ok brian came inand we fixed swd

had issues programming

one pico doesn't work

then fixed buttons

and all leds on new front panel

still cannot get new bus to work but trying things like only setting one pin

now going to do watchdog to full reset controller. added that to vscode debug, we can always use reset button to full reset

we then ran interchange which was reading from i2c to see if the buttons now work! they do. just needed to fix one button.

```

46.446450 INFO data = 00 00 ff 1f

interchange::___embassy_main_task::{async_fn#0} @ interchange\src\bin\interchange.rs:161

46.500069 INFO data = 00 00 ff 9f

interchange::___embassy_main_task::{async_fn#0} @ interchange\src\bin\interchange.rs:161

46.553667 INFO data = 00 00 ff 9f

interchange::___embassy_main_task::{async_fn#0} @ interchange\src\bin\interchange.rs:161

46.607296 INFO data = 00 00 ff bf

interchange::___embassy_main_task::{async_fn#0} @ interchange\src\bin\interchange.rs:161

46.660916 INFO data = 00 00 ff bf

```

Ok next we wanted to get the card working so we could program the card and front panel at the same time and use them for bus transfer writing. we needed another swd cable for the card to be able to program them both at once so brian made one

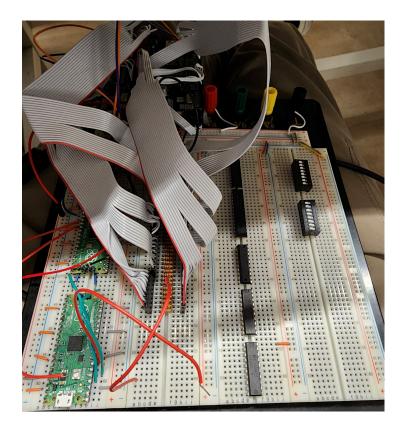

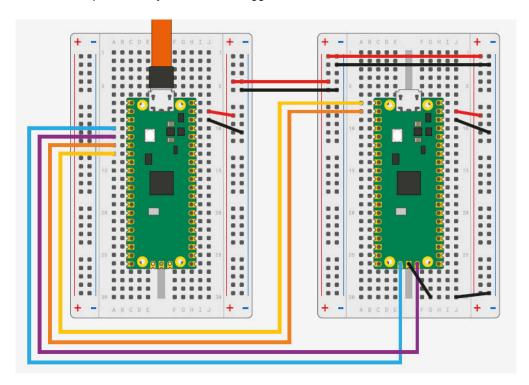

I then used the picos on the board as debug probes since the other pico didn't work and wired them up to the card and front panel. it looks like this (green and blue silicone wires):

We then programmed the card. it flashed but the program wasn't runing, there wern't any outputs to console. Brian and i setup openocd debugging and noticed it was hard faulting somewhere. We didn't see anything wrong with the code cause it worked on another board, so we realized it was a hardware problem, brian noticed the chip select was not soldered wellk, fixed that, brought it back, and the program ran as intended, we just set all the pins to high from the card and this should trigger all the leds on the front panel as they are tied to the bus too, we noticed that they did not all turn on:

Because they did not all turn on that means not all of the connections were good between the front panel and card. so brian went to inspect and fix these.

Brian fixed all of them but A11 and HLDA. Then those were fixed and everything lit up.

Then we needed to verify all the control lines that were not the leds had connections between the card and front panel. i setup a front panel program to set all the gpios to inputs except the i2c lines and had it printed all the ones that were high, they were all high!

```

1.633343 INFO led at index 17 is low

└ inputs::_

_embassy_main_task::{async_fn#0} @ interchange\src\bin\inputs.rs:105

1.633450 INFO led at index 18 is low

inputs::___embassy_main_task::{async_fn#0} @ interchange\src\bin\inputs.rs:105

1.633553 INFO led at index 19 is low

inputs::___embassy_main_task::{async_fn#0} @ interchange\src\bin\inputs.rs:105

1.633659 INFO led at index 20 is low

- inputs::____embassy_main_task::{async_fn#0} @ interchange\src\bin\inputs.rs:105

1.633766 INFO led at index 21 is low

_embassy_main_task::{async_fn#0} @ interchange\src\bin\inputs.rs:105

- inputs::

1.633870 INFO led at index 22 is low

└ inputs::___embassy_main_task::{async_fn#0} @ interchange\src\bin\inputs.rs:105

1.633974 INFO led at index 23 is low

inputs::___embassy_main_task::{async_fn#0} @ interchange\src\bin\inputs.rs:105

1.634083 INFO led at index 24 is low

└ inputs::___embassy_main_task::{async_fn#0} @ interchange\src\bin\inputs.rs:105

1.634188 INFO led at index 25 is low

- inputs::___embassy_main_task::{async_fn#0} @ interchange\src\bin\inputs.rs:105

1.634293 INFO led at index 26 is low

embassy_main_task::{async_fn#0} @ interchange\src\bin\inputs.rs:105

- inputs::_

1.634400 INFO led at index 27 is low

inputs::___embassy_main_task::{async_fn#0} @ interchange\src\bin\inputs.rs:105

1.634504 INFO led at index 28 is low

inputs::___embassy_main_task::{async_fn#0} @ interchange\src\bin\inputs.rs:105

1.634614 INFO led at index 29 is low

└ inputs::___embassy_main_task::{async_fn#0} @ interchange\src\bin\inputs.rs:105

1.634720 INFO led at index 30 is low

— inputs::____embassy_main_task::{async_fn#0} @ interchange\src\bin\inputs.rs:105

1.634822 INFO led at index 31 is low

- inputs::_

_embassy_main_task::{async_fn#0} @ interchange\src\bin\inputs.rs:105

1.634931 INFO led at index 32 is low

inputs::____embassy_main_task::{async_fn#0} @ interchange\src\bin\inputs.rs:105

1.635036 INFO led at index 33 is low

inputs::___embassy_main_task::{async_fn#0} @ interchange\src\bin\inputs.rs:105

1.635141 INFO led at index 34 is low

└ inputs:: embassy main task::{async fn#0} @ interchange\src\bin\inputs.rs:105

1.635245 INFO led at index 35 is low

inputs::___embassy_main_task::{async_fn#0} @ interchange\src\bin\inputs.rs:105

1.635351 INFO led at index 36 is low

inputs::

_embassy_main_task::{async_fn#0} @ interchange\src\bin\inputs.rs:105

1.635458 INFO led at index 37 is low

_embassy_main_task::{async_fn#0} @ interchange\src\bin\inputs.rs:105

inputs::

1.635568 INFO led at index 38 is low

```

do now we have verified our backplane, front plane, and card connections are all good!

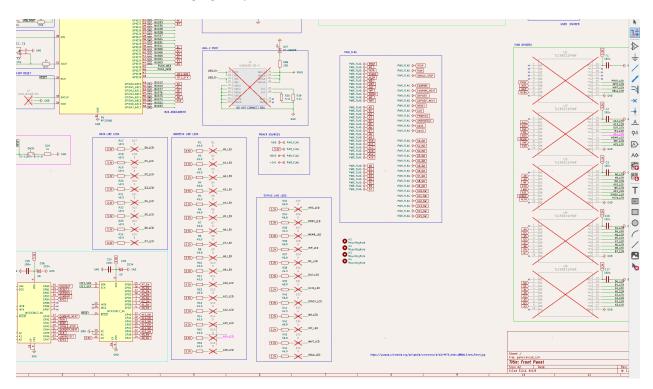

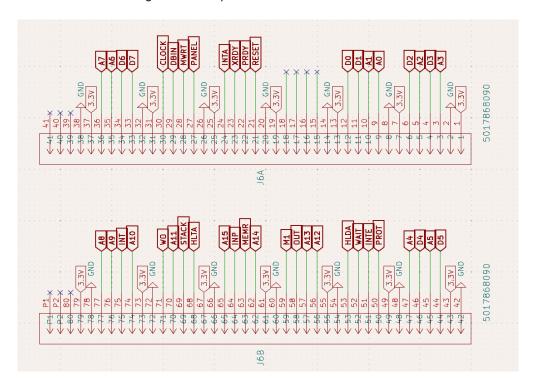

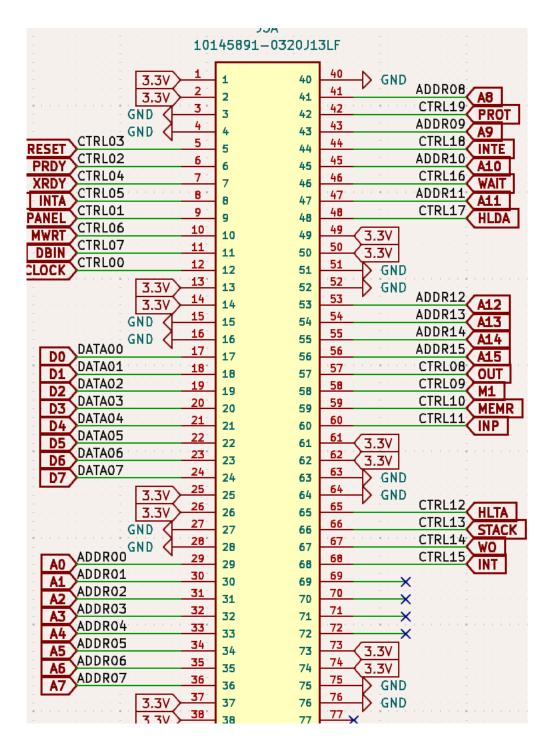

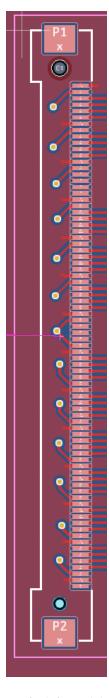

Ok now i can get started on actually programming with our real pcbs! I needed the bus signal notations for each gpio pin on the card. I checked the kicad schematic however the control signal lines were not notated. I fixed these

I now can use the MEMR to indicate to the memory that i would like to read.

I need to also know the mappings for the data and addr lines between the card and front panel, so i created a mapping table of those and the rest of the control signals:

| Function | Panel<br>GPIO | Card<br>GPIO |  |

|----------|---------------|--------------|--|

| Α0       | 31            | 16           |  |

| A1       | 41            | 17           |  |

| A2       | 33            | 18           |  |

| A3       | 35            | 19           |  |

| A4       | 16            | 20           |  |

| A5       | 18            | 21           |  |

| A6       | 22            | 22           |  |

| A7       | 20            | 23           |  |

| A8       | 42            | 24           |  |

| A9       | 43            | 25           |  |

| A10      | 45            | 26           |  |

| A11      | 3             | 27           |  |

| A12      | 12            | 28           |  |

| A13      | 10            | 29           |  |

| A14      | 7             | 30           |  |

| A15      | 4             | 31           |  |

| D0       | 40            | 8            |  |

| D1       | 30            | 9            |  |

| D2       | 32            | 10           |  |

| D3       | 34            | 11           |  |

| D4       | 17            | 12           |  |

| D5       | 19            | 13           |  |

| D6       | 21            | 14           |  |

| D7       | 23            | 15           |  |

| HLDA     | 11            | 41           |  |

| STACK    | 1             | 37           |  |

| INTE     | 14            | 46           |  |

| PROT     | 15            | 47           |  |

| WAIT     | 13            | 40           |  |

| INT      | 44            | 39           |  |

| HLTA     | 0             | 36           |  |

| WO       | 2             | 38           |  |

| OUT      | 9             | 32           |  |

| M1       | 8             | 33           |  |

| MEMR     | 6             | 34           |  |

| INP      | 5             | 35           |  |

| CLK      |               | 0            |  |

| PANEL    |               | 1            |  |

| PRDY     |               | 2            |  |

| RESET    |               | 3            |  |

| XRDY     |               | 4            |  |

| INTA     |               | 5            |  |

| MWRT     |               | 6            |  |

| DBIN     |               | 7            |  |

| 20.11    |               | ,            |  |

Next steps are to change the dev board code to work on the real pcbs with the right gpio ports and get the final read and write transaction code working.

#### Entry 4

10am-11am

Wednesday 4/16

1 hour

I started with hm.rs to try to build up to a final protocol from simple to complicated

I learned that the push was working but the tx was getting full and the transactions didn't work

I also learned that even though gpio 5 is high, the wait condition was not continuing. Need to investigate the wait command more.

#### Entry 3

10pm-4am

Tuesday 4/15

6 hours

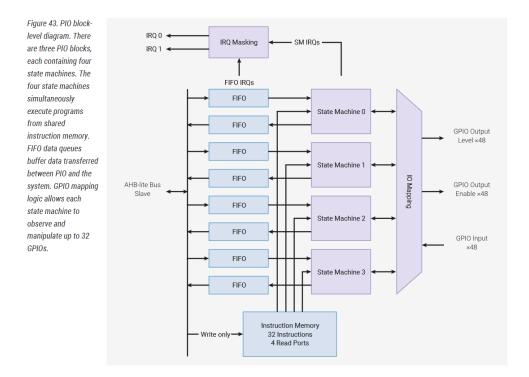

Okay reread about pio. Know all the push and pulls now. I learned that irqs or just paying attention to the rx/tx fifo buffer is how you ccan detect signals or new data from PIO state machines

Ok now testing written code by claude

Looks like recall is always detecting a read but cycle is not receiving a response

I made a simple pio program just turning a pin on and off to make sure the control signal pins were working. that worked when i saw the signal on the oscilloscope.

Now i looked through the program again and made chagnes where i just constantly asserted smemr and dbin high and low to make sure they were outputting correctly, they were.

Ok through trial and error and using copilot to compare the 2 files, i learned that you need to call set\_set\_pins instead of set\_out\_pins cause i was using set instead of out to push to the pins. you also HAVE to have "set pindirs, 1", .

Ok i figured out it just can't register a 1 likely cause there are resistors between the bus lines. That's annoying cause that means we can only pull low for an acknowledgement. Will implement that

#### Entry 2

2:00pm-4pm

Tuesday 4/15

2 hours

Okay need to figure out why all the address lines are not being driven over the pus from the card.

Triggered all GPIO pins but they didn't all light up.

Checked to make sure front panel worked with all pins again in case the gpio pins were damaged or something and they were fine.

Also check an output signal was being sent from the card to the backplane and they were for the LEDs that were missing

Now going to check the connections.

### **Entry 1**

Tuesday 4/15

2am-4am

2 hours

Okay right now I'm moving changes from the new-toolchain branch to the main branch so we can get debugging on it later if we want. Ok that took awhile but brian cleaned up all the packages and added docs and stuff so it works nice. The debugging may be useful.

After everything was merged, there were some rust analyzer complaints, so i just fixed those.

Okay next step is to get the switches to actually light up their individual LEDs above them instead of just arbitrary ones that were next to each other.

### Week 13

This week was spent debugging why our PIO was not working and testing our code for interchange on the final PCB for the front panel with Brian.

#### Entry 4

Friday night

3 hours

10pm-1am

During the time I was away Brian setup VSCode debugging via GDB and OpenOCD so that we could figure out root case by tracing through to verify that GPIOBASE was actually set.

He did this by using the <u>AArch32 bare-metal target Toolchain</u> instead of the one that comes with Rust that probers/openocd uses. This gave us the debugging notation for the ELF file and that we needed in order for debugging to work.

Here is a screenshot of the VSCode debugging working from Brian's computer:

```

08a80187403f815 > 3a85ec ∰ 3 |b ? ‡ † 3 □ ∨ rs > {} impl StateMachine < d, PlO, SM> > 🗇 set_con 713 impl < 'd, PlO: Instance + d, const SM: usize> StateMachine < 'd, PlO, SM> {

VARIARIES

impl<'d, PIO: Insta

pl<'d, PIO: Instance + d, const SM: usize> StateMachine<'d

pub fn set_config(&mut self, config: &Config<'d, PIO>) {

let mut low ok: bool = true;

let mut high_ok: bool = true;

let in_pins: Range<u8> = config.pins.in_base..config.pins.in_base +

let side_pins: Range<u8> = config.pins.sideset_base..config.pins.side

let set_pins: Range<u8> = config.pins.set_base..config.pins.set_base

let out_pins: Range<u8> = config.pins.out_base..config.pins.out_base

for pin_range: Range<u8> in [in_pins, side_pins, set_pins, out_pins]

for pin: u8 in pin_range {

low_ok &= pin < 32;</pre>

high_ok &= pin >= 16;

high ok = true

if !low_ok && !high_ok {

> sm = {...}

panic!(

"All pins must either be <32 or >=16, in:{:?}-{:?}, side:{:?}

> self = 0x200004d0 <interchange

config.pins.in_base,

config.pins.in_base + config.in_count - 1,

config.pins.sideset_base,

> config = 0x2007f70c

Global

Static: ../../..cargo/git/checkouts/embassy-c08a80187403f815/

config.pins.sideset_base + config.pins.sideset_count - 1,

config.pins.set_base,

config.pins.set_base + config.pins.set_count - 1,

config.pins.out base,

config.pins.out_base + config.pins.out_count - 1,

WATCH

let shift: u8 = if low_ok { 0 } else { 16 };

sm.pinctrl().write(|w: &mut SmPinctrl| {

w.set_sideset_count(val: config.pins.sideset_count);

D 812

w.set_set_count(val: config.pins.set_count);

w.set_out_count(val: config.pins.out_count);

w.set_in_base(val: config.pins.in_base.checked_sub(shift).unwrap_

w.set_sideset_base(val: config.pins.sideset_base.checked_sub(shift

CALL STACK

w.set_set_base(val: config.pins.set_base.checked_sub(shift).unwra

rp2350.dap.core0 (Name: rp2350.dap... PAUSED ON STEP

w.set_out_base(val: config.pins.out_base.checked_sub(shift).unwr

embassy_rp::pio::StateMachine<embassy_rp::per

PIO::PIO.gpiobase().write(|w: &mut Gpiobase| w.set gpiobase(val: shift

embassy executor::raw::{impl#9}::poll::{closu

if let Some(origin: u8) = config.origin {

unsafe { self.exec_jmp(to_addr: origin) }

✓ interchange.rs interchange\src\bin

pub fn get_addr(&self) -> u8 {

let addr: Reg<SmAddr, RW> = Self::this_sm().addr();

91

```

We did this and noticed that GIPOBASE was getting set for the higher pins, unlike what we originally found. This was some erratic behavior. There was no issue it turned out in any of our packages.

We weren't sure what was the issue. I then tried to program our prototype front panel PCB with our PIO program instead of the dev boards since those seemed to be unreliable.

The program then worked for the upper pins and the LEDs lit up on the front panel!

Now that we knew the LED outputs over we then needed to verify that the I2C + IO Expanders also worked on the prototype PCBs. We need to change the pins that the microcontroller knew the IO expanders were on since they were different than our dev boards.

We then used our original program which read from I2C and then output that data on the FIFO for the state machine the PIO program was running from. This would demonstrate that flipping switches would then correspond to changed LEDs on the front panel.

```

loop {

let mut addr0: [u8; 1] = [0];

let mut addr1: [u8; 1] = [0];

let mut data: [u8; 1] = [0];

let mut tmp: [u8; 1] = [0];

// Read from port B, top IC (data)

i2c.write_read(address: ADDR1, write: &[GPIOA], read: &mut data).await.unwrap();

// // Read from port B, top IC (lower addr)

i2c.write_read(address: ADDR1, write: &[GPIOB], read: &mut addr0).await.unwrap();

// // Read from port A, bottom IC (top addr)

i2c.write_read(address: ADDR, write: &[GPIOA], read: &mut addr1).await.unwrap();

i2c.write_read(address: ADDR, write: &[GPIOB], read: &mut tmp).await.unwrap();

info!("data = {:02x} {:02x} {:02x} {:02x}", data[0], addr0[0], addr1[0], tmp[0]);

// Send the data to the PIO FIFO - this will be output to pins 40-47

sm0.tx().wait_push(data[0] as u32).await;

// Optional: Add delay between updates

Timer::after_millis(50).await;

}

```

#### And it did!

As you can see on the front panel bellow, 2 of the 8 switches farthest from the front of the image are flipped down while the rest are up. And likewise 6 of the 8 expected LEDs are lit up. When we flipped the other switches we saw that their corresponding LEDs switched as well. This is the expected behavior!

We then tested if the buttons worked as well.

We noticed that they actually did not work. When we pressed a button, no output on our terminal changed that indicated the signals coming from I2C.

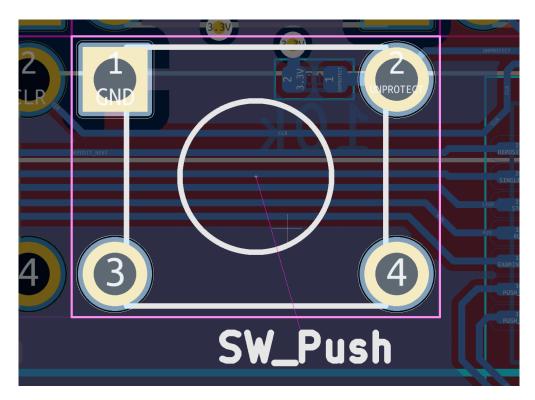

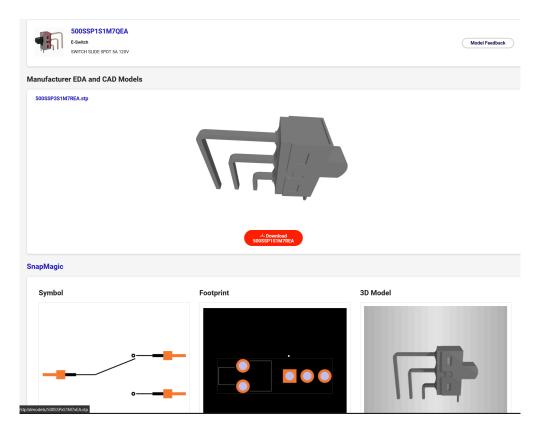

When we looked at the datasheet for the button, we actually noticed that the notation in kicad for what was one side of the switch was different than the datasheet.

Below you can see that the schematic infers that when the button is pushed, pins 2 and 4 are linked with 1 and 3. But what actually happens is the button is split horizontally and pins 1 and 2 are connect to 3 and 4 when the button is pressed.

This was a annoying sign because it meant that all we were getting outputs that were just tied to ground. We realized we needed to desolder all the buttons and somehow rework them to allow for the button to actually work. We decided to later cut off pin 1 to remove it from being tied to ground.

Next steps are to actually complete the full interchange logic so that the buttons and switches work as function and bus signals are sent to control the CPU and memory from the front panel.

We also need to rework the buttons so that we can actually use them. They will need to be desoldered and legs cut off and then resoldered.

#### Entry 3

4/9 Weds night

6pm-8pm

2 hours

When I came back for tonight, Brian had determined that there was a line in the rp235x-pac Rust crate that was not setting the GPIOBASE correctly.

I needed to apply a patch to our Cargo patch to fix this.

Through a google search I learned there are multiple ways to do this. You can:

- 1. Download the repository of the package, apply the patch, and repoint your Cargo.toml to it instead of downloading it from crates-io.

- 2. Use a crate like cargo-patch.

I decided to go with the first solution since it seemed easier and we needed to apply the patch to all of our packages in our Cargo workspace so i thought this would be easier.

I downloaded the repo and made the change and added

```

[patch.crates-io]

rp235x-pac= { path = "../rp235x-pac" }

```

to the Cargo.tomi in our interchange package since that was the package we were using.

I did this and rebuilt the project. I didn't notice anything from the terminal saying that it applied the patch or anything which concerned me.

When I the programmed the project to the microcontroller with pin 47 as the output for PIO, I did not see it light up or any signal on the oscilloscope.

I was concerned the patch was not being applied. I wanted to verify that the dependency rp235x-pac was actually a dependency since it wasn't a root-level dependency I saw in our Cargo.toml. I asked chatgpt how i could get a printout of the dependency tree with cargo and it said I should run cargo tree. I ran that but still did not see rp235x-pac.

Brian came back at this time and he also seemed to be mistaken that rp235x-pac was causing the problem. We decided we wanted to step through the functions this time using a debugger instead of just searching through the code at what might be the cause for GPIOBASE not being set.

Brian and I tried GDB first, however, when we tried setting a breakpoint at a function name, it was unable to find it. We guessed that embassy or Rust mixed up or did not provide notations for the embassy functions in the ELF file cause of state machines or something so we needed to find another solution.

Brian and I decided that VSCode debugging and fixing the debugger would be the best way forward so Brian got to work at getting the debugging figured out and the VSCode launch file setup and I went home.

#### Entry 2

4/9 Weds morning

10am-12am

2 hours

Today we tried to get the PIO (programmable IO) working to output to the LEDs on the dev board. We need this so that we can drive our parallel bus with PIO instead of bit banging, which is much slower.

I had tried this before on the dev board but was failing when trying to get pin 47 or 46 to trigger. I then tried a lower level pin because I thought maybe that might be the issue as some elements of the microcontroller have different operation for the larger QFN package. Pin 30 worked.

We then tested pin 46 and 47 again to make sure that the this wasn't a one off fluke. The lights on the board barely lit up for pin 30 so we verified with an oscilloscope to see if any signal could be observed. We did not see any.

We then needed to debug why some pins were working but others were not. Brian setup OpenOCD to observe the registers of the microcontroller. I installed telnet on my computer as OpenOCD requires it. We were able to observe that there was no PIO code in the registers where PIO code was supposed to be. But this was the case for both when the program specified pin 30 as the output pin and pins 46 and 47, so we didn't think this was the issue.

Brian and I then searched the datasheet for the RP2350 to see if there were any other configuration registers that controlled PIO related output and found that a GPIOBASE register exists:

#### **PIO: GPIOBASE Register**

Offset: 0x168

Table 1016. GPIOBASE Register

| Bits | Description                                                                                                                                                                       | Туре | Reset |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|

| 31:5 | Reserved.                                                                                                                                                                         | -    | -     |

| 4    | Relocate GPIO 0 (from PIO's point of view) in the system GPIO numbering, to access more than 32 GPIOs from PIO.  Only the values 0 and 16 are supported (only bit 4 is writable). | RW   | 0x0   |

| 3:0  | Reserved.                                                                                                                                                                         | -    | -     |

We then check that this was enabled in memory for the program that drove pins 46 and 47 but did not see this.

We then needed to search through the embassy HAL for the RP2350 to figure out if GPIOBASE was set and where.

Brian got to work on this and I went home. Next steps are to continue to debugging so that we can drive higher level GIPO pins with PIO.

### Entry 1

4/7 Monday night

10-11pm

1 hour

Today I tested that the front panel and cards were able to be programmed with Brian.

We first hooked up the card and front panel to the backplane and connected the card from a Pico acting as a debug probe to the card over SWD.

We did this after Brian last week figured out that the SWD programming was not working because the flash chip was improperly wired. Brian rewired it and we were able to reprogram it again.

We flashed a program that turned on all of the LEDs to the card

Almost all of the LEDs lit up on the front panel. That let us know that the connection between the card and the front panel for all the bus lines was not reliable. Our soldering for either the DIMM slot, or the ribbon cable connector may not be correct.

I then programmed the front panel with the same program and all of the LEDs did lit up this time:

This let us know that all the routings between the microcontroller on the front panel were at least correct.

Next steps are to fix the soldering between the card and the front panel so that the card can drive all the LEDs on the bus properly.

## Week 12

## **Entry 1**

Wednesday

10-11am

1 hour

Today I registered my team for the spark challenge and design expo. I also did a more research on how to output to parallel pins with PIO using the embassy Rust package.

## Week 11

## Entry 3

3/28 Friday

10-12

2 hours

For this time I focused on drafting the code for the rest of the front panel functionality.

I needed to write code to output to the LEDs by writing to the ADDR and Data lines on the bus.

```

// Read from port A, top IC (data)

i2c.write_read(ADDR, &[GPIOA], &mut data).await.unwrap();

info!("data = {:02x}", data[0]);

// Read from port B, top IC (lower addr)

i2c.write_read(ADDR, &[GPIOB], &mut addr0).await.unwrap();

info!("addr0 = {:02x}", addr0[0]);

// Read from port A, bottom IC (top addr)

i2c.write_read(ADDR1, &[GPIOA], &mut addr1).await.unwrap();

info!("addr1 = {:02x}", addr1[0]);

```

I need to do the button functionality and the different operations associated with them like single step, examine, and deposit.

I need to tie the switches to such programming logic.

Here is the button logic I came up with using the button reference of course below, chatgpt to remind me of each button functionality, and our bus layout table

| GPIO# | Туре      | Name    | Description                     | Ownership | )   |       |

|-------|-----------|---------|---------------------------------|-----------|-----|-------|

| 4     | Control   | CLOCK   | bus clock                       | Panel     |     |       |

| 5     | Control   | ~PRESET | reset                           | Panel     |     |       |

| 6     | UI        | PANEL   | front panel data control        | Panel     |     |       |

| 7     | UI        | PROT    | memory protection               | Panel     |     |       |

| 8     | Status    | SM1     | first machine cycle of instruct | CPU       |     |       |

| 9     | Status    | SHLTA   | halt                            | CPU       |     |       |

| 10    | Status    | SSTACK  | stack operation                 | CPU       |     |       |

| 11    | DMA       | ~PHOLD  | hold bus control                |           |     |       |

| 12    | R/W       | PDBIN   | data bus in                     | CPU       |     |       |

| 13    | R/W       | SWO     | write-out                       | CPU       |     |       |

| 14    | R/W       | PWAIT   | mem/io                          | CPU       |     |       |

| 15    | I/O       | PRDY    | io ready                        |           |     |       |

| 16    | I/O       | SOUT    | output IO cycle                 | CPU       |     |       |

| 17    | I/O       | SINP    | input io cycle                  | CPU       |     |       |

| 18    | Memory    | XRDY    | memory ready                    | RAM       |     |       |

| 19    | Memory    | MWRT    | memory write strobe             | CPU       |     |       |

| 20    | Memory    | SMEMR   | memory read strobe              | CPU       |     |       |

| 21    | Interrupt | ~PINT   | interrupt request               |           |     |       |

| 22    | Interrupt | SINTA   | interrupt acknowledge           | CPU       |     |       |

| 23    | Interrupt | PINTE   | interrupt enable                | CPU       |     |       |

|       | Address   | A{15:0} | ,                               |           |     |       |

| 40-47 | Data      | D{7:0}  | tri-state                       | CPU       | RAM | Panel |

```

if (reset) {

nRst = 0;

addr = 0;

else {

nRst = 1;

if (clr) {

addr = 0;

data = hiz;

clock = clock;

else if (stop) {

clock = clock;

else if (run) {

clock = !clock;

else if (single_step) {

single_step = 1;

else if (examine) {

// read addr pins

i2c.write_read(ADDR, &[GPIOB], &mut addr0).await.unwrap();

i2c.write_read(ADDR1, &[GPIOA], &mut addr1).await.unwrap();

// flog loan word instruction over the bus

panel = 1;

// send addr

panel = 0;

```

```

else if (examine_next) {

// flog loan word with next addr

panel = 1;

panel = 0;

else if (deposit) {

panel = 1;

// read data

i2c.write_read(ADDR, &[GPIOA], &mut data).await.unwrap();

// send data sw (addr)

panel = 0;

else if (deposit_next) {

panel = 1;

// read data

i2c.write_read(ADDR, &[GPIOA], &mut data).await.unwrap();

// send data sw addr + 1

panel = 0;

}

```

I clarified with brian what the HALT and PANEL signals do on the bus. HALT is just a status flag for when the cpu reaches a halt instr. on the front panel we also trigger the halt led when that happens. PANEL is a flag asserted by the panel to indicate to the cpu and mem it wants to take control of the data lines. That way the panel can issue instructions to write to memory.

The next step is to turn this from psuedocode into actual rust code and write the PIO setup and runtime tasks to read and write to respective pins on the bus. I'll also need to figure out how to do reads and writes from the front panel too.

#### Entry 2

3/26 Wednesday 10:00-11:00 1 hour

Today I need to fix why the messages printing to console were not always the input state of the switches.

I chatgpted this and it told me that the MCP likely cycles through using a register pointer all the registers and prints the values of those instead of just the input data to the IO expander. I would need to issue a write over I2C requesting that I wanted just the data and then it would give that back to me for each iteration.

That's when I realized that I actually needed the write\_read() function as was used in the original I2C example. This function writes to the bus first and then reads a response. I replaced the blocking\_read() with this line: i2c.write\_read(ADDR, & [GPIOB], &mut portb).await.unwrap(); and it worked!

```

2.513842 INFO portb = 7c

interchange:: embassy main task::{async fn#0} @ src\main.rs:115

3.015108 INFO portb = 7c

interchange:: embassy main task::{async fn#0} @ src\main.rs:115

3.516357 INFO portb = 7c

- interchange:: embassy main task::{async fn#0} @ src\main.rs:115

4.017606 INFO portb = 7c

interchange:: embassy main task::{async_fn#0} @ src\main.rs:115

4.518852 INFO portb = 7c

interchange:: embassy main task::{async_fn#0} @ src\main.rs:115

5.020106 INFO portb = 7c

interchange::___embassy_main_task::{async_fn#0} @ src\main.rs:115

5.521363 INFO portb = 7c

interchange:: embassy main task::{async fn#0} @ src\main.rs:115

6.022610 \text{ INFO} \text{ portb} = 7e

interchange:: embassy main task::{async fn#0} @ src\main.rs:115

6.523853 INFO portb = 7e

interchange:: embassy main task::{async fn#0} @ src\main.rs:115

7.025103 INFO portb = 7e

interchange:: embassy main task::{async fn#0} @ src\main.rs:115

7.526377 TNFO porth = 7e

```

As you can see, it prints out in hex whether each switch is on or off and halfway here I flip one of the switches so the output turns from 7c to 7e.

I had some flashing issues before programming it because of a known bug so this took about 20 minutes to figure out how to get consistent flashing and running to occur. I figured out that hitting reset on the IC after you program it once and it doesn't run and then reprogramming it, causes it to successfully run the next time about 80% of the time. If that doesn't work after consecutive tries, unplugging and reconnecting the entire system to power over usb.

My next step was to continue working on the front panel code and

#### Entry 1

3/25 Tuesday 11:30-5:30 6 hours

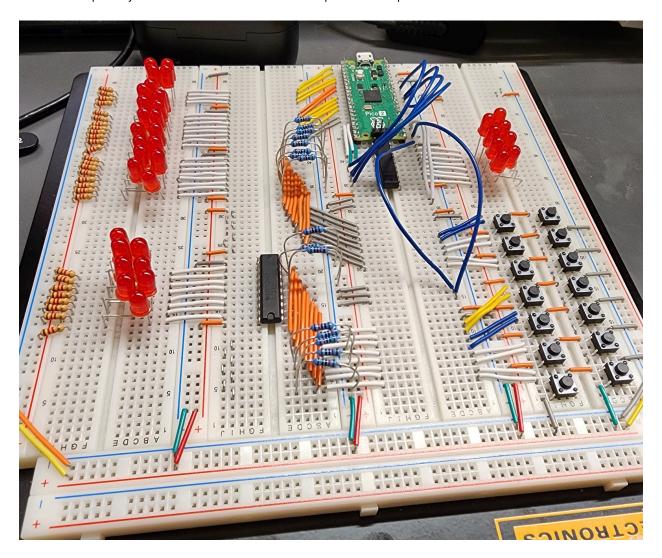

Today I wanted to get a working bus implementation working

I pulled out the bus prototyping board and I realized I needed debug LEDs. I could add them to the bus board, however we already had the front panel breadboard done, so I thought, oh i could just code that right now since the front panel code needs to be done at some point too.

I looked at the board and pulled up the datasheets for the 2 boards

https://www.ti.com/lit/ds/symlink/tlc59211.pdf?

ts=1742960394353&ref\_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FTLC59211

https://ww1.microchip.com/downloads/aemDocuments/documents/APID/ProductDocuments/DataSheets/MCP23017-Data-Sheet-DS20001952.pdf

I verified all the pin connections and learned the power, data, and addrs pins on the io expanders

I noticed some of the ICs nathan hadn't connected the power yet. I added the wiring for those

I then added the power and ground wires from the pico to the board rails

I then power the pico up over USB and the board LEDs lit up.

I noticed the switch LEDs were still shining

I asked brian why and he noted there weren't pull down resistors and that the switch inputs leading to the LEDs were in a floating state.

I added 10k pullup resistors (the ones in the middle below) and the weird LED behavior went away.

And here is a partially disassembled view of the final setup of the front panel breadboard:

However, I realized that the LEDs in this configuration are directly conected to the switch inputs and are not individual inputs like they are on our production board. Additionally, getting this breadboard to be able to connect with our other dual-stamp bus breadboard so I could use the LEDs as bus debugging LEDs was going to basically be impossible because I had already used up all the GPIO pins on the raspi pico. I could have used our third stamp which had more pins to replace the pico and then bridged that over, however that would take a lot of work rewiring.

Instead I opted for a more concise solution where we would move all the switches, buttons, and LEDs of the front panel, to just the main bus breadboard and have one of the two stamps act as the microcontroller for the front panel, and the other act as both the cpu and the memory. This would consolidate all of our testing down to one breadboard and be much simpler to wire than adding a third stamp.

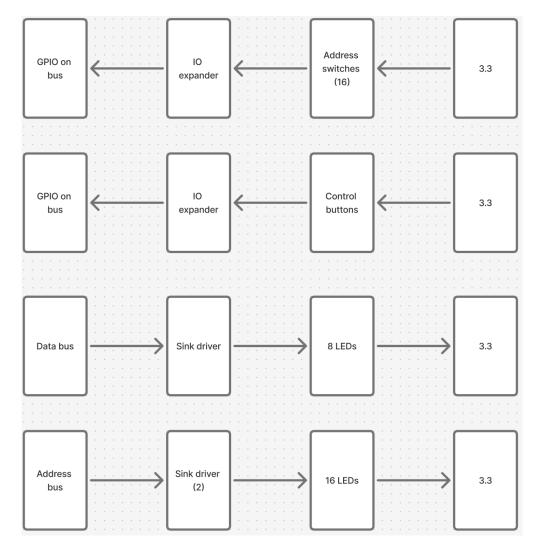

First I investigated how I was going to route this. I pulled up the schematic for the current front panel and noted all of the connections again using the highlight nets tool.

Here is one such connections (highlighted pink):

I then made a schematic in Figjam to plan the the ordering and all of the stages, just to verify they would all fit on the breadboard:

Now that I knew I had enough pins to put all the IO Expanders and sink drivers on one row, and the switches, buttons, and LEDs on another, I placed them there:

I then began routing the rest of the board.

I figured out all 24 LEDs weren't going to fit in the second column cause the switch arrays each took up 2 extra pins, so I moved the data LEDs to next to the bus on the second row.

I then placed the address LEDs at the bottom in the 4th row, moved the switches down next to them, and then placed the buttons. This had enough room so it worked perfectly.

I then began wiring up the LEDs to the sink drivers, the sink drivers to the bus, the buttons and switches to the IO expanders, and the IO expanders to the bus. We are using 2 interrupt pins on one of the io expanders, so I added those to directly to the stamp board because we needed to reserve enough pins for the other simulated bus signals.

Finally I routed the power and checked all the wiring.

Here is the final wiring:

I plugged it in and it appeared nothing was smoking!

I didn't notice any LEDs were on but this was expected since none of the GPIO pins were being driven.

I wanted to get the LEDs working so first I programmed a blinky program to light up the LED on pin 47. It worked. Pin 47 linked to the data LED on the far upper left of the board as shown above. It blinked, however, it was very dim. I wasn't sure why it was very dim vs. the first board where the LEDs lit up more strongly. Maybe more current drained on the bus pins?

Anyways, the LEDs/bus GPIO outputs were confirmed to be working, so I then moved onto confirming the switches and buttons worked as inputs.

I needed to figure out how I2C worked again and what messages were transferred on our MCP23017.

I used chatgpt for this to give me a quick overview of I2C again and I looked at the IC datasheet to learn that the MCP broadcasts the values of its registers over I2C.

I then needed an I2C example from our HAL library, embassy, and <u>I found one</u>. Luckily, the example actually was personally made for the MCP23017 and I could use the code immediately. I realized the original code used read\_write() functions and I thought these weren't necessary for basic reads, so I replaced them with blocking\_read().

I also realized from the datasheet that the MCP doesn't have pull down resistors. only pull up. So I needed to reroute all switches and buttons to ground instead of 3.3 which I had them before.

Here is the first iteration of testing code with these changes:

```

use mcp23017::*;

info!("init mcp23017 config for IxpandO");

// init - a inputs, b inputs

i2c.write(ADDR, &[IODIRA, 0xff]).await.unwrap(); // all inputs

i2c.write(ADDR, &[IODIRB, 0xff]).await.unwrap(); // all inputs

i2c.write(ADDR, &[GPPUA, 0xff]).await.unwrap(); // pull up inputs

i2c.write(ADDR, &[GPPUB, 0xff]).await.unwrap(); // pull up inputs

loop {

let mut porta = [0];

let mut portb = [0];

// Read from port A (buttons)

//i2c.blocking_read(ADDR, &mut porta).unwrap();

//info!("porta = {:02x}", porta[0]);

// Read from port B (switches)

i2c.blocking_read(ADDR, &mut portb).unwrap();

info!("portb = {:02x}", portb[0]);

Timer::after_millis(500).await;

}

```

I then built and flashed this program to the stamp and it began to run.

I noticed though that as it was running, it wasn't always outputting the value of one of the switch arrays after the portb line. it only did it like every 7 meesages like here:

```

2.012589 INFO portb = 7c

_____embassy_main_task::{async_fn#0} @ src\main.rs:115

```

I had run out of time for the day so I saved fixing this issue for tomorrow.

## Week 9

## Entry 2

3/13 Thursday

10pm-1:30am

3.5 hours

Today I needed to figure out if we were going to keep the Brian designated/non-essential pin order for the cards/dimm and route more difficult, or maybe switch their positioning up based on what pin order the card is in.

As you can see, the pin order for the front panel is not organized very well. The data and address pins are not next to each other. This was to make routing on the front panel easier

Meanwhile the pin functionality order was organized for the cards:

So first, I needed to learn if the PIO pins do need to be next to each other to send data over the bus. I looked up how to send parallel bus signals using PIO since I couldn't find any Embassy examples that did that. I found this <u>Raspi forum post</u> showing how to do it. They just needed to add the line

pio\_sm\_set\_consecutive\_pindirs(pio, sm, 0, 8, true);

This gave me some indication that you can only setup output pins that are consecutive.

Then I confirmed that setting consecutive pins was the only way to set out pins for the Embassy rust package (the one we're using) and this <u>was correct</u>:

```

v pub fn set_out_pins(&mut self, pins: &[&Pin<'d, PIO>])

Sets the range of pins affected by OUT instructions. The range must be consecutive. Out pins must configured as outputs using

StateMachine::set_pin_dirs to be effective.

```

So if the pins need to be next to each other for the card and moving them around in SW would be bad, then it would make sense to keep their ordering and route them criss cross to the corresponding backplane/ffc connector pins.

Nathan took over backplane routing from here so he did the criss-cross layout of the traces based on their assigned functionality:

Since Brian was cleaning up the front panel, the card was done, and Nathan was working on the back, I decided to get started researching how much our PCB order was going to cost.

I exported our card PCB as gerber files and went to JLC PCB's website.

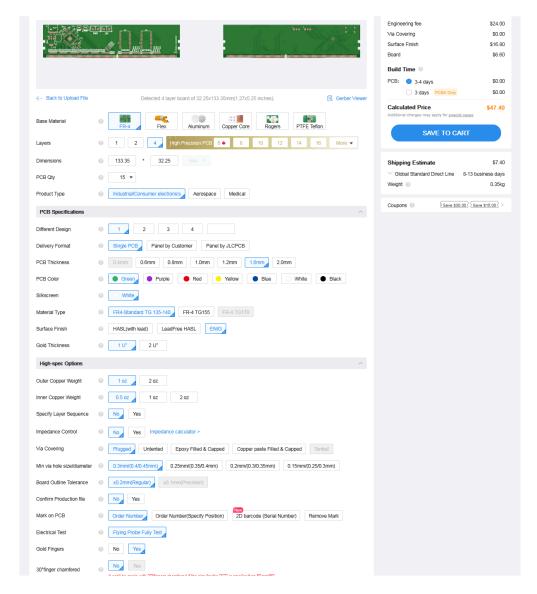

Our PCB was processed successfully and here is the configuration chosen:

We need about 15 cards 3 cards x 4 machines. And we also needed Gold fingers for our edge DIMM connectors. Finally we need ENIG surface finish since only that is comptible with gold fingers. This came out to be \$47.

Then we needed to have JLC do assembly as well because that's the only way we can get our microcontroller on the board. I clicked on the assembly tab and it requested a BOM and placement file. I exported the BOM from kicad from the fabrication outputs but I was unsure how to get the placements. I thought location from fabrication output would be good, however, it failed to upload.

I then googled how to get this placements file and i came across the JLC PCB kicad extension <u>Fabrication Toolkit</u>. This makes it easy for you to export all the files needed for JLC so I downloaded it and used it and the placement file it generated worked. I then saw all the parts that JLC had and proceeded and got my final assembly cost.

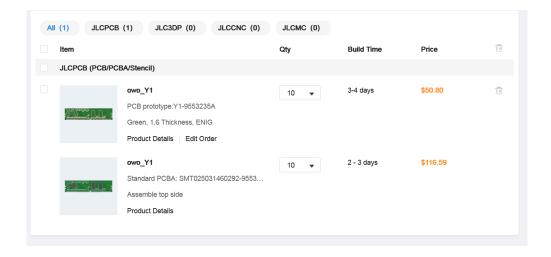

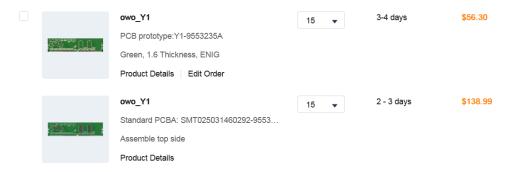

For 10 cards:

For 15:

As you can see, there's not much difference when you scale. The assembly price was quite a lot.

If we were to get 10 cards, that would be around \$170 and <u>our enclosures</u> which also are a large cost that we already know are \$39 each, would come out to \$160 for 4. That is \$330 spent with only \$280 left for the 5 front panel cards and the 5 back panel. It maybe should be enought? The front panel has a lot of components though so I'm a bit concerned. I will wait and see how much those are calculated as since I am going to bed now. Brian and Nathan will calculate them in the morning before the order them. This gives us a good idea now though on what we can and can't order and where we could cut costs.

As for me, my next steps is to get going on the software over break. I have brought home our development breadboards so I can work on sw over break. I will need to complete tram over break to stay on schedule. I'd also like to do cycle (CPU) and interconnect (front panel) since then I won't have to do work on the week after break. I have a good understanding of PIO and how output works now that I know how the consecutive pin output assigning works for a parallel bus so I am confident i can get a bus implementation with state machines working quickly.

# Entry 1

3/12 Wednesday

8pm-2am

6 hours

Today I first talked with Caleb about how our software stack is going to work.

```

+ roun on regions 1 ( (addr , dayla)

WRITE

men [addr] = data

```

I made the diagram above to explain that retreiving instructions from memory takes actually 3 clock cycles and that tram would handle doing memory reads and the CPU firmware would not worry about that. That si why tram is its own package. As you can see, I also wrote some psudocode on how we could use async/await, callback functions and event listeners to create onRequest and sendRequest functions for tram and then exec intructions for exec. This helped me better understand the software stack and I copied this psuedocode in a new frm over to our tram repo and got started on it.

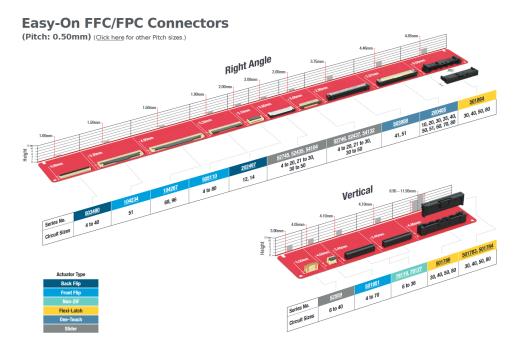

Next I went back to working on our backplane since I realized that we need to add the connector that will link the front panel with the back panel. The connector will not be a DIMM connector. I knew it was going to be a ribbon cable. I learned Nathan had previously chosen and FFC connector for the front panel, so I looked at the <u>datasheet</u> for that to get a better idea of how it works. I also googled/chatgpted what the difference between an FFC and FPC connector/cable is since the datasheet uses both terms. FPC is like a printed circuit in the cable so we only care for FFC type ribbon cables.

I also inquired Nathan why he chose this connector since it is quite large. I learned that we need an 80 pin connector for all our bus signals and Molex only makes 80 pin connectors that are in this size. We also needed a vertical FFC connector and Molex only makes them in this formfactor too.

I found this Molex product guide and it shows all their connector types

As you can see, the larest is the only vertical one that supports that many pins. and has a nice clip.

Now that the connector was confirmed, I needed to find a compatible cable for it. I noticed on the datasheet it said the connector was compatible with a certain type of jacket. I didn't know what a jacket was so I looked that up and it is a plastic housing that protects cables that goes on the outside of an FFC cable. Here were the Jackets that were compatible with our connector:

#### Use with Part(s)

| Description                                                 | Part Number |  |  |  |

|-------------------------------------------------------------|-------------|--|--|--|

| 0.50mm Pitch FFC-to-Board Plug<br>Jacket, 80 Circuits       | 5017838009  |  |  |  |

| 0.50mm Pitch FFC-to-Board Plug<br>Jacket Cover, 80 Circuits | 5017848009  |  |  |  |

I chose the <u>783 varient</u> and found its part on digikey. Then I just needed the cable.

I tried using Molex's website to find compatible cables, however, they didn't have a filter for finding cables based on compatible connectors so I was very lost. Until, I went to digikey's website! When I pulled up the <u>Digikey</u> page for our connector, there was a compatible parts section at the bottom that showed which cables were compatible:

Here were all the varients! In the future, I now know I should probably search for parts using distributor websites since they are going to be the ones I'll be buying the product from in the end and they have better filters as well. I just didn't know they sold these as I struggled to find them in the first place.

The cables were all different sizes. We only need a small ribbon cable. Unfortunately the 2 in ones were sold out so I selected the <u>4 inch</u> one.

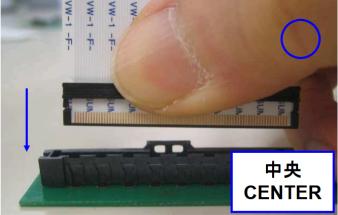

Next I need to figure out what the cable looked like and how it was inserted, just to make sure how it was going to work with the jacket and such. I found the <u>product specification</u> from Molex for the connector and inside of it, it shows the jacket and how the cable is oriented inside of the jacket:

When mating the connector, hold the JACKET AND JACKET COVER together at either a whole or the center portion of them to insert.

With this knowledge, I now know that we need to orient our connectors for the frontplane and backplane to match which way the ribbon will be pointing so that the connectors are on the right side. The cable only has connectors on one side so this is why it is important.

I placed the connector in our PCB layout for routing later:

I also learned from brian how to import the 3D model for it from digikey because it originally wasn't showing up in the 3D view for the backplane. Now it does:

Ok, now that the FFC connector is sorted, I also realized that a power switch was missing from the backplane. This needs to be a vertical power switch that will show through a cutout on the front panel. To fin this part, I simply looked for in-stock vertical 2 way switches on Digikey. Here is the cheapest option I found and it fits our needs:

I needed the 3D model for this and footprint so I learned how to get to digikey's footprints page and import it into kicad:

I then added it to the schematic:

And inserted it into the layout where it needs to go on the left side of our backplane:

The final thing to do was to route the FFC connector to the DIMM slots. Only thing was that Brian was still working on the pin assignments for the front panel and which order they were going to be for the front panel connector, so I waited a bit.

Brian finished, however I realized that the pin order does matter for the front panel but for the cards/DIMMS it does not. We can change the pin functionality in sofwtare.

So I thought, maybe it would be easy then to route them like this:

But I wasn't so sure. Because maybe the card pin order *does matter* because the PIO pins need to be next to each other. I wasn't sure because I hadn't done my own programming in PIO yet so I waited for next morning to figure out what to do about this.

# Week 8

# Entry 1

3/4 Tuesday

10:30pm-10am

11.5 hours

Today we needed to finish all the pcb layouts and insert them into our presentation that was for the next day.

I realized that we had not started on our backplan PCB schematic and layout so I took to getting that done while my teammates worked on the other PCBs and slides.

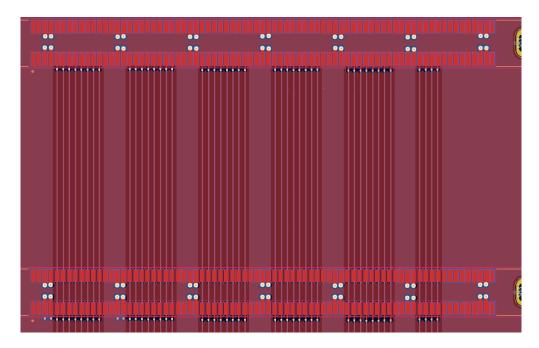

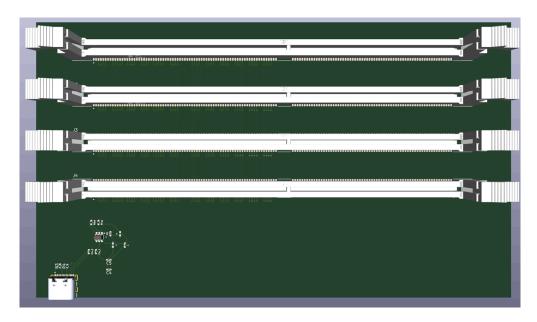

First I needed to figure out how I was going to do the schematic for the dimm slots. Here is what I assigned them nets.

I then copied this 4 times. We chose SMD Dim slots as they can be more easily routed for a bus than through hole ones as I learned from an earlier layout experiment.

Then I went to PCB layout for the bus.

I routed them in the below fashion where bus signals are viaed to the bottom layer and all share a bottom copper strip. Power and ground which are after every block of signal pins, get zone-linked either for the front layer (for power) or through vias to the back layer (for ground).

As I did this, Brian showed me how to use KiCad. I learned all the key shortcuts, how to import new footprints and models, how to set a custom grid, and how to make zones.

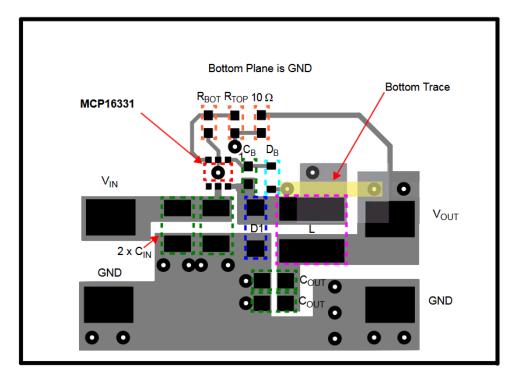

After laying out the DIMM slots, I proceeded to research the buck converter and recommended layout to place on the backplane.

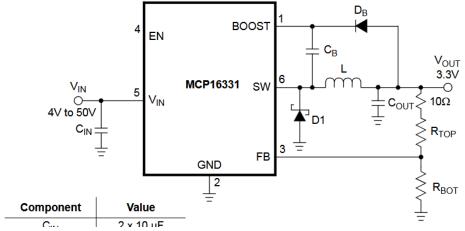

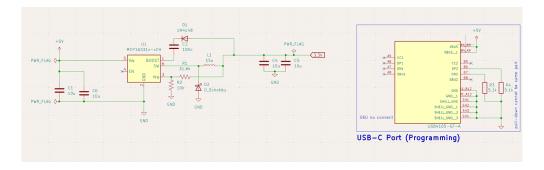

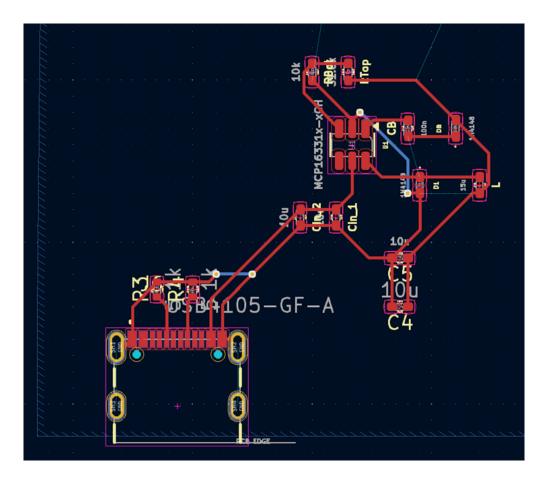

I found the docs <u>here</u> and I followed the schematic and layout given on page 22 for the 500 mA design. Here was the reference:

And here was my implementation with the USB C port as well

I then verified everything looked good in the 3D model

Now that the backplane first prototype was done, I switched back to researching software since we needed a bit more for our slides

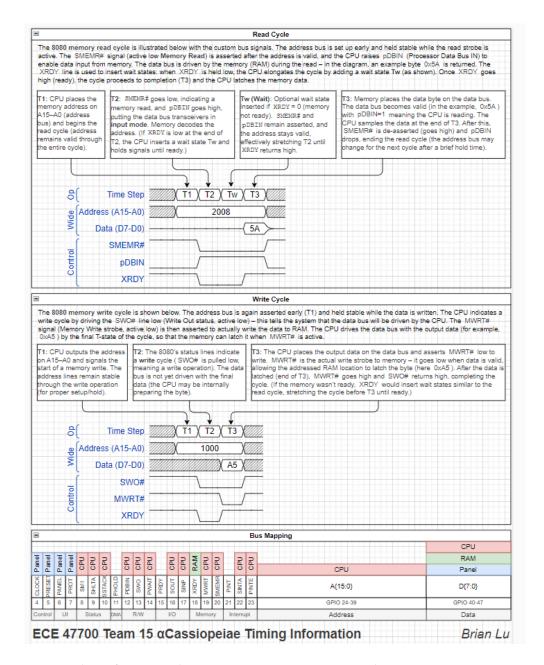

Brian made a document highlighting how our bus read and write transactions are going to work so i reviewed that:

This gave me a better idea of what bus signals are relevant to memory operations

I then added this info to our presentation and also listed all the memory communication transactions that would need to be made between the CPU, memory, and front panel.

As part of realizing the front panel needs to communicate over the bus as well, I talked and learned from brian that whenever data is written to memory from the panel input, the panel itself needs to send over 3 cycles to complete a full write machine cycle. This is why our front panel needs a microprocessor and why it's not always a reflection of the bus and the switches alone cannot handle writing to memory.

After I learned this, I was curious how the deposit (write) and examine (read) process worked so I rewatched this video explaining how the altair 8800 is programmed again. This got me familiar with the examine and examine next switches and how to operate the whole thing so I now know how to better implement the software. I documented my findings about how a full bus transaction works on our slide like this:

#### Clock always running

Single step just triggers a flip flop to have the pc attach to the main clock.

Examine sends a <u>imp</u> instruction (<u>imp</u>, upper, lower)

- 1. Flip On switch (deliver power to all PCBs, microcontrollers start, set front panel = stop, CPU pc = 0)

- 2. Program first instruction

- 1. First byte

- 1. You're already in data mode. Flip the switches to change the data line. Lights do not change

- 2. Hit deposit. Data lights should change to switch values.

- 2. Second byte